\*RELATÓRIO TÉCNICO\*

UM ESTUDO DOS PROBLEMAS DE

PROJETO DE MATRIZES DE PORTAS

COM TECNOLOGIA CMOS

Alexandre Malheiros Meslin

Gabriel Pereira da Silva

Gerson Bronstein

Sidney de Castro Oliveira

Eber Assis Schmitz

NCE-30/90

Novembro/90

Universidade Federal do Rio de Janeiro

Núcleo de Computação Eletrônica

Caixa Postal 2324

20001 - Rio de Janeiro - RJ

BRASIL

UNIVERSIDADE FEDERAL DO RIO DE JANEIRO

NUCLEO DE COMPUTACAO ELETRONICA

# UM ESTUDO DOS PROBLEMAS DE PROJETO DE MATRIZES DE PORTAS COM TECNOLOGIA CMOS

## RESUMO

Este trabalho abrange desde aspectos ligados às características da célula básica, até os problemas da estrutura geral da matriz. São avaliados os parâmetros para dimensionamento e espaçamento dos dispositivos da matriz básica, além dos problemas elétricos de projeto. É feita uma análise dos principais tipos de circuitos de periferia, com apresentação dos resultados de simulação. Finalmente, os resultados obtidos na engenharia reversa de uma matriz de portas são também apresentados.

## A STUDY OF THE CMOS GATE ARRAYS DESIGN PROBLEMS

## ABSTRACT

This work discusses the aspects related to the basic cell features, and the problems of general array structure. The basic array sizing and spacing parameters, and eletrical design problems are evaluated. An analysis of some peripheral circuits, with simulation results, is done. Finally, the results of a gate array reversal engineering are also shown.

## ÍNDICE

|                                                      |    |

|------------------------------------------------------|----|

| 1. Introdução                                        | 1  |

| 2. Tipos de Matrizes de Portas                       |    |

| 2.1 - Introdução                                     | 3  |

| 2.2 - Matriz de Portas com Canal                     | 3  |

| 2.3 - Matriz de Portas sem Canal                     | 7  |

| 3. Célula Básica                                     |    |

| 3.1 - Parâmetros de Projeto                          | 11 |

| 3.2 - Célula para Matrizes Com Canal                 | 15 |

| 3.3 - Células para Matrizes Sem Canal                | 20 |

| 3.4 - Outros tipos de Células                        | 25 |

| 4. Dimensionamento do Canal                          |    |

| 4.1 - Introdução                                     | 26 |

| 4.2 - Tipos de Canal                                 | 26 |

| 4.3 - Cálculo da Largura do Canal                    | 29 |

| 5. Periferia                                         |    |

| 5.1 - Introdução                                     | 30 |

| 5.2 - Proteção de Entrada                            | 31 |

| 5.3 - Conversão de Nível                             | 32 |

| 5.4 - Circuitos do PAD de Saída                      | 35 |

| 5.5 - Canal para Roteamento Periférico               | 44 |

| 6. Alimentação                                       |    |

| 6.1 - Introdução                                     | 46 |

| 6.2 - Distribuição de Alimentação                    | 46 |

| 6.3 - Eletromigração e o Problema do Dimensionamento | 50 |

| 6.4 - Dissipação e Outras Considerações              | 53 |

| 7. Engenharia Reversa                                |    |

| 7.1 - Introdução                                     | 55 |

| 7.2 - Técnicas Utilizadas                            | 55 |

| 7.3 - Análise do Circuito                            | 57 |

| 8. Bibliografia                                      | 70 |

## ÍNDICE DE FIGURAS

|                                                           |    |

|-----------------------------------------------------------|----|

| 2.1 - Tipos de matrizes de portas                         | 3  |

| 2.2 - Matriz de portas com canal                          | 4  |

| 2.3 - Canal com "underpass"                               | 6  |

| 2.4 - Matriz de portas sem canal                          | 9  |

| 3.1-A - Inversor                                          | 11 |

| 3.1-B - Porta "NAND"                                      | 11 |

| 3.1-C - Porta "NOR"                                       | 11 |

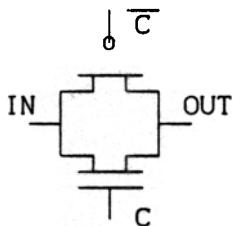

| 3.2 - Comporta de passagem                                | 12 |

| 3.3 - Inversor com saída em alta impedância               | 12 |

| 3.4 - FF "LATCH" dinâmico                                 | 13 |

| 3.5 - Parte P da célula                                   | 13 |

| 3.6 - Célula com os transistores isolados                 | 14 |

| 3.7-A - Célula com transistores e portas isoladas         | 16 |

| 3.7-B - Célula com transist. isolados e portas conectadas | 16 |

| 3.7-C - Célula com transist. conectadas e portas isoladas | 17 |

| 3.7-D - Célula com transistores e portas conectadas       | 17 |

| 3.8 - Transistores com as portas conectadas e isoladas    | 18 |

| 3.9 - Célula com os transistores desalinhados             | 19 |

| 3.10 - Transistor com área mínima                         | 19 |

| 3.11 - Transistor com fator de forma 6:2                  | 20 |

| 3.12-A - Célula com difusão contínua e porta interrompida | 21 |

| 3.12-B - Célula com difusão partida e porta interrompida  | 22 |

| 3.12-C - Célula com difusão contínua e porta conectada    | 23 |

| 3.12-D - Célula com difusão partida e porta conectada     | 24 |

| 3.13 - Transistor para uso em PLA                         | 25 |

| 4.1 - Exemplo de canal com "underpass" contínuo           | 27 |

| 4.2 - Exemplo de canal setorizado (partido)               | 27 |

| 4.3 - Exemplo de canal setorizado não alinhado            | 28 |

| 5.1 - Mod. de descarga eletrostática provocada pelo homem | 31 |

| 5.2 - Circuito de proteção de entrada                     | 32 |

| 5.3 - "Layout" da proteção de entrada                     | 32 |

| 5.4 - Esquema do conversor de nível                       | 33 |

| 5.5 - "Layout" do inversor com histerese                  | 34 |

| 5.6 - Simulação do inversor com histerese                 | 34 |

| 5.7 - "Pad" genérico                                      | 35 |

| 5.8 - Transistores de saída                               | 36 |

| 5.10 - Circuito típico de um "pad" de saída "tri-state"   | 37 |

| 5.11 - "Bufferização" com fator=3                         | 38 |

|                                                            |    |

|------------------------------------------------------------|----|

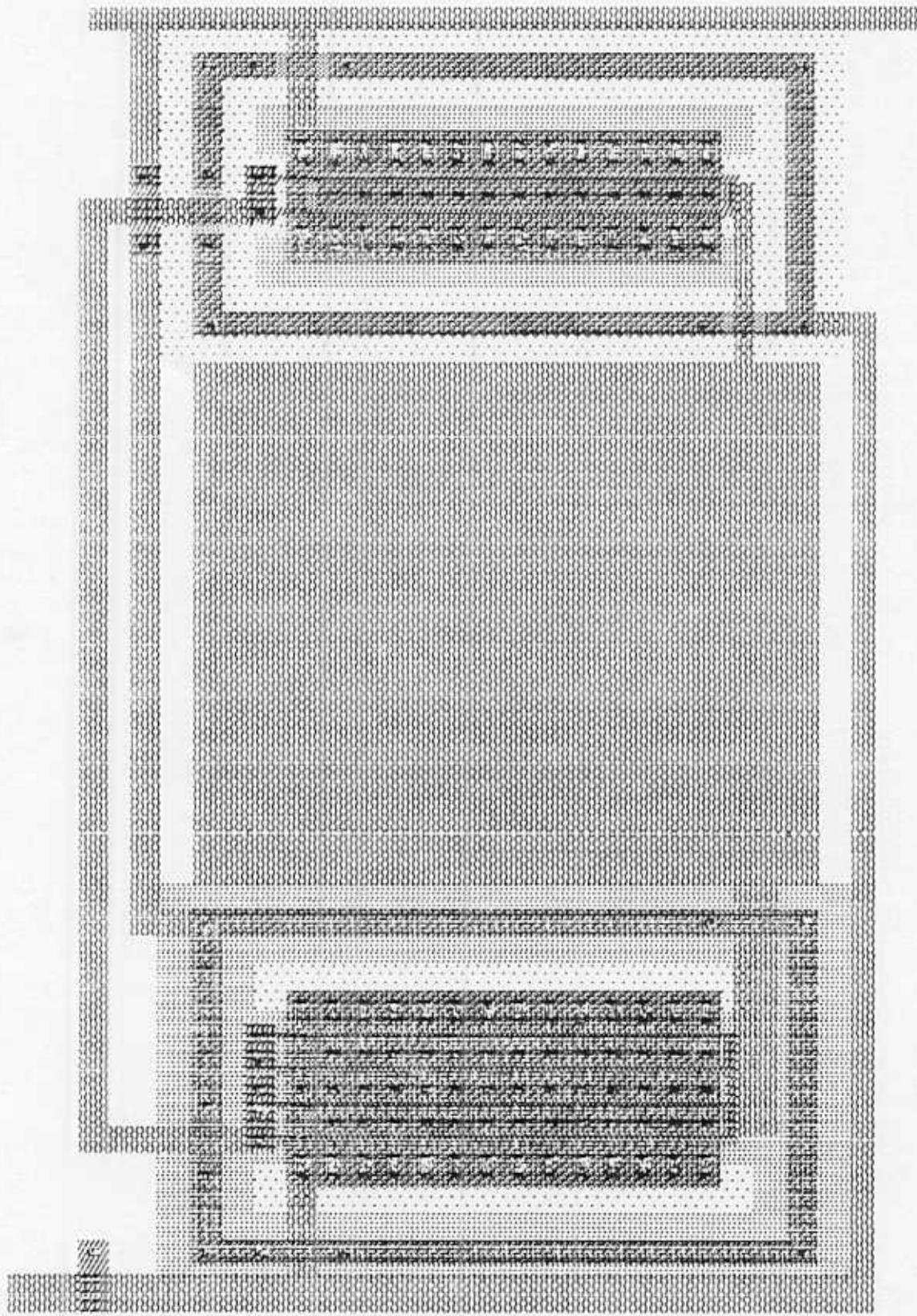

| 5.12 - "Layout" do "pad" grande                            | 39 |

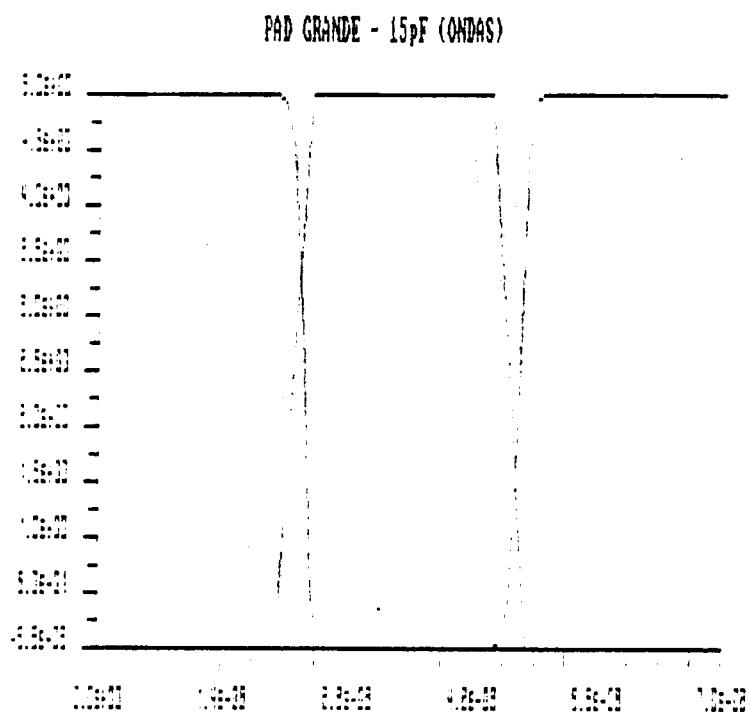

| 5.13 - Simulação do "pad" grande no ONDAS                  | 40 |

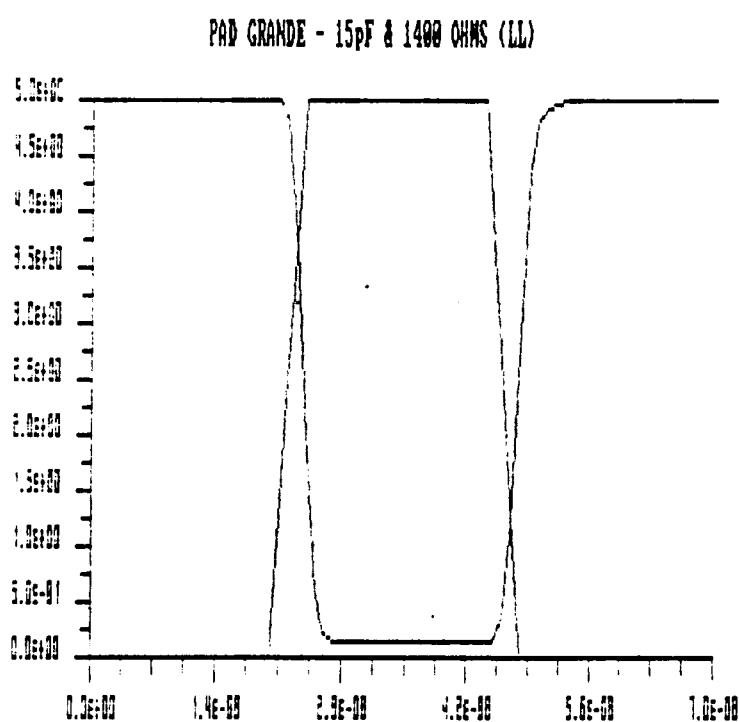

| 5.14 - Simulação do "pad" grande no SPICE - lento lento    | 40 |

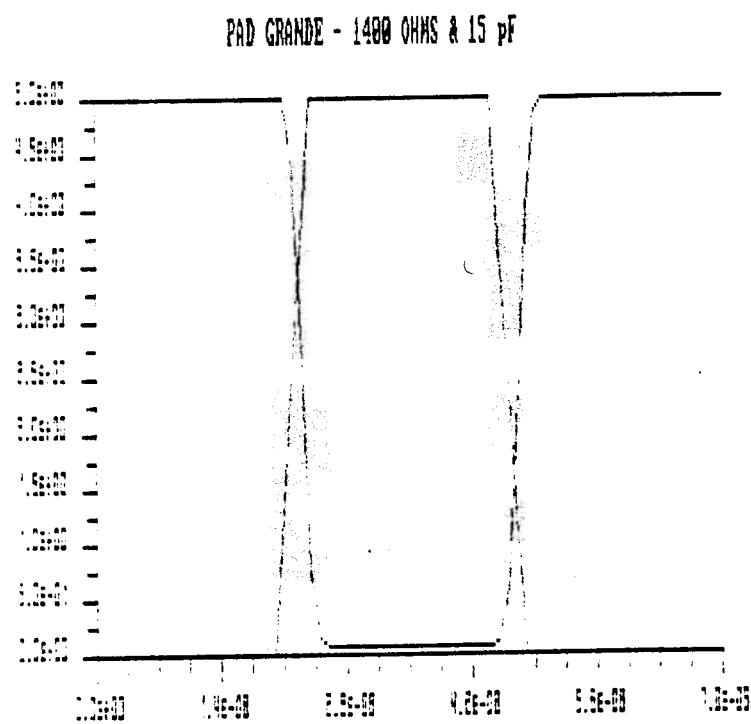

| 5.15 - Simulação do "pad" grande no SPICE - rápido rápido  | 41 |

| 5.16 - "Layout" do "pad" pequeno.                          | 42 |

| 5.17 - Simulação do "pad" pequeno no ONDAS                 | 43 |

| 5.18 - Simulação do "pad" pequeno no SPICE - lento lento   | 43 |

| 5.19 - Simulação do "pad" pequeno no SPICE - rápido rápido | 44 |

| 5.20 - Disposição do canal                                 | 45 |

| 6.1-A - Esquema de alimentação em um "buffer" inversor     | 48 |

| 6.1-B - Flutuação de tensão                                | 48 |

| 6.2 - Configuração P-N-N-P                                 | 49 |

| 6.3 - Circuito aberto causado por eletromigração           | 51 |

| 6.4 - Curto-circuito causado por eletromigração            | 51 |

| 6.5 - Célula básica                                        | 52 |

| 7.1 - Esquema da célula básica                             | 62 |

| 7.2 - Foto 1 : Planta baixa do CI                          | 63 |

| 7.3 - Foto 2 : Detalhe dos canais                          | 63 |

| 7.4 - Foto 3 : Circuito de teste                           | 64 |

| 7.5 - Foto 4 : Detalhe da periferia                        | 64 |

| 7.6 - Foto 5 : CI de referência                            | 65 |

| 7.7 - Foto 6 : Detalhe da célula básica (I)                | 65 |

| 7.8 - Foto 7 : Detalhe da célula básica (II)               | 66 |

| 7.9 - Foto 8 : Detalhe da célula básica (III)              | 66 |

| 7.10 - Foto 9 : Detalhe da periferia (I)                   | 67 |

| 7.11 - Foto 10 : Detalhe da periferia (II)                 | 67 |

| 7.12 - Foto 11 : Circuito de E/S                           | 68 |

| 7.13 - Foto 12 : Circuito de E/S                           | 68 |

## 1. INTRODUÇÃO

O amadurecimento da tecnologia de fabricação de semicondutores, no começo da década de 80, deu início a era dos circuitos integrados dedicados ("ASICS"). Estes circuitos surgiram da necessidade de integrar funções não fornecidas pelos circuitos comerciais. Entretanto, este mercado tinha dois obstáculos à sua ampliação: os altos custos de projeto e a complexidade de fabricação. Estas barreiras foram superadas com o aprimoramento das ferramentas de CAD e a introdução da matriz de portas ("gate array").

A matriz de portas é um circuito dedicado constituído basicamente de um arranjo pré-definido de portas lógicas. A personalização é feita roteando conexões entre os elementos do arranjo (células), de acordo com o projeto do usuário.

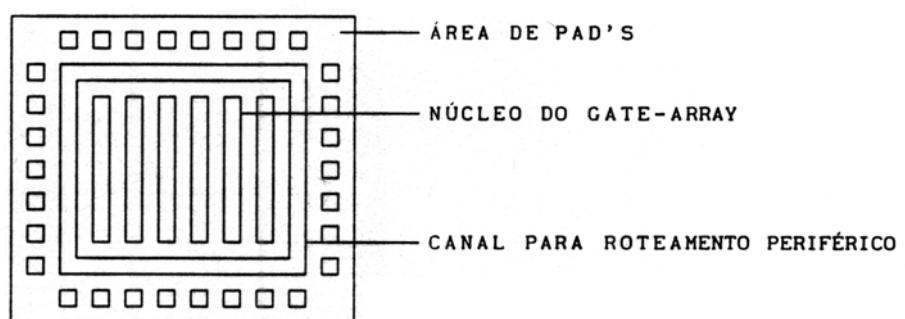

As células estão organizadas em fileiras, com ou sem canais de roteamento entre elas, constituindo o que chamamos de núcleo da matriz. Além do núcleo, a matriz possui também uma periferia, onde estão localizados os "buffers" de entrada e saída, a proteção elétrica e os conversores de nível.

A personalização da matriz é feita a nível de máscara de metal e de contatos. Inicialmente, a personalização estava restrita a um nível de contato e a um nível de metal. As matrizes mais recentes permitem a individualização em um, dois ou três níveis de metal e contato.

As principais vantagens da matriz de portas são a redução do custo de fabricação das máscaras e do tempo de projeto. Além disto, o tempo de fabricação é menor porque se requer um número menor de passos no processo. Acrescentando-se a isto o uso de ferramentas automáticas de projeto, reduziu-se significativamente o tempo de retorno de projeto.

Este trabalho apresenta um estudo dos problemas de projeto de matrizes de porta com tecnologia CMOS. Escolheu-se a tecnologia CMOS por ser dominante nas implementações comerciais destes circuitos. Suas principais características são a baixa dissipação de potência, alta velocidade e alta densidade. As várias etapas do projeto de uma matriz CMOS são aqui descritas e avaliadas, permitindo-se obter um projeto

adequado ao tipo de processo que for disponível.

O trabalho abrange desde aspectos ligados às características da célula básica (micro-arquitetura), como às da estrutura geral da matriz (macro-arquitetura). São avaliados os problemas de dimensionamento e espaçamento de todos os dispositivos da matriz, e os problemas de alimentação que são encontrados durante a elaboração de um projeto.

É feita também uma análise dos circuitos de periferia, mostrando os principais tipos, com apresentação de resultados de simulação. O trabalho termina com a apresentação dos resultados obtidos na engenharia reversa de uma matriz de portas comercial.

Finalmente, gostaríamos de agradecer a colaboração da COPPE-METALURGICA, nas pessoas do Prof. Paulo Emídio (Cascão), José Roberto (Fininho) e ao técnico Ivan; e ao INSTITUTO DE QUÍMICA, na pessoa da Prof. Zélia, pelo apoio dado na realização das fotografias do circuito integrado comercial.

## 2. TIPOS DE MATRIZES DE PORTAS

### 2.1 INTRODUÇÃO

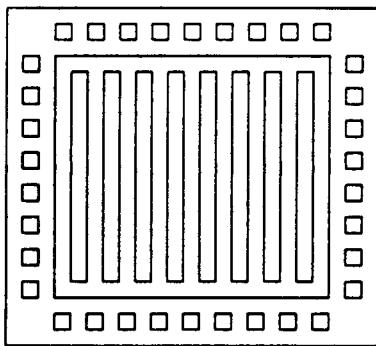

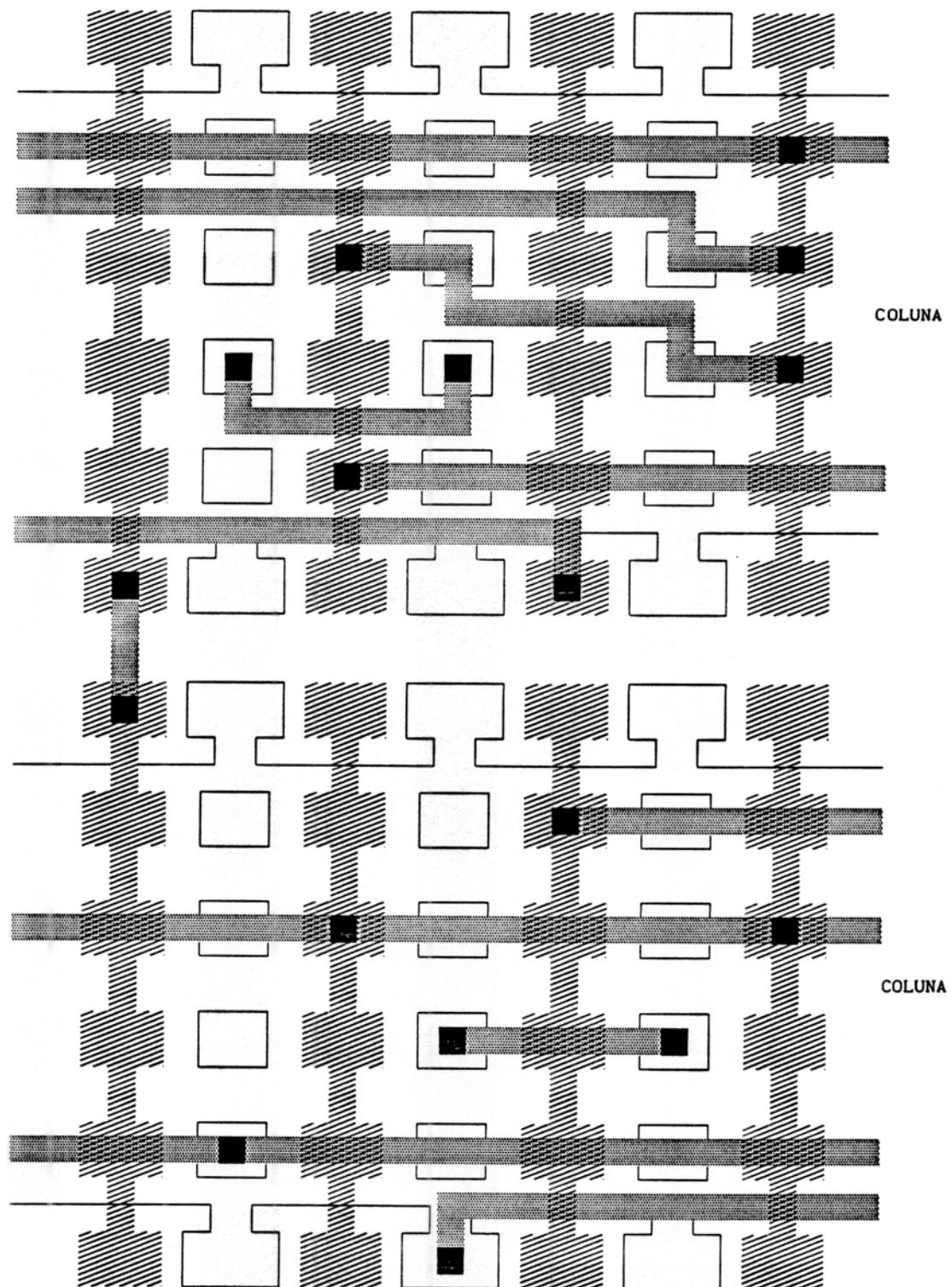

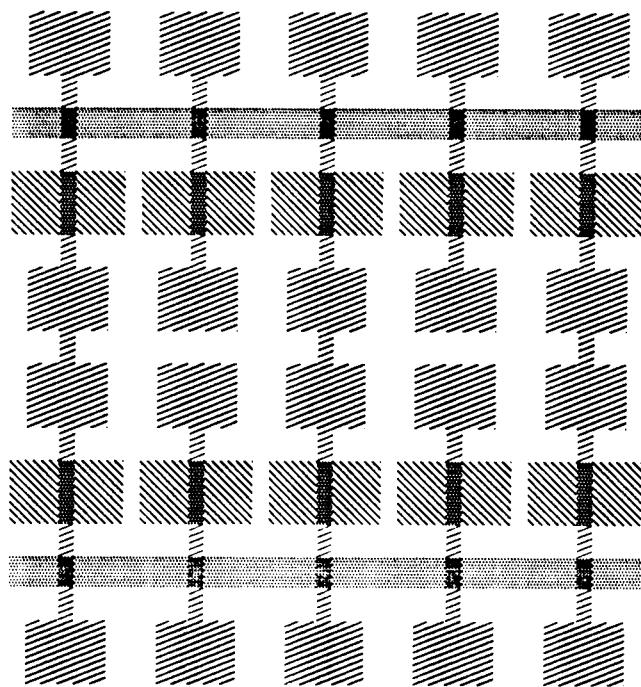

As matrizes de portas podem ser classificadas de acordo com sua estrutura interna ou macro-arquitetura. A macro-arquitetura descreve a estrutura básica da matriz de portas, isto é, como ela é formada quando duplicamos suas células básicas. Cada tipo de combinação de células básicas caracteriza um tipo diferente de macro-arquitetura. Iremos abordar dois tipos básicos<sup>1</sup> de macro- arquitetura: a com canal e a sem canal. A figura abaixo ilustra cada uma delas.

com canal

sem canal

fig. 2.1 - Tipos de matrizes de portas

### 2.2 - MATRIZ DE PORTAS COM CANAL

Este é o tipo mais tradicional de matriz de portas. Neste tipo de matriz, as células estão organizadas em fileiras chamadas de colunas. Entre cada coluna existe um espaçamento sem células pré-difundidas, chamado de canal. Este canais são destinados ao roteamento, ou seja, toda interconexão entre as células básicas é feita através dele, como mostra a figura 2.2.

<sup>1</sup>Algumas outras variações de matriz de portas podem ser encontradas como por exemplo, o tipo "Forest Gate Array" [3].

fig. 2.2 - Matriz de portas com canal

Podemos notar que existe um espaço para roteamento no interior das células. Este espaço é reservado para as interligações que definem a função da célula básica. Assim, por exemplo, podemos construir um inversor ou uma porta "nand" sem utilizar o canal.

O roteamento é feito na fase de metalização, que é a fase do processo que personaliza a matriz de portas. Pode-se utilizar um ou mais níveis

de metal para fazê-lo. Quando se utiliza apenas um nível de metal é necessário que o canal possua "underpass" em poli-silício ou difusão para permitir o roteamento na direção transversal ao canal, como mostra a figura 2.3.

fig. 2.3 - Canal com "underpass"

Contudo, este tipo de matriz de portas atingiu um limite inerente à sua macro-arquitetura. A necessidade de integração de circuitos mais complexos resultou em um número maior de interligações e, consequentemente, aumentou a largura do canal de roteamento. Este aumento de largura de canal passou a exigir maior área de silício, e levou a duas situações contraditórias:

- a) Manter o número original de células básicas, aumentando a largura do canal através do aumento da área do circuito integrado, ou

- b) Reduzir o número de colunas de células básicas, como forma de obter um canal maior sem aumentar o tamanho do circuito integrado.

As duas hipóteses não são satisfatórias. A primeira resulta em trilhas de interconexão longas, com capacidades parasitas elevadas, dificultando o projeto. A segunda provoca uma baixa utilização do circuito integrado, já que diminui o nível de integração da matriz de portas.

Por outro lado, este tipo de matriz de portas possui algumas vantagens: é de fácil realização e requer uma ferramenta de roteamento relativamente simples.

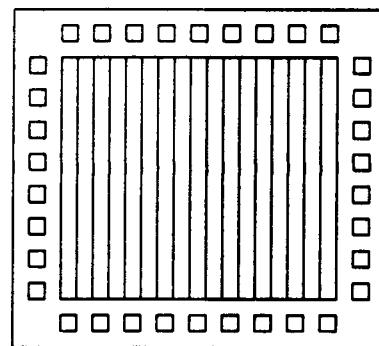

### 2.3 MATRIZ DE PORTAS SEM CANAL

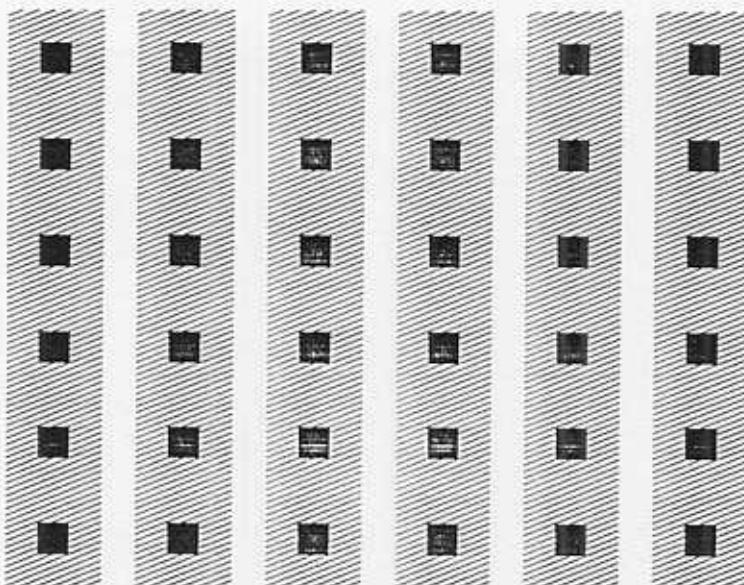

A matriz de portas sem canal foi proposta como solução para a necessidade de integrar circuitos mais complexos. Na matriz de portas sem canal ou mar-de-portas, os canais de roteamento são removidos, fazendo com que as colunas de transistores sejam posicionadas lado a lado, formando um "mar" de células ou transistores.

Em particular, circuitos altamente regulares como PLA's, RAM's e ROM's podem ser mais densamente integrados do que circuitos compostos com lógica combinacional aleatória. Isto porque podem ser construídos com células básicas específicas, com transistores de tamanhos diferentes, capacidade de interligação mais adequada e outras peculiaridades. Com este tipo de estrutura, consegue-se taxas de utilização de até 90% do

total de portas pré-difundidas [6]. A implementação dos circuitos acima, em uma estrutura com canal, resultaria em uma baixa utilização do canal.

Na matriz de portas sem canal, não há perda de espaço com canais de roteamento, ou seja, existe o maior número possível de transistores por unidade de área. O roteamento é agora realizado passando-se as interconexões sobre algumas células, ocasionando a perda de algumas delas. A figura 2.4 mostra um roteamento numa matriz de portas sem canal.

Contudo, somente a área das células efetivamente gasta para roteamento é perdida. Isto permite, na maioria dos casos, uma economia considerável de área, garantindo uma melhor utilização da matriz de portas. Deve ser notado que para permitir o roteamento, o tamanho do transistor neste tipo de estrutura é bem maior que na anterior. Consequentemente, haverá um maior fluxo de corrente elétrica, tornando crítica a questão da distribuição da alimentação.

fig. 2.4 - Matriz de portas sem canal

O uso da matriz de portas sem canal impõe algumas limitações:

- a) Com relação ao "software": como sua estrutura é mais livre, a ferramenta de CAD para roteamento deverá ser bastante flexível, resultando em uma maior complexidade.

- b) Com relação ao "hardware": a obrigatoriedade de utilização de dois níveis de metal na fase de personalização.

A necessidade da integração conjunta de circuitos altamente regulares com circuitos não regulares, leva o projetista a questionar qual o tipo de macro-arquitetura que deve ser utilizada. A escolha é condicionada à disponibilidade existente, tanto de tecnologia de fabricação, quanto de ferramentas de apoio a projeto.

### 3. CÉLULA BÁSICA

#### 3.1 PARÂMETROS DE PROJETO

No projeto de uma célula básica para uma matriz de portas, deve-se considerar que seus transistores serão interconectados através de pistas de metal. As células devem ter estruturas regulares para facilitar o processo de roteamento manual ou por computador. A seguir são apresentados os parâmetros que devem ser avaliados no projeto de uma célula básica:

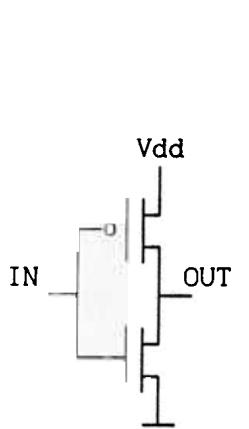

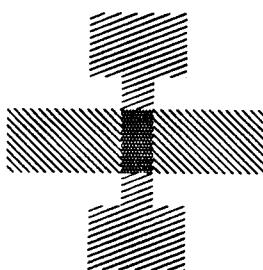

##### a) Conexão das Portas

Em uma célula básica, as portas dos seus transistores "P" e "N" podem estar conectadas ou não entre si, dependendo do processo de isolamento escolhido e da aplicação final da matriz de portas. Transistores com as portas conectadas são destinados ao projeto de lógica combinacional (entenda-se, neste caso, por lógica combinacional portas do tipo "NAND", "NOR" e inversores), que aproveita a forma simétrica e complementar dos circuitos "CMOS".

fig. 3.1-A

INVERSOR

fig. 3.1-B

NAND

fig. 3.1-C

NOR

Pode-se observar que as portas dos transistores P e N da figura 3.1 estão sempre interligadas duas a duas. Este tipo de transistor torna o desenho de elementos como o "transmission gate" (comporta de passagem) difícil de otimizar. Perde também muitos transistores por elemento,

porque necessita de sinais complementares em suas portas, conforme mostra a figura 3.2

fig. 3.2 - Comporta de passagem

Elementos com saída do tipo "tri-state" (alta impedância) também necessitam de transistores com portas isoladas.

fig. 3.3 - inverter com saída em alta impedância

Existem células que possuem transistores com portas conectadas, alternados por transistores com portas não conectadas (isoladas). Este tipo de célula serve para ser utilizado em projetos com circuitos do tipo "flip-flop" dinâmico, que são feitos de comportas de passagem e inversores, dispostos alternadamente.

fig. 3.4 - FF "latch" dinâmico

### b) Isolamento entre Transistores

Outro fator que deve ser analisado no projeto de uma célula básica é a forma pela qual deverão ser isolados os drenos/fontes de dois transistores. Como pode ser observado, através dos exemplos anteriores (fig 3.1, 3.2 e 3.3), existe um grande número de configurações que utilizam transistores em série ou em paralelo, ou seja, possuem pelo menos o dreno ou a fonte em comum. Um tipo de célula voltada para esta aplicação, teria todos os transistores com pelo menos um elemento em comum , como na figura abaixo :

fig. 3.5 - parte "P" da célula

Uma opção seria manter os transistores isolados entre si, mas com previsão de interconexão , através de uma área para um contato no

dreno/fonte. Esta segunda configuração oferece mais flexibilidade, embora ocupe mais espaço físico e necessite de uma área maior de metal.

fig. 3.6 - célula com transistores isolados

No caso de transistores com dreno ou fonte em comum, deverão existir facilidades para isolamento entre os transistores. Este isolamento poderá ser feito de duas maneiras :

- i) Eletricamente: Deixar um certo número de portas inativas, conectando-as a VDD ou VSS. Desta forma, isolando eletricamente o dreno ou fonte de dois transistores vizinhos, mas que não devam estar interconectados.

- ii) Geometricamente: Retirar, em espaços regulares, transistores, descontinuando a camada de difusão, formando grupos de transistores que realizam as funções básicas (célula básica).

Se as portas dos transistores "P" e "N" estiverem conectadas, a única forma possível de isolamento é a física. As portas não utilizadas dos transistores não devem ser deixadas em aberto para evitar que sinais espúrios induzidos (ruído) levem a um mau funcionamento do circuito.

### c) Transparência de Roteamento

Para facilitar a passagem de sinais de uma célula distante para outra,

as células básicas necessitam ter transparência em pelo menos um dos sentidos. Esta transparência existe naturalmente em tecnologias de mais de um metal. Em tecnologias com apenas um metal pode ser obtida através da inclusão de "underpass" (fio de passagem) de difusão ou, preferencialmente, de poli-silício. O fio de passagem cruza a célula perpendicularmente à direção preferencial das pistas de metal.

#### d) Alimentação

Um outro fator importante é a alimentação. Pode-se deixar espaço pré-definido entre as células para passagem das linhas de alimentação; ou os sinais de VDD e VSS podem ser roteadas junto com os outros sinais. A estrutura da célula deve estar adaptada ao esquema de distribuição de alimentação que estiver sendo utilizado.

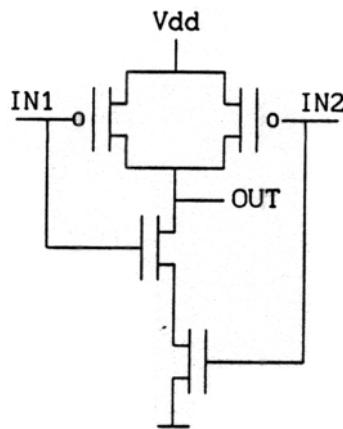

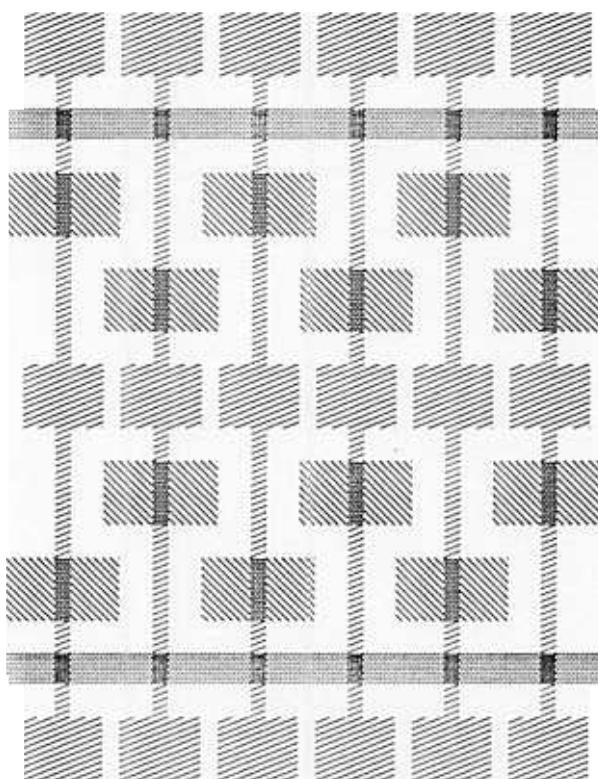

### 3.2 CÉLULAS PARA MATRIZES COM CANAL

As células básicas para macro-arquiteuras com canal podem ter tamanho menor que as células básicas de macro-arquiteturas sem canal; já que o espaço interno disponível para roteamento é apenas o suficiente para a realização das funções básicas.

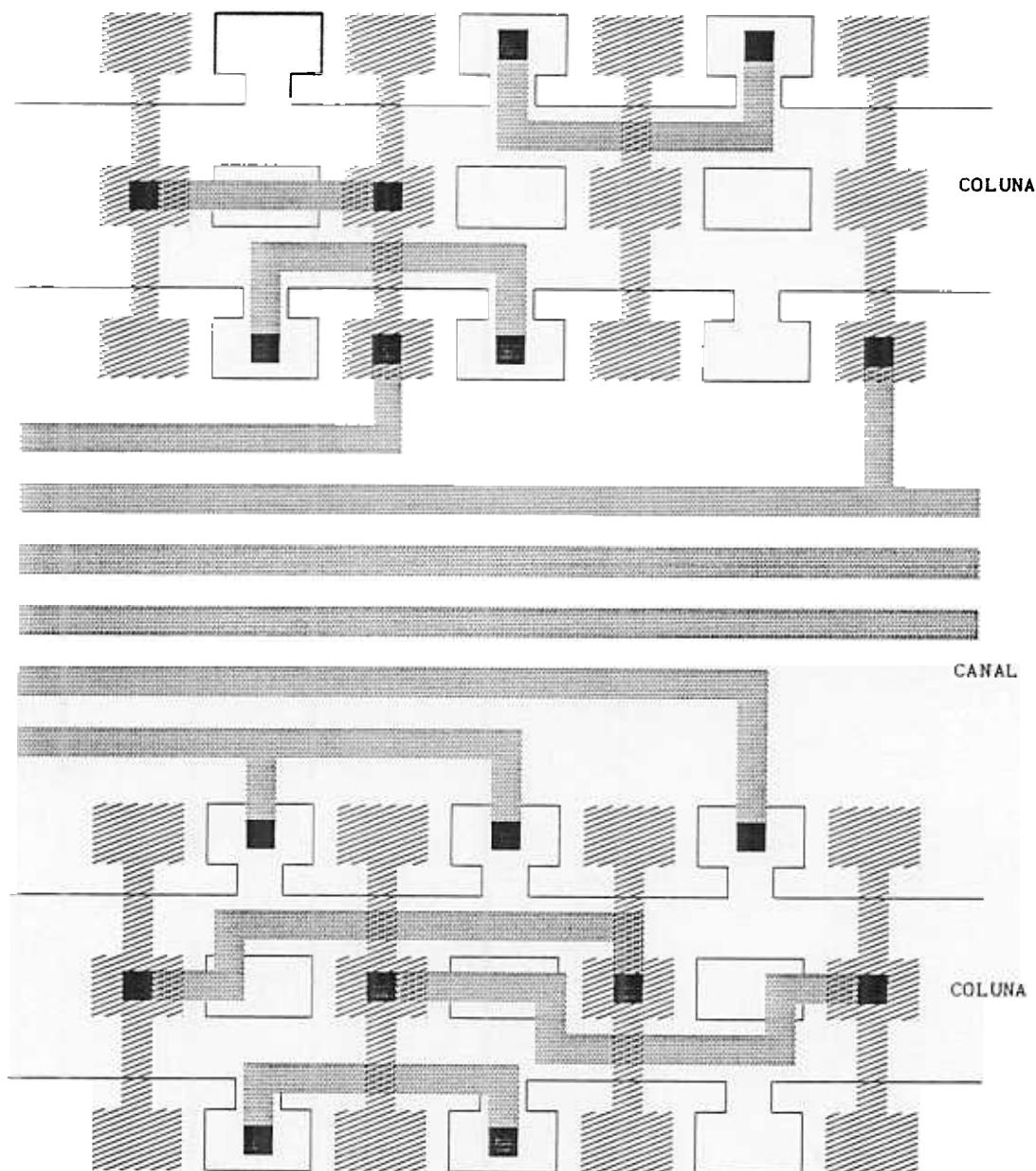

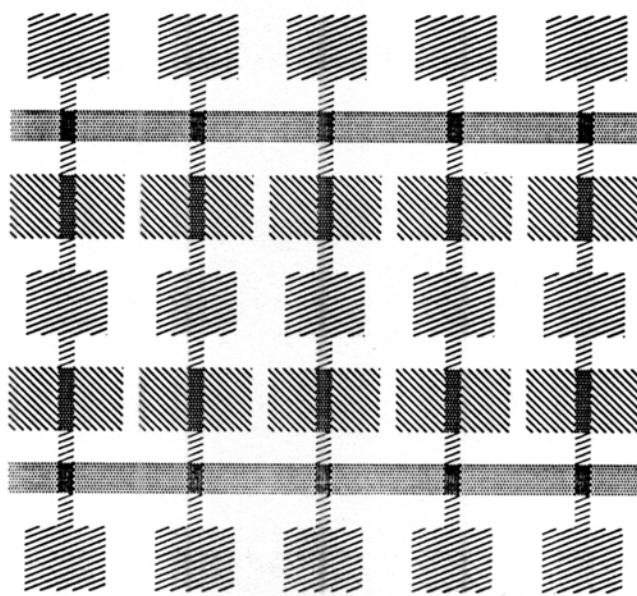

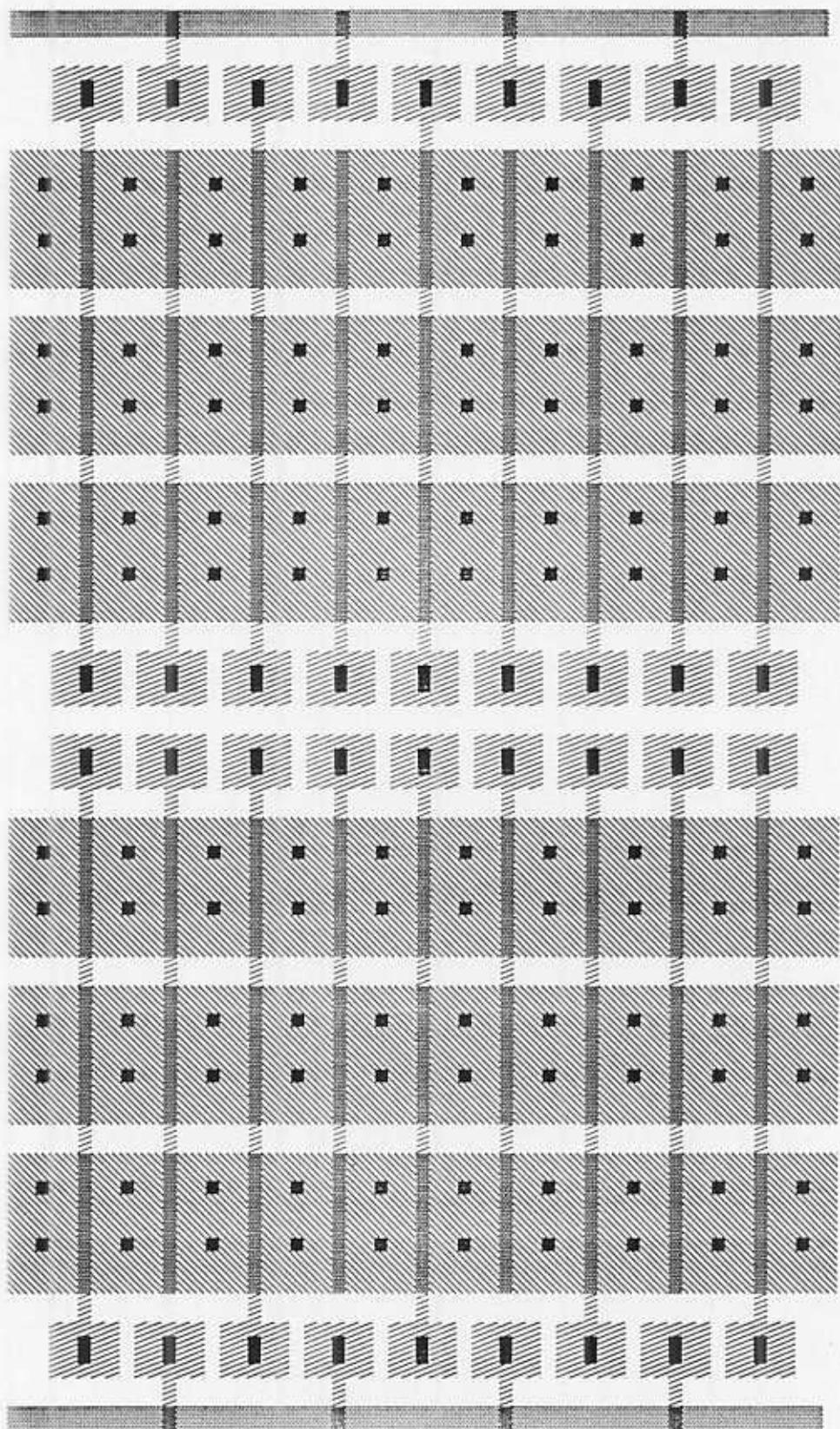

Como já foi dito anteriormente, os transistores podem ser ou conectados dois a dois ou isolados. Por sua vez, as portas dos transistores "P" e "N" também podem ser conectadas ou isoladas. Com isto, pode-se obter quatro tipos básicos de célula, acrescidas das combinações possíveis entre estes quatro tipos, conforme mostrado a seguir:

fig 3.7A Célula com transistores e portas isoladas

fig 3.7-b - Transistores isolados e portas conectadas

fig. 3.7-C - Transistores conectados e portas isoladas

fig 3.7-D - Célula com transistores e portas conectadas

A seguir vemos um exemplo de célula que é a combinação de duas células mostradas anteriormente. Esta célula possui transistores com portas isoladas e conectadas alternadamente.

fig. 3.8 - Transistores com portas conectadas e isoladas

Neste tipo de célula, as portas dos transistores não utilizados podem ser conectadas, formando um "underpass", possibilitando que um sinal externo a célula a atravesse.

Uma outra topologia baseada na célula de transistores isolados, pode ser vista na figura 3.9. Esta topologia procura diminuir a área da célula e levar o seu fator de forma para próximo de 1:1 [8].

fig. 3.9 - Célula com os transistores desalinhados

Este tipo é chamado de célula com transistores desalinhados. Uma vantagem deste tipo de célula é a existência de espaço para roteamento interno para mais de uma pista de metal.

O tamanho dos transistores é um fator importante a ser considerado no projeto da célula básica. Um transistor maior permite um circuito mais rápido, e também um número menor de células em um mesmo circuito integrado. Neste caso, o transistor pode ter uma relação de "W/L" maior , desde que não aumente o tamanho da célula. Por exemplo, utilizando-se a tecnologia CMOS mostrada em GLASSER [13], obtém-se o seguinte transistor de área mínima (incluindo área de contatos):

fig. 3.10 - Transistor com área mínima.

Este transistor possui fator de forma 3:2. Um outro transistor que ocupa a mesma área e possui fator de forma 6:2 (o dobro) pode ser obtido aproveitando-se a largura mínima para contato:

fig. 3.11 - Transistor com fator de forma 6:2

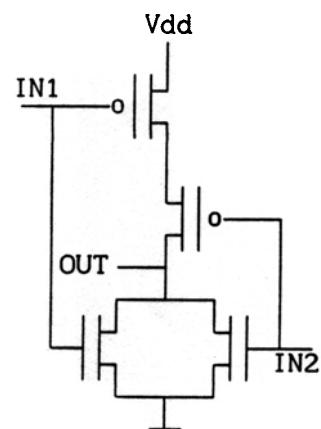

### 3.3 CÉLULAS PARA MATRIZES SEM CANAL

Este tipo de arquitetura deixa espaço para roteamento dentro da própria célula. Por esta razão, os transistores devem ser maiores que os das células com canal. Em contrapartida, não é perdida área com canais externos às células, que seriam utilizados para roteamento.

Existem vantagens e desvantagens no aumento do fator de forma:

- Vantagens:

- Aumento da velocidade de comutação dos transistores através de uma corrente de dreno maior,

- Uma capacidade maior de fornecimento de corrente.

- Desvantagens:

- Aumento do consumo de potência,

- Necessidade de pistas de alimentação mais largas.

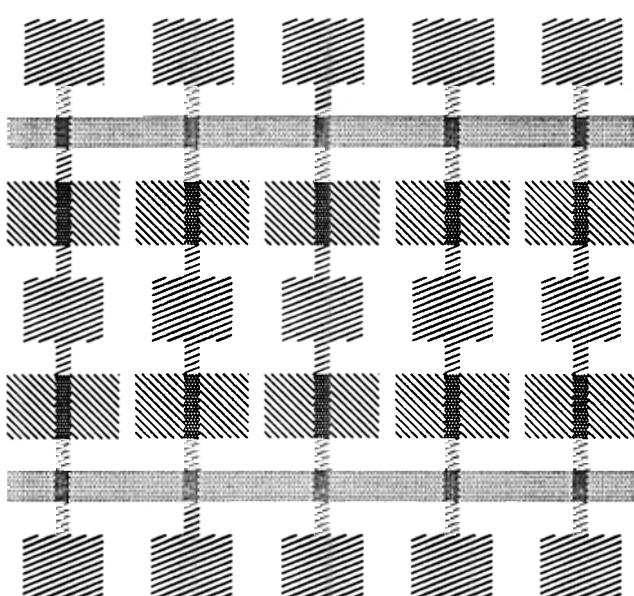

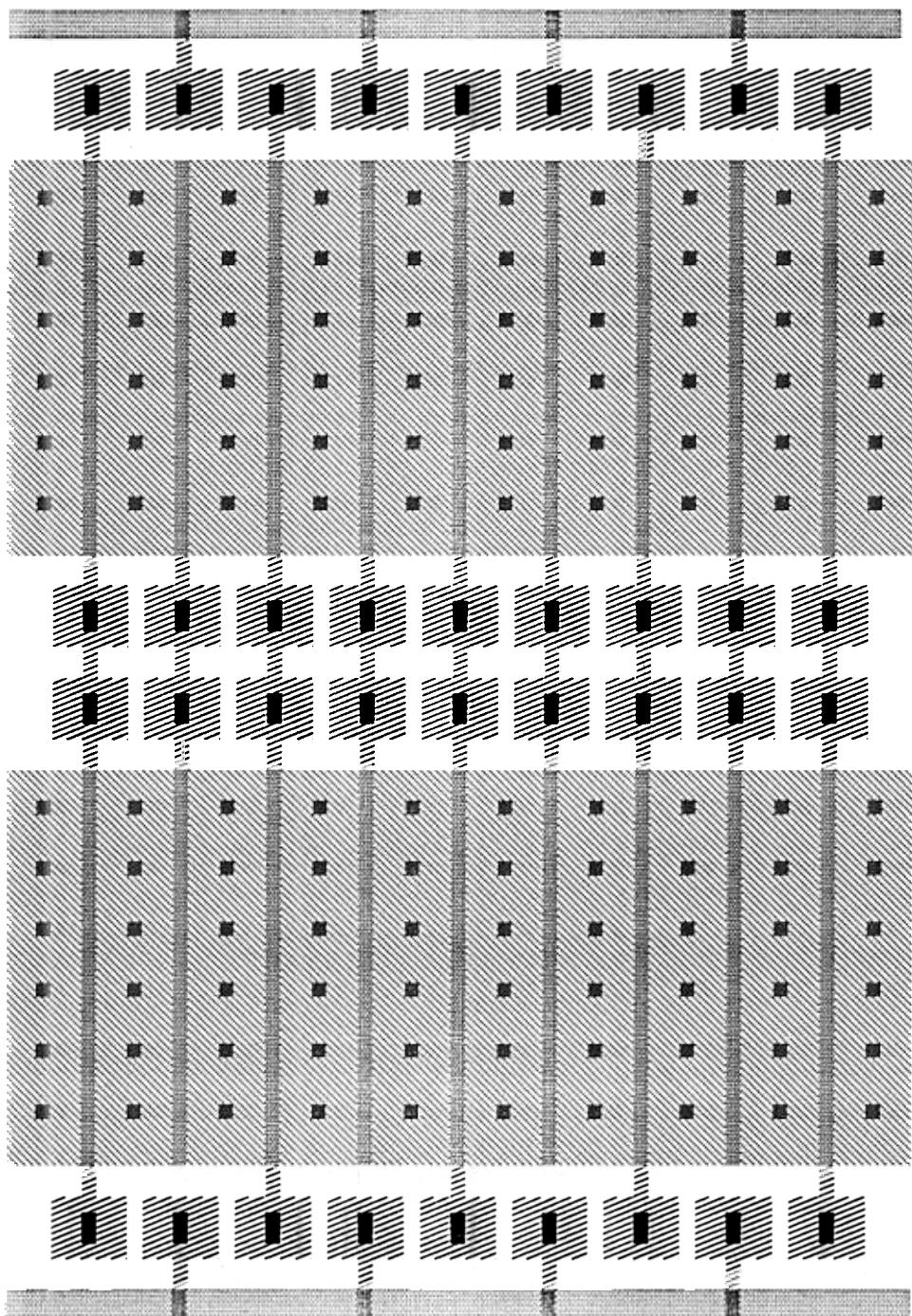

Assim como nas células que necessitam de canal externo, existem diversas formas de se implementar uma célula do tipo "mar-de-portas" com difusão contínua ou não, com as portas de poli-silício conectadas ou não. Vejamos alguns exemplos a seguir:

fig. 3.12-A - Célula com difusão contínua e porta interrompida [6]

fig. 3.12-B - Célula com difusão partida e porta interrompida

fig 3.12-C - Célula cm difusão contínua e porta conectada [3]

fig. 3.12- D - Célula com difusão partida e pora conectada

A topologia com difusão interrompida foi derivada do canal setorizado (partido) citado em [9]. Embora ocupe maior área, o roteamento se torna mais fácil, já que dois sinais podem compartilhar o mesmo canal vertical (não o mesmo sub-canal). Outra vantagem é a facilidade de se alterar o fator de forma dos transistores utilizando-se mais ou menos segmentos.

### 3.4 - OUTROS TIPOS DE CÉLULAS

Além das células para uso geral, já descritas nos itens anteriores (3.1 e 3.2), podem ser incorporadas à matriz de portas, células para uso específico em circuitos ou configurações homogêneas como RAM's, ROM's ou PLA's. Na figura 3.13 temos um exemplo de uma célula específica para PLA [3].

fig. 3.13 - Transistor para uso em PLA

Estes tipos de células podem ser utilizadas em conjunto com outras células convencionais em uma matriz de portas formando uma matriz de portas híbrida ou floresta de portas [3].

## 4 DIMENSIONAMENTO DO CANAL

### 4.1 INTRODUÇÃO

Um ponto pouco discutido na literatura técnica de microeletrônica é o tipo de canal e o seu dimensionamento. O tipo de canal de roteamento influirá principalmente na ferramenta de roteamento, que deverá aproveitar as facilidades e vencer as dificuldades oferecidas pela arquitetura do canal.

Por outro lado, a largura do canal, que é fixada durante o projeto da macro-arquitetura da matriz de portas, se for mal escolhida, pode tornar inviável projetos nesta matriz.

Se o canal for muito estreito, poderá ser impossível para o roteador executar todas as ligações dentro do circuito integrado. O caso contrário também é prejudicial, já que um canal muito largo irá diminuir a densidade de transistores dentro do circuito integrado. Ou seja, ou vai aumentar seu tamanho, ou diminuir o número de transistores dentro do mesmo. No primeiro caso, o custo associado ao aumento da área poderá encarecer o projeto a ponto de não ser economicamente viável, enquanto que no outro caso, o próprio circuito não caberia dentro da matriz de portas.

### 4.2 TIPOS DE CANAL

Para tecnologias com mais de um nível de metal, o canal pode ser apenas uma área deixada entre duas linhas de células, sem difusões ou poli-silício. A transparência ou mudança de direção de um sinal é conseguida apenas mudando-se o nível do metal, ou seja, utiliza-se o primeiro nível (primeiro metal) para conexão de sinais na horizontal e o segundo na vertical [6]. Os outros níveis de metal que existirem, podem ser utilizados para otimizar as ligações, como é feito normalmente em projetos de circuito impresso.

As tecnologias com apenas um único nível de metal tornam necessária a inclusão de uma outra camada, que pode ser difusão, ou, preferencialmente, poli-silício, por apresentar uma resistência "ohmica" menor. Esta outra camada é colocada perpendicularmente a

direção preferencial do metal no canal e são deixadas áreas para contato entre o metal e esta outra camada [9].

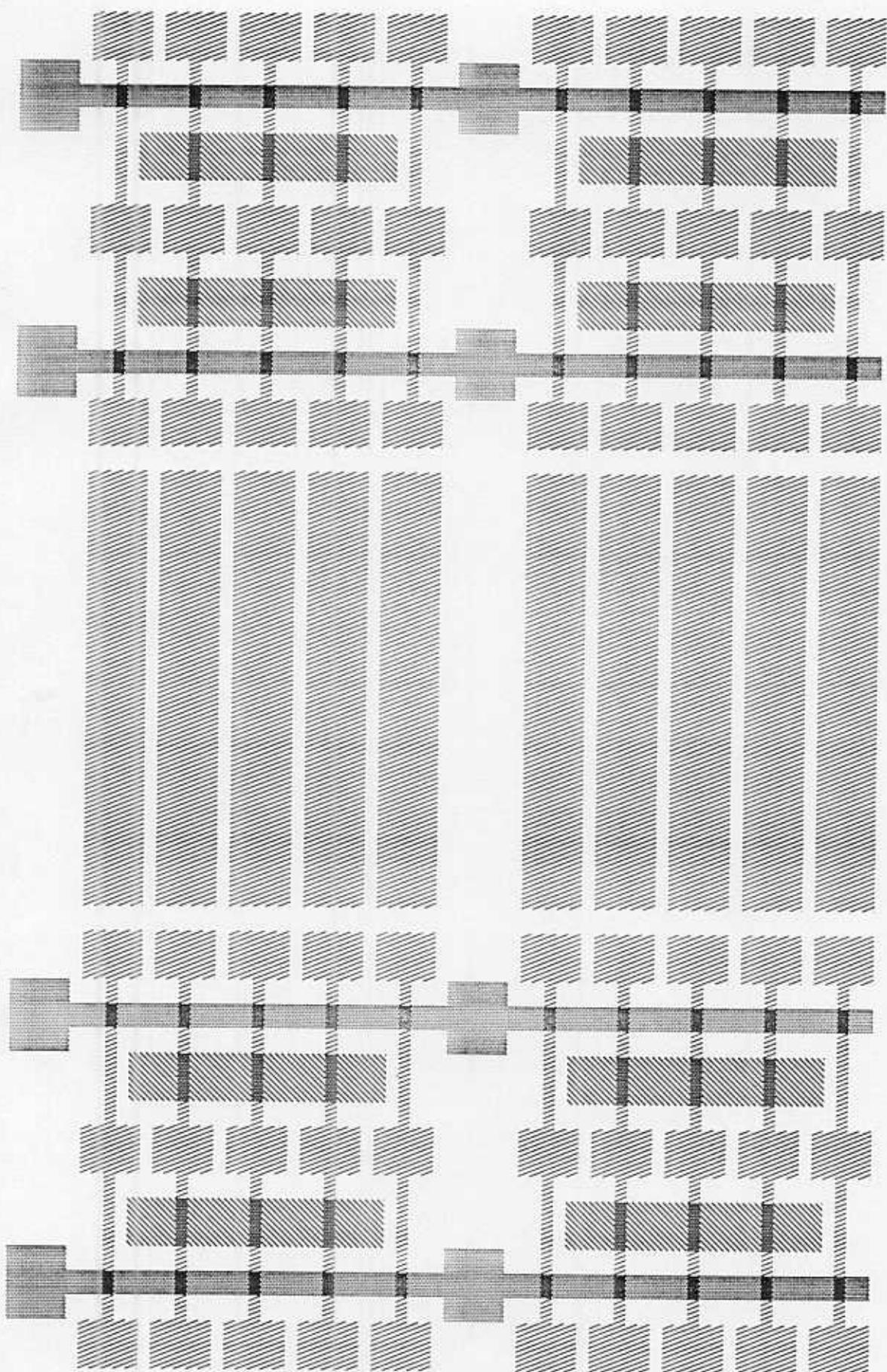

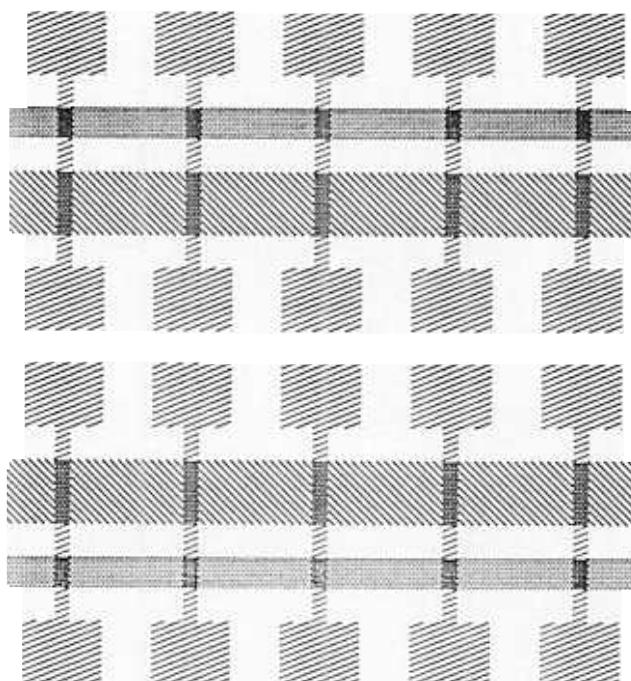

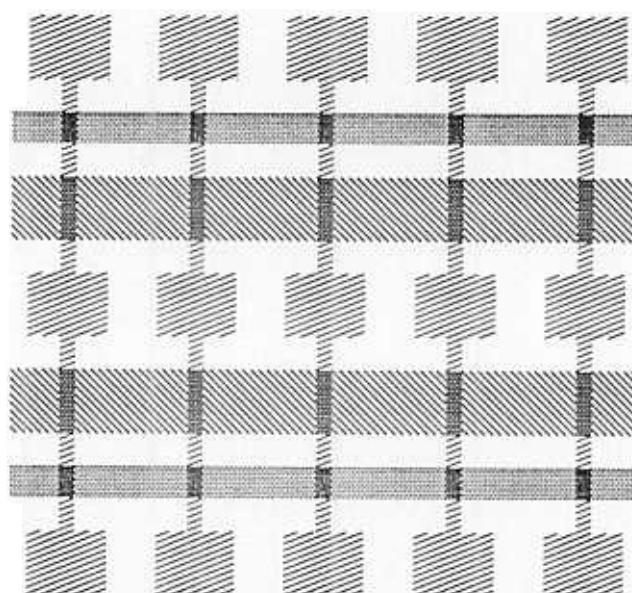

As pistas de "underpass", a exemplo das células básicas do "mar-de-portas" podem ser contínuas (figura 4.1) ou interrompidas (figura 4.2) [9], isto é, com setores ou subcanais.

fig. 4.1: exemplo de canal com "underpass" continuos.

fig. 4.2 - Exemplo de canal setorizado (partido)

Uma outra opção para canal partido seria desalinear os setores (figura 4.3) para aumentar a transparência do canal e facilitar a mudança de direção das pistas. É verdade também que o roteador precisaria ser ainda mais elaborado do que no caso do canal partido alinhado.

fig. 4.3 exemplo de canal "setorizado" não alinhado

No caso da estrutura do canal intrínseca, a escolha do tipo de "underpass" deverá levar em conta o roteador, que necessita ser mais elaborado para poder aproveitar melhor o canal setorizado. Caso o roteador seja mais simples, ou não disponha de muitos recursos, o canal com "underpass" contínuo é mais recomendado por ser de roteamento mais fácil.

Por outro lado, mesmo precisando de um roteador mais elaborado, o canal partido apresenta mais alternativas para o roteamento, tornando-o mais facilmente executável.

Pode-se observar através das figuras 4.1 e 4.2 que o canal partido apresenta uma densidade máxima de pistas de metal menor do que a do canal contínuo.

#### 4.3 CÁLCULO DA LARGURA DE CANAL

Como já foi dito anteriormente, embora o cálculo da largura do canal seja de fundamental importância para o projeto da macro arquitetura da matriz de portas, dificilmente se encontra alguma literatura a respeito do cálculo da sua largura e/ou do seu dimensionamento.

A falta de informação a este respeito se deve ao fato de não existir uma rotina para o cálculo exato do seu valor, e sim um número aproximado, que normalmente é obtido pela experiência dos fabricantes das matrizes de portas.

Os próprios fabricantes apresentam diversos tipos de matrizes de portas de forma tal que pelo menos um deles deve servir para um determinado projeto. A escolha do modelo é feita através de tentativa e erro, porém, a experiência do fabricante é fundamental para uma escolha mais ou menos acertada.

Mesmo assim, alguns parâmetros devem ser observados na escolha do tamanho do canal, como por exemplo, a largura do canal, que deve ser proporcional ao número de ligações externas às células, que por sua vez, é proporcional ao número de células existentes em uma linha e em todo o circuito integrado. É verdade também que a necessidade de mais ou menos espaço no canal será função do tipo de circuito a que se destina a matriz de portas.

Um resultado mais prático pode ser obtido simulando-se alguns circuitos reais (ou aleatórios) variando-se a largura do canal em um roteador, preferencialmente naquele em que será feito o roteamento final, até que se consiga executar o roteamento completo da grande maioria dos sinais com um tamanho mínimo de canal. Alguns valores práticos sobre o número de células e a largura de canal, podem ser encontrados no capítulo 7.

## 5. PERIFERIA

### 5.1 INTRODUÇÃO

Normalmente, os circuitos de entrada e saída não são especificados detalhadamente pelos fabricantes de ASICs, levando o projetista a utilizar circuitos previamente fornecidos como "caixas pretas". Os fabricantes optaram por esta política para manter em segredo os circuitos de proteção de entrada e o cálculo das áreas dos transistores de saída.

Antes de se projetar um circuito de E/S, deve-se escolher uma família de circuitos comerciais para se utilizar como padrão elétrico, tanto em relação aos níveis de tensão, como aos tempos de subida, descida ou propagação.

O padrão mais utilizado pelos fabricantes de matrizes de portas é o TTL. A tabela 5.1 mostra as principais características do padrão TTL. É necessário, portanto, a colocação de uma interface para compatibilizar o circuito CMOS com o padrão TTL.

Um outro fator importante é o roteamento dos sinais do núcleo das matrizes de portas para os "pads" de entrada e saída.

|                 | 7404  | 74H04 | 74L04 | 74LS04 | 74S04 |     |

|-----------------|-------|-------|-------|--------|-------|-----|

| I <sub>OH</sub> | 400   | 500   | 200   | 400    | 1000  | μA  |

| I <sub>OL</sub> | 16    | 20    | 3.6   | 8      | 20    | mA  |

| I <sub>IH</sub> | 40    | 50    | 10    | 20     | 50    | μA  |

| I <sub>IL</sub> | 1.6   | 2     | 0.18  | 0.4    | -     | mA  |

| C <sub>L</sub>  | 15    | 25    | 50    | 15     | 15/50 | pF  |

| R <sub>L</sub>  | 400   | 280   | 4000  | 2000   | 280   | ohm |

| FANOUT          | 10/10 | 10/10 | 20/20 | 20/50  | 20/-  |     |

| t <sub>P</sub>  | 10    | 6     | 33    | 9.5    | 3     | ns  |

Capacitância TTL: 10 pF → T<sub>r</sub> = T<sub>f</sub> = 15 ns (R<sub>L</sub> = 2400 Ω)

50 pF → T<sub>r</sub> = T<sub>f</sub> = 37 ns (R<sub>L</sub> = 2400 Ω)

Tabela 5.1 - Principais características do padrão TTL

## 5.2 PROTEÇÃO DE ENTRADA

Nos circuitos VLSI, as tensões envolvidas são da ordem de alguns volts (5, 9 ou 12 V) normalmente. Mas não se pode garantir que estes limites serão sempre obedecidos. Na interface com o circuito integrado, as tensões produzidas por descargas eletrostáticas podem chegar a dezenas, ou mesmo centenas de vezes este valor.

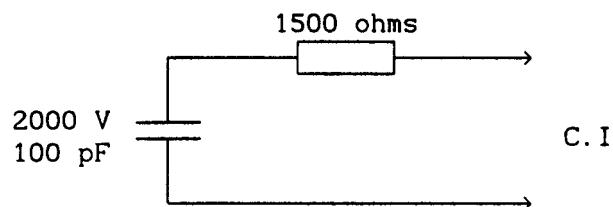

Os circuitos de proteção de entrada evitam que estas tensões danifiquem o circuito integrado. A figura 5.1 mostra um modelo para a descarga eletrostática provocada pelo homem [13].

Um circuito MOS pode ser danificado por uma descarga estática de várias maneiras. O modo mais usual é pela destruição da camada de óxido de silício da porta do transistor, devido ao campo elétrico excessivamente alto. Por exemplo, o campo elétrico máximo que o óxido de silício suporta é  $7 \times 10^6$  V/cm. Então, a máxima tensão que pode ser aplicada a porta é de apenas 21 volts [13].

fig. 5.1 - Modelo de descarga eletrostática

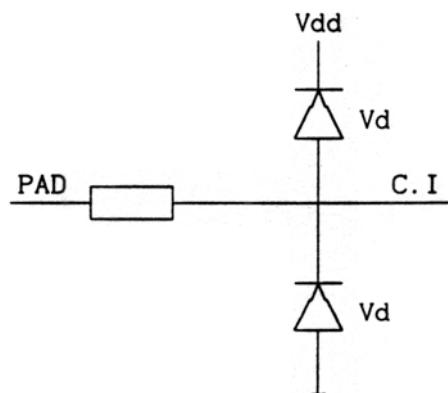

O circuito de proteção mais popular consiste em um resistor de poli-silício e 2 diodos que "grampeam" a tensão de entrada entre Vss - Vd e Vdd + Vd. O principal problema deste circuito está no dimensionamento dos diodos, que devem suportar uma corrente de pico muito alta. A figura 5.2 mostra o esquema do circuito de proteção e a figura 5.3 mostra o "layout".

fig. 5.2 - Esquema da Proteção de entrada

fig 5.3 - "Layout" da proteção de entrada

### 5.3 CONVERSÃO DE NÍVEL

Em algumas situações é necessária a ligação de circuitos integrados de diferentes tecnologias, por exemplo, CMOS, NMOS, TTL, ECL, etc. Cada uma destas tecnologias possui parâmetros elétricos próprios, como nível de "1", nível de "0", correntes de entrada e saída, etc. No caso específico dos níveis de tensão, é necessária a introdução de um elemento de interface para a compatibilização dos mesmos. No presente

trabalho, o problema se resume à compatibilização das tecnologias CMOS e TTL. CMOS, por ser a tecnologia aqui utilizada e TTL, por ainda ser a tecnologia mais utilizada. A conversão de nível se torna mais importante quando se pensa na potência consumida. No caso de lógica CMOS, há apenas o consumo de potência dinâmica, durante a transição dos sinais. Se fosse aplicado um sinal TTL a um circuito CMOS, os níveis de tensão TTL colocariam os transistores CMOS na região linear (nem saturados, nem cortados), ocasionando um consumo de potência estática também.

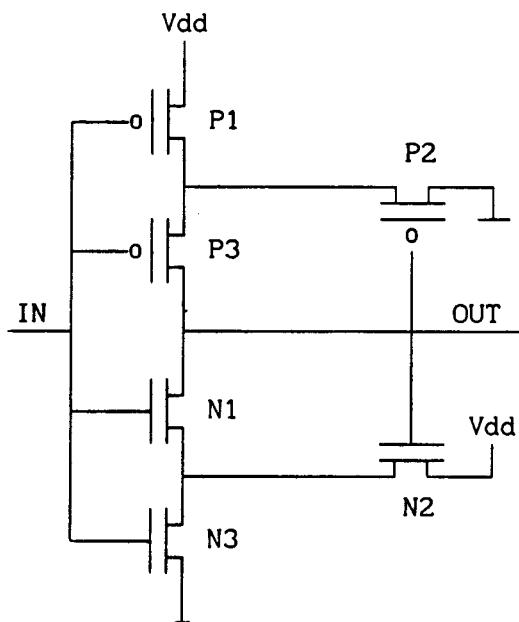

Existem algumas formas de se implementar um conversor de nível [11], [13], porém uma forma bastante atraente é utilizar um comparador com histerese (Schmitt trigger), pois além da conversão de nível, ele também melhora os tempos de subida e descida do sinal.

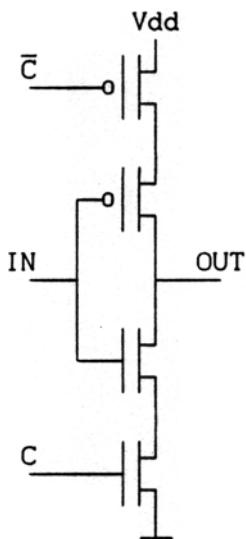

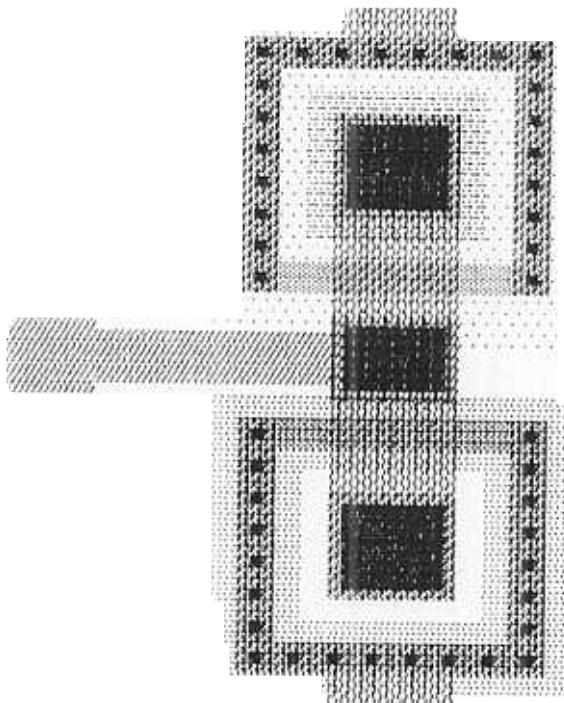

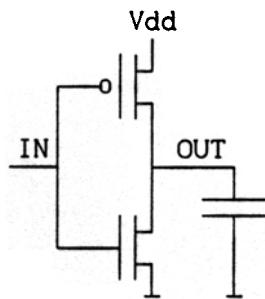

Um comparador com histerese possui 2 níveis de referência: V<sub>1</sub> e V<sub>2</sub>. Colocando V<sub>1</sub> = V<sub>OL</sub> TTL e V<sub>2</sub> = V<sub>OH</sub> TTL, temos um conversor de nível TTL ---> CMOS. Um circuito prático que implementa um inversor com histerese é mostrado na fig. 5.4 e o "layout" deste circuito na fig. 5.5

fig. 5.4 - Esquema do conversor de nível

fig. 5.5 - "Layout" do inversor com histerese

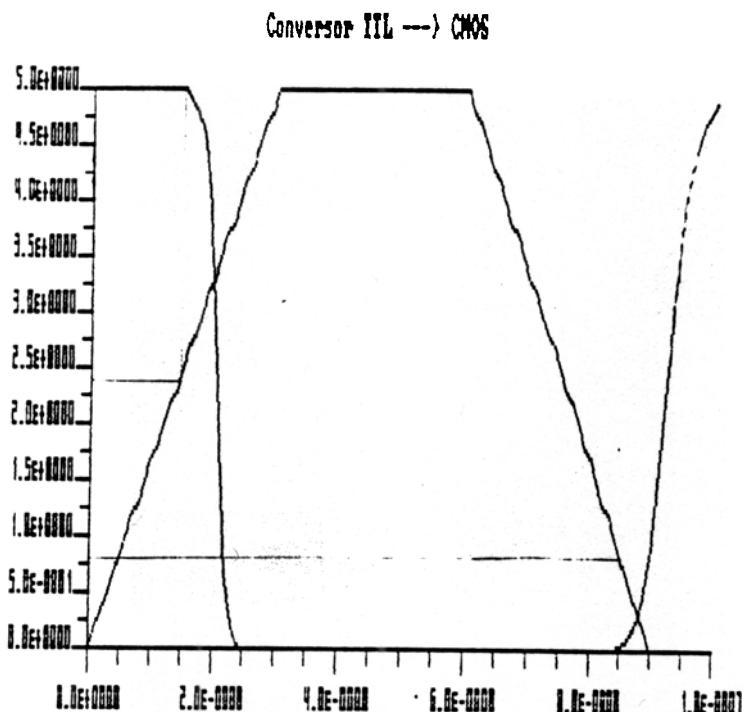

Alterando a relação entre os tamanhos de P1 e P3, altera-se o valor de V2 e alterando a relação entre N1 e N3, altera-se o valor de V1. A simulação do circuito da fig. 5.5 é mostrada na fig. 5.6.

fig 5.6 - Simulação do conversor de nível

## 5.4 CIRCUITOS DO PAD DE SAÍDA

Os "pads" de saída de um circuito integrado ocupam uma grande área na periferia do circuito. Isto é explicado pelo tamanho dos transistores que excitam o "pad" e pela necessidade de uma área grande de metal para efetuar a soldagem.

O tamanho desses transistores pode chegar facilmente a alguns milímetros de largura. Neste caso, a resistência de poli-silício e difusão é extremamente crítica. A resistência de poli-silício é minimizada fragmentando a porta do transistor em segmentos curtos e paralelos. Já a resistência de difusão é mantida baixa sobrepondo-a com metal e realizando vários contatos com a difusão.

A matriz de portas é um circuito de uso geral. Para mantê-lo flexível não devemos adotar padrões rígidos em relação aos "pads". Assim, todos os "pads" devem ser bidirecionais, se comportando como entrada ou saída dependendo da utilização. Esta definição deve ser feita na metalização.

Outros padrões de saída como dreno aberto e alta impedância devem ser factíveis. Para o dreno aberto, basta não interligar, na metalização, os transistores P e N que excitam o "pad". Já a saída em alta impedância não é tão simples, pois requer uma lógica complementar capaz de cortar estes dois transistores.

A figura a seguir mostra um "pad" genérico, podendo ser uma entrada ou uma saída com facilidades de dreno aberto e alta impedância conforme escolha feita na metalização [11].

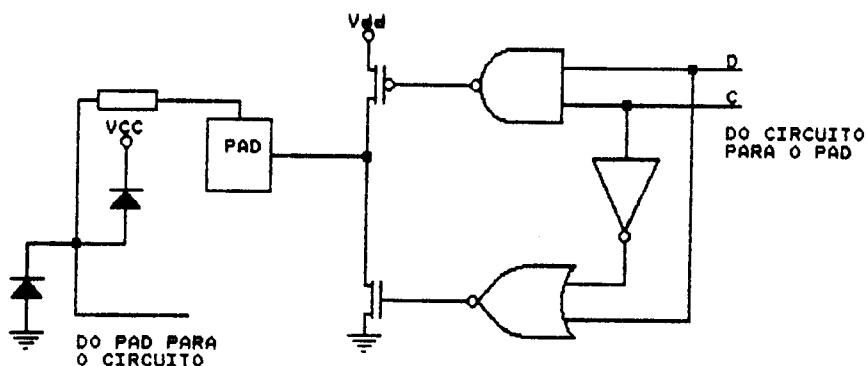

fig. 5.7 - "Pad" genérico

A questão fundamental no projeto do "pad" de saída é a determinação do tamanho dos transistores P e N de saída. Este tamanho é função direta da carga que o "pad" será capaz de excitar.

Neste trabalho consideramos um "fanout" de duas cargas TTL normais ou 1400 ohms e 15pF como padrão de saída.

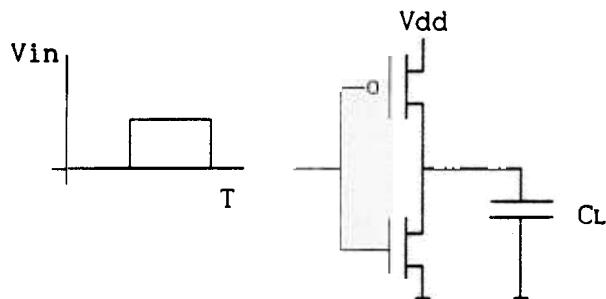

fig. 5.8 - Transistores de saída

Considere a figura acima. Segundo Weste [11], o tempo de descida pode ser aproximado pela equação:

$$t_d = 4 \cdot \frac{C_L}{K_n \cdot V_{dd}} \quad \text{onde} \quad K_n' = K_n \cdot (W_n/L_n)$$

Pelas regras de processo utilizadas [11], o parâmetro  $K_n'$  varia entre  $35 \times 10^{-6}$  e  $50 \times 10^{-6}$ . Considerando o pior caso, para se ter um tempo de descida inferior a 5ns temos:

$$W_n/L_n = 4 \cdot \frac{15 \times 10^{-12}}{(35 \times 10^{-6}) \cdot (5 \times 10^{-9}) \cdot 5} = 68$$

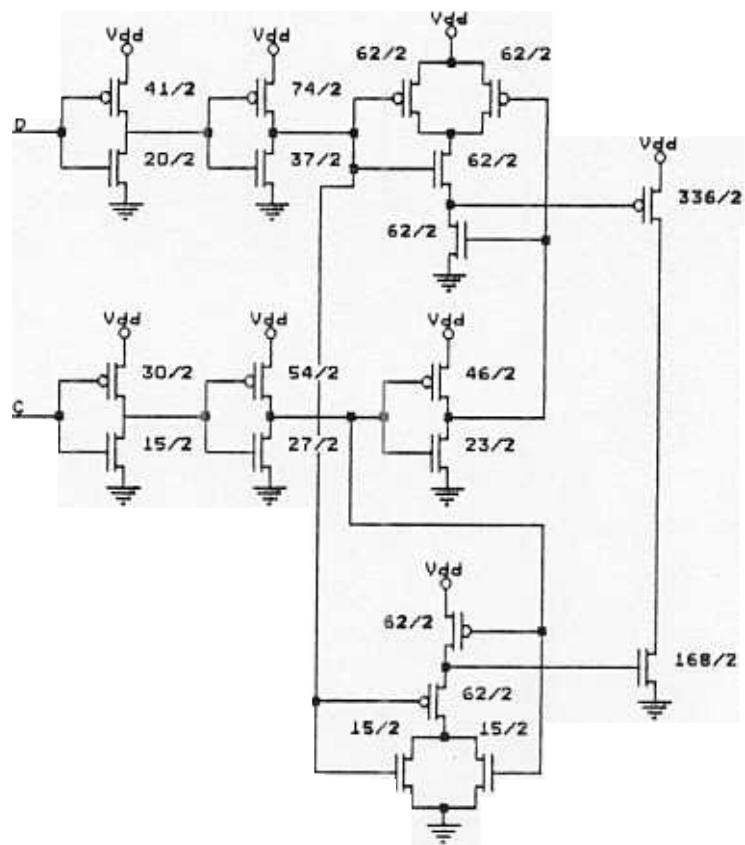

Para o cálculo do tempo de subida considere que  $K_n' = 2K_p'$  [11]. Logo, o transistor P deve ter o dobro do tamanho do transistor N para se ter os tempos de subida e descida aproximadamente iguais. Foram feitas duas tentativas:

- a)  $W_p/L_p = 336/2$  e  $W_n/L_n = 168/2$

- b)  $W_p/L_p = 168/2$  e  $W_n/L_n = 84/2$

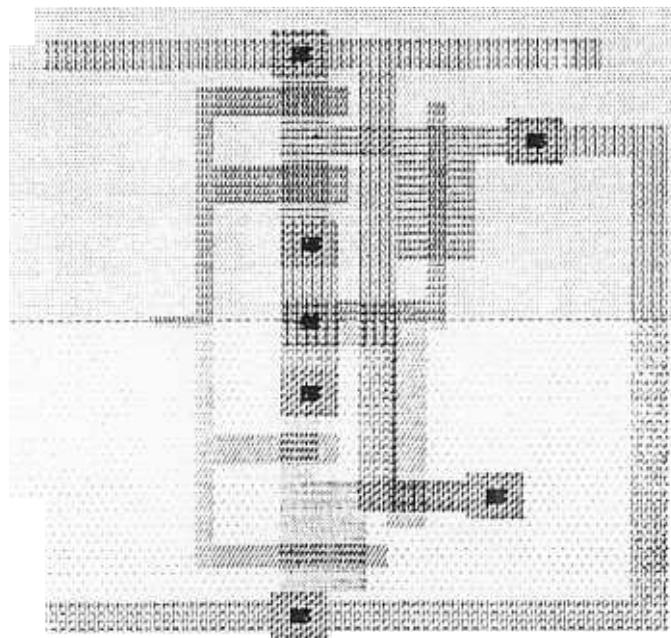

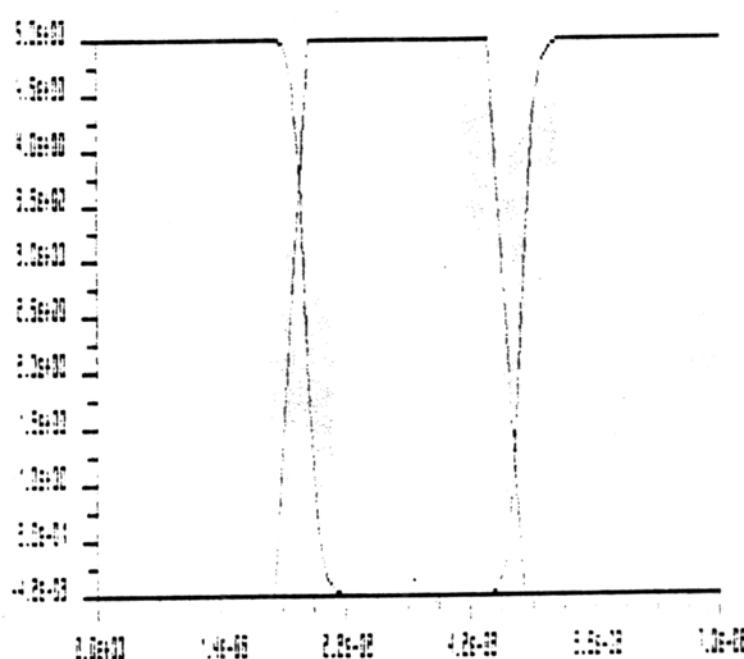

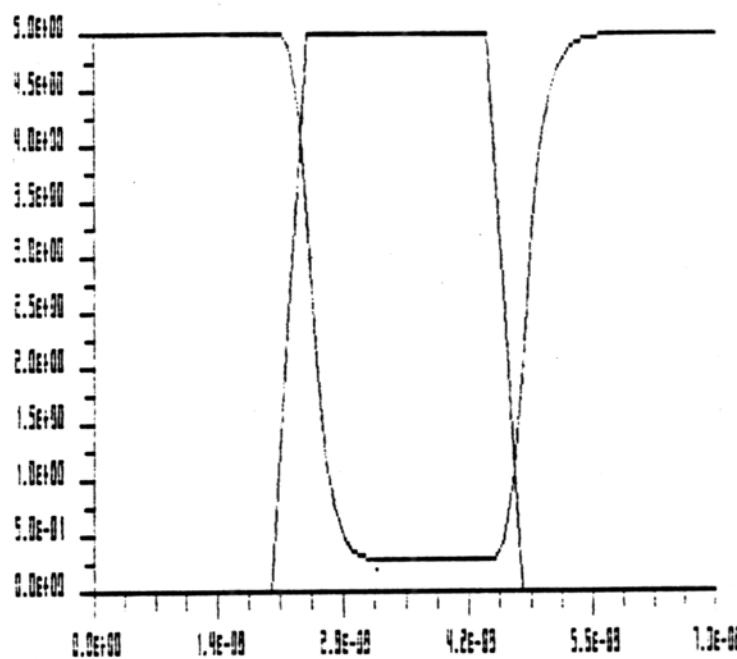

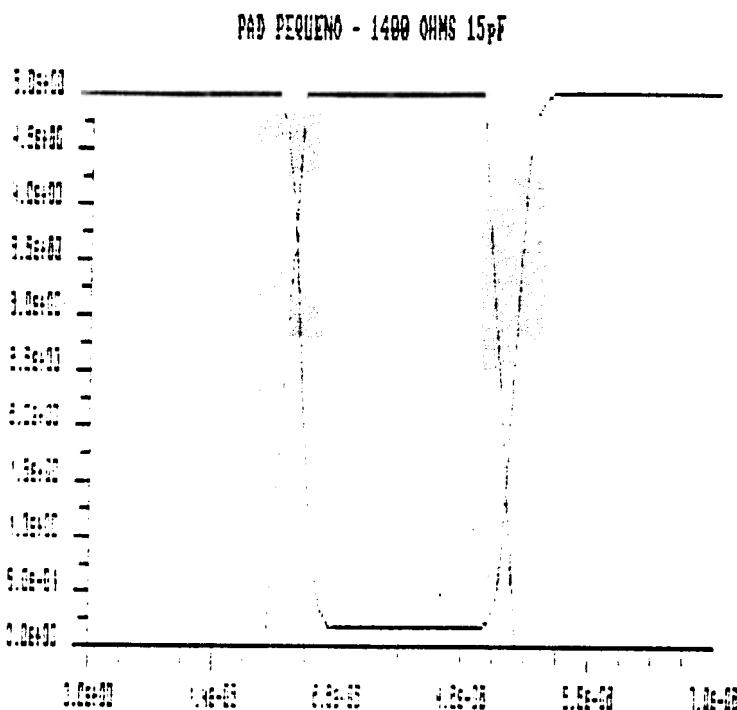

Conforme os resultados em anexo (figs. 5.12 a 5.19) verificamos, pela simulação feita no SPICE, que mesmo o "pad" pequeno, no pior dos casos, é capaz de excitar as duas cargas TTL satisfatoriamente. O menor tempo de subida/descida observado foi inferior a 4ns, considerando, é claro, que o tempo de subida/descida no padrão TTL é medido entre os níveis de tensão de 0,4V e 2,4V, o que não corresponde a 10% e 90% de VDD respectivamente como calculado anteriormente.

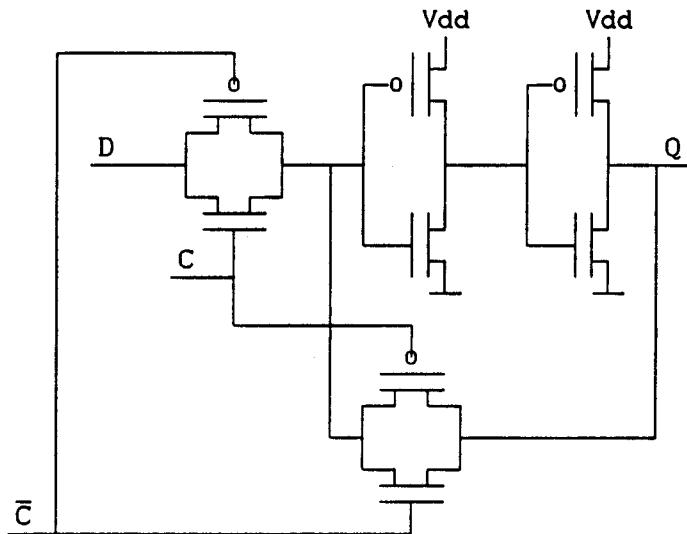

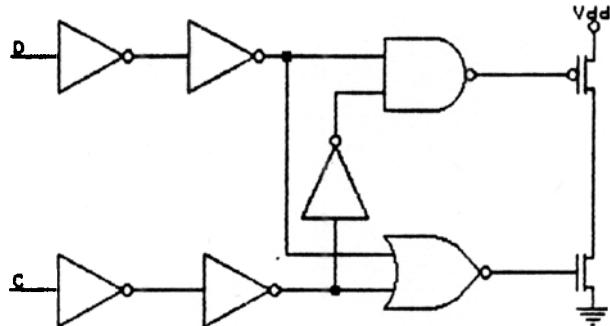

Um outro problema surge agora. Devido ao grande tamanho dos transistores de saída é necessário um transistor relativamente grande para excitá-lo e assim sucessivamente, caracterizando um processo de "bufferização" adequada. Existe um fator de aumento progressivo no tamanho dos inversores capaz de minimizar o atraso de propagação entre o ambiente interno ao circuito integrado e o ambiente externo e, ao mesmo tempo, fazer a "bufferização". Um circuito típico de um "pad" de saída com três estados é mostrado na fig. 5.10 [11].

fig. 5.10 - Circuito típico

Utilizando um fator de "bufferização" de 3 obtemos o diagrama a seguir, que ilustra o tamanho dos transistores (fig. 5.11).

fig. 5.11 - Circuito de "bufferização" com fator 3

Esta "bufferização" pode ser integrante do circuito do "pad", localizando-se junto aos transistores P e N de excitação final sem, praticamente, resultar em aumento de área utilizada. Alternativamente, pode ser implantada na própria matriz de transistores. Esta última solução dá mais flexibilidade, porém, reduz o espaço útil da matriz de portas para o usuário final.

fig. 5.12 - Layout do "pad" grande

fig 5.13 - Simulação do "pad" grande

fig 5.14 - Simulação do "pad" grande (modelo LL)

fig. 5.15 - Simulação do "pad" grande (modelo RR)

fig. 5.16 - Layout do "pad" pequeno

PAD PEQUENO - 15pF (ONDAS)

fig. 5.17 - Simulação do "pad" pequeno

PAD PEQUENO - 15pF & 1400 OHMS (LL)

fig. 5.18 - Simulação do "pad" pequeno (modelo LL)

fig. 5.19 - Simulação do "pad" pequeno (modelo RR)

#### 5.4 CANAL PARA ROTEAMENTO PERIFÉRICO

Até o momento, a preocupação maior era com a interconexão dos transistores de uma célula, desta com outras células formando os blocos e destes com outros blocos formando o circuito final. Mas não se deve esquecer que é necessário que os sinais do mundo externo cheguem às células e que os sinais de saída sejam levados ao mundo externo.

O problema do roteamento dos sinais do núcleo da matriz de portas para os PAD's é resolvido com a inclusão de um canal para roteamento entre o núcleo e os PAD's. O dimensionamento deste canal é feito de modo análogo ao dimensionamento do canal do núcleo das matrizes de portas com canal (ver ítem 4.2). A figura 5.20 mostra a disposição do canal.

fig. 5.20 - Disposição do canal

## 6. ALIMENTAÇÃO

### 6.1 INTRODUÇÃO

Um esquema de alimentação mal feito pode comprometer até mesmo o melhor dos projetos de uma matriz de portas. Problemas de alimentação nestes circuitos não são facilmente identificáveis. Normalmente resulta em ruído a nível de sistema, causando um mal funcionamento intermitente. Os circuitos integrados passam a ter baixa confiabilidade e o sistema também.

A seguir abordaremos os principais problemas de alimentação em uma matriz de portas:

- a) a distribuição de alimentação;

- b) o problema da eletromigração;

- c) o dimensionamento das linhas de alimentação;

- d) os problemas relativos à dissipação e encapsulamento.

### 6.2 DISTRIBUIÇÃO DA ALIMENTAÇÃO

Uma distribuição de alimentação bem feita é fundamental para o bom funcionamento da matriz. Na medida em que não se pode prever qual vai ser a sua utilização final, a distribuição de alimentação se torna um parâmetro dos mais importantes. A distribuição de alimentação se torna crítica à medida que a densidade de portas aumenta. Mais transistores são colocados na mesma área, o que significa que as linhas de alimentação podem passar a apresentar ruído. Para evitar estes problemas é necessário uma distribuição adequada da alimentação. Existem dois esquemas básicos que descreveremos a seguir: o fixo e o flexível.

A maioria das matrizes usa uma grade de alimentação fixa. Esta grade deve fornecer espaçamento adequado para roteamento das macrocélulas. Um espaçamento adequado para uma grade fixa pode ser conseguido com dois níveis de metal. Algumas matrizes restringem a colocação das

macrocélulas de modo que as portas de E/S da célula não caiam sob as linhas de alimentação. Outras utilizam células projetadas com mais de um ponto de contato, chamados de "antenas", de modo que cada sinal de E/S possa ter pontos alternativos de conexão, caso o original esteja sob uma linha de alimentação. Este último esquema tem o inconveniente de introduzir um congestionamento adicional de rotas.

A alternativa para os métodos acima é utilizar um esquema de alimentação flexível. Este método representa uma tarefa adicional para o software de CAD, e muitos sistemas de roteamento atualmente em uso não estão à altura deste desafio.

A distribuição de alimentação em uma matriz de portas com dois níveis de metal é melhor realizada no segundo nível, onde a metalização é mais espessa e a resistência menor. Uma política bastante utilizada é distribuir os sinais no primeiro nível e depois rotear a alimentação no segundo, utilizando as áreas que sobraram após o roteamento dos sinais. Infelizmente, com o aumento da densidade da matriz, há menos área disponível para alimentação, o que não é o ideal. Uma política melhor é fazer algumas aproximações conservativas sobre o uso da matriz e realizar uma distribuição de alimentação de acordo com estas aproximações.

Nas matrizes de portas convencionais, com dois níveis de metal, o primeiro nível de metal corre ao longo do canal, e o segundo nível é perpendicular, no núcleo da matriz. O primeiro nível de metal é utilizado tanto para barramentos de alimentação no núcleo como para linhas de sinal. O segundo nível é utilizado para linhas de sinal no núcleo e para linhas de alimentação na periferia. As linhas de alimentação ocupam uma grande parcela da área das matrizes de alta densidade. Estima-se [1] que a taxa de ocupação para uma matriz de portas com 20K gates seja perto de 60 %.

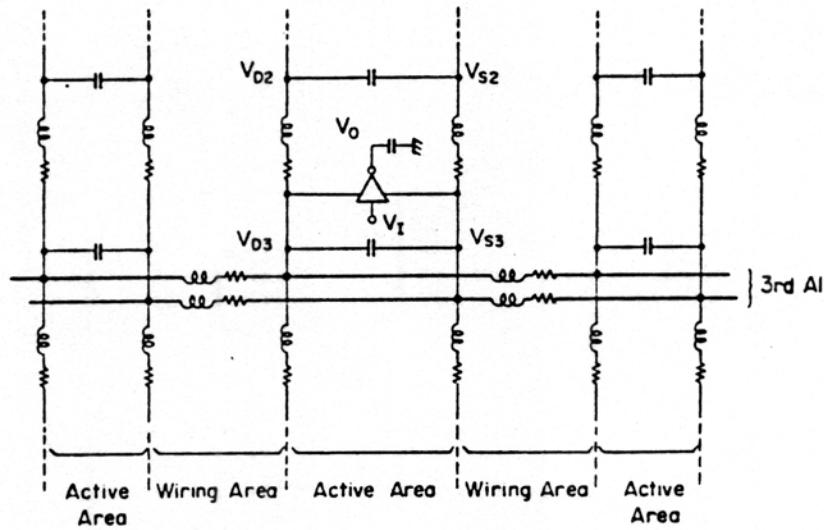

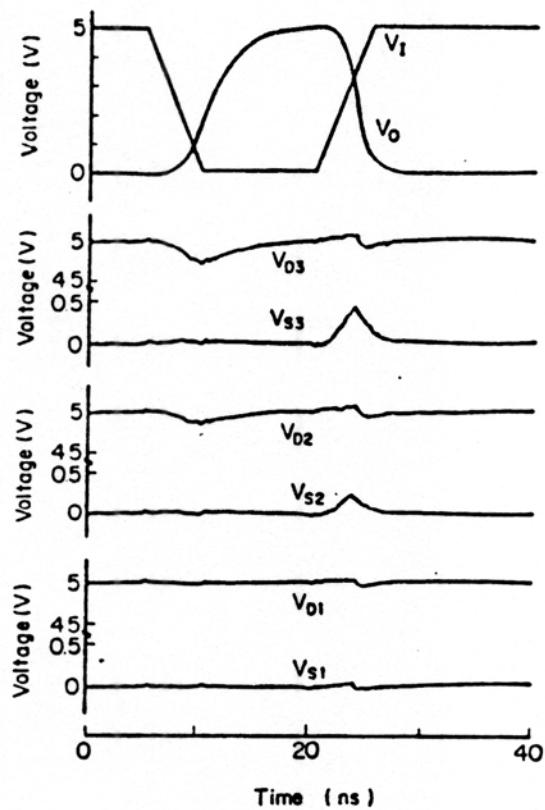

Nas figuras 6.1-A e 6.1-B podemos observar um esquema de como é a flutuação de tensão em um "buffer" inversor colocado no centro de uma matriz com 20K portas. É visível a flutuação de tensão existente nos pontos próximos ao buffer, demonstrando o efeito de uma distribuição não bem feita. Para matrizes com densidades acima desta, passa a ser conveniente o uso de três níveis de metalização [1].

fig. 6.1-A - Circuito equivalente com um inverSOR

fig. 6.1-B - Flutuação de tensão com dois níveis de metalização

Uma opção para a utilização de três níveis de metal, é distribuir a alimentação, a nível de micro-arquitetura, por uma malha fina de alumínio, e a seguir, a cada 25 colunas de células uma linha mais larga no segundo nível, e entre cada linha de células, uma linha mais larga no primeiro nível.

Ao invés de empilharmos as células, numa configuração de transistores do tipo P-N-P-N, podemos espelhar as células topo a topo, obtendo uma configuração do tipo P-N-N-P (fig. 6.2). Esta organização permite compartilhar os barramentos de VDD e VSS entre fileiras adjacentes apenas com o aumento da sua largura, com consequente economia de espaço. Pode-se ainda alargar, quando possível, o barramento de alimentação pela metalização associada a cada macrocélula.

fig. 6.2 - Configuração P-N-N-P

Toda a alimentação no interior da matriz de células se origina nos "pads" de VDD e VSS, situados na periferia do circuito integrado. Esta corrente aumenta a medida que nos aproximamos da periferia. Deste modo, uma opção para evitar eletromigração e ruído, é criar mais um nível na malha de alimentação. Um esquema possível, é despovoar  $N$  fileiras de células a cada  $M$  fileiras, e passar um barramento no primeiro nível de metal com largura  $X$ . Podemos despovoar  $P$  colunas no meio da matriz, para permitir um barramento no segundo nível com largura  $Y$ . Para uma matriz com 130.000 portas, valores encontrados para  $N$ ,  $M$  e  $X$  são respectivamente 4, 20/40 e 150/300 micra. Para os valores de  $P$  e  $Y$  temos 50/150 e 300/500 micra [7].

Há mais ainda para se considerar. Existe também o efeito de distribuirmos a alimentação nas células de E/S e o problema de fornecer alimentação aos "buffers" de saída sem afetar a matriz de células ou circuitos fora dela.

Um esquema de alimentação completo envolve anéis de alimentação ao redor do núcleo da matriz. Podemos usar, p. ex., seis anéis no segundo nível de metal. Os dois anéis externos forneceriaiam alimentação para os transistores P e N dos drivers de E/S. Os quatro anéis do interior poderiam fornecer alimentação para a matriz interna, e às áreas de "pré-drivers" e "receivers" de E/S. Assim, os grandes transistores de saída podem chavear sem afetar a matriz interna. A grade fina de alumínio e os barramentos reforçados se ligariam direto nestes quatro anéis. Estes por sua vez seriam ligados direto aos PAD's.

Um cuidado a mais para ser tomado, seria evitar os ruídos ocasionados pelo chaveamento simultâneo dos buffers de saída. Utilizando um circuito de E/S com controle sobre a taxa de variação da tensão de saída, é possível diminuir a excursão de corrente que causa este ruído. Como vantagem adicional existe o fato de se poder acionar cargas de capacidade diferentes, com praticamente o mesmo tempo de propagação. Não se deve ainda esquecer de um circuito adequado de proteção para entrada e saída, com diodos na entrada e proteção contra curto-circuito.

Se estes cuidados forem tomados na elaboração da distribuição de alimentação, veremos que é possível obter um excelente projeto, mesmo para matrizes de portas de altas densidades.

### 6.3 ELETROMIGRAÇÃO E O PROBLEMA DO DIMENSIONAMENTO

Eletromigração é o termo utilizado para denominar o transporte de massas em condutores metálicos submetidos a altas densidades de corrente (tipicamente acima de  $10^5$  A/cm<sup>2</sup>) [15]. Este transporte ocorre, principalmente, devido a transferência de energia cinética do fluxo de elétrons para os átomos da rede cristalina do condutor, ocasionando o deslocamento ou mesmo a retirada de átomos desta rede [11] [13] [15] [16]. Dois tipos de falhas podem ocorrer devido a eletromigração:

1) o acúmulo de "buracos" na rede cristalina pode ocasionar a ruptura do condutor (círcuito aberto, fig. 5.3).

2) o acúmulo de átomos deslocados, principalmente próximos ao terminal (+) do condutor, pode ocasionar um curto circuito com os condutores adjacentes [1] (fig. 5.4).

Fig. 1. 1 mil wide Al stripe I/C conductor which has failed due to electromigration.

fig. 6.3 - Círcuito aberto

fig 6.4 - Curto-circuito

A eletromigração depende também de outros fatores, como temperatura do condutor, tipo de rede cristalina (monocristalina ou policristalina), pureza do material, etc. Experiências mostram que redes monocristalinas (como o alumínio) estão menos sujeitas a este fenômeno do que redes policristalinas (como o poli-silício). Mostram também que este fenômeno depende do valor rms da corrente, no caso da corrente ser pulsada [11]. A eletromigração pode ser considerada desprezível para densidades de corrente abaixo de  $1 \mu\text{A}/\mu\text{m}^2$  ( $10^5 \text{ A}/\text{cm}^2$ ) [15] [16]. Deve-se tomar muito cuidado no momento de dimensionar as linhas de alimentação (VDD e VSS) das células, pois apesar das correntes envolvidas serem de alguns mA apenas, as dimensões dos condutores são da ordem de alguns microns apenas, podendo levar a densidades de corrente superiores a  $1 \mu\text{A}/\mu\text{m}^2$ .

A seguir um exemplo de dimensionamento de linhas de alimentação em matrizes de portas:

Célula Básica

fig. 6.5 Célula básica

Existem basicamente 2 componentes de corrente:

1) devido a condução simultânea dos 2 transistores.

2) devido as cargas (capacitores).

A resistência de canal dos transistores P e N é, respectivamente:

$$R_p = 75 \cdot W_p/L_p, \text{ kohms} \quad R_n = 25 \cdot W_n/L_n, \text{ kohms}$$

i) Cálculo da componente (1) da corrente:

Supondo o pior caso, ou seja,  $I_1 = I_{1\max}$  durante todo o tempo de

subida (ou descida) do relógio temos:

$$I_{1\text{rms}} = \frac{2}{T_{ck}} \cdot \left[ \int_0^{T_r} I_{1\max}^2 dt \right]^{1/2} = \frac{2T_r^{1/2}}{T_{ck}} \cdot I_{1\max}$$

mas, no pior caso

$$I_{1\max} = \frac{V_{dd}}{R_p + R_n}$$

então,

$$I_{1\text{rms}} = \frac{2T_r^{1/2} V_{dd}}{T_{ck} \cdot (R_p + R_n)}$$

ii) Cálculo da componente 2 da corrente:

No caso da descarga do capacitor através do transistor N, o valor RMS da corrente é o mesmo que para o caso da carga.

$$I_{2rms} = \left[ \frac{1}{T_{ck}} \int_0^{T_{ck}} (I_0 e^{-t/R_p C})^{1/2} dt \right]^{1/2} \quad \text{onde } I_0 = \frac{V_{dd}}{R_p}$$

$$I_{2rms} = I_0 \left[ \frac{R_p C}{2T_{ck}} \right]^{1/2} (1 - e^{-2T_{ck}/R_p C})^{1/2}$$

Para ilustrar o exemplo, considere :  $ck = 20 \text{ MHz} \rightarrow T_{ck} = 50 \text{ ns}$   $T_r = 2 \text{ ns}$   $W_p/L_p = W_n/L_n = 3 \rightarrow R_p = 25 \text{ kohms}$  e  $R_n = 8,3 \text{ kohms}$   $VDD = 5 \text{ V}$   $C = 100 \text{ fF}$   $I_{total} = I_{1rms} + I_{2rms} = 42,4 \mu\text{A} + 31 \mu\text{A} = 74 \mu\text{A/célula}$ . Supondo a largura mínima das linhas de metal =  $4\mu$  [13] e uma densidade de corrente máxima de  $1 \text{ mA}/\mu^2$ , temos:

$$4 \text{ mA} / 74 \mu\text{A} = 54 \text{ pares por linha de VDD.}$$

Observe que neste exemplo foi considerado o pior caso, ou seja, todos os inversores chaveando ao mesmo tempo e submetidos a mesma carga. Portanto, o número máximo de pares pode aumentar em função do número médio de chaveamentos em uma coluna e da taxa de utilização das células.

#### 6.4 DISSIPAÇÃO DE POTÊNCIA

No ítem anterior, foi discutido um problema sério em circuitos integrados, o do dimensionamento dos condutores. Outro problema, igualmente sério, é o da remoção da potência dissipada pelos transistores dentro dos circuitos integrados. No exemplo visto anteriormente, cada célula consome cerca de  $74 \mu\text{A}$ , dissipando  $5 \times 74 = 0,4 \text{ mW}$ . Em uma matriz de portas de tamanho médio, com cerca de 3000 células, a potência dissipada seria de, aproximadamente,  $1,2 \text{ W}$  ! Em termos de circuitos VLSI esta é uma potência que não pode ser desprezada.

Dois fatores são fundamentais quando se fala em dissipaçāo de potência.

O primeiro é a temperatura máxima de operação, ou a temperatura acima da qual ocorre uma degradação nos parâmetros dos transistores. O outro, é o fator econômico. É muito mais interessante para um projetista utilizar um circuito integrado que não necessite de nenhum dispositivo externo para dissipar sua potência. A utilização de dissipadores torna o projeto mais caro e, as vezes, inviável. Além do mais, para melhorar as características térmicas dos circuitos integrados, é necessária a utilização de encapsulamento cerâmico, que é mais caro que o encapsulamento plástico.

Para o cálculo da temperatura interna do circuito integrado em função da potência dissipada, é necessário o conhecimento da resistência térmica ( $\theta$ ) do encapsulamento. Esta resistência nos dá a diferença de temperatura ( $\Delta T$ ) por watt dissipado .

$$T_c - T_a = \Delta T_{CA} = \theta_{ja} \cdot P_d$$

Exemplo:

Um encapsulamento DIP plástico de 40 pinos possui uma resistência térmica total  $\theta_{ja} = 62^{\circ}\text{C/W}$ . Supondo que a temperatura máxima de operação seja  $100^{\circ}\text{C}$  e que a temperatura ambiente é de  $25^{\circ}\text{C}$  a potência máxima que pode ser dissipada é:

$$P_{max} = \frac{\theta_{ja}}{T_c - T_a} = \frac{62}{100 - 25} = 0,83 \text{ W}$$

No caso deste circuito integrado dissipar uma potência maior que 830 mW, será necessária a utilização de dissipadores para diminuir o  $\theta_{ja}$ .

## 7 ENGENHARIA REVERSA

### 7.1 INTRODUÇÃO

No estudo da implementação de uma matriz de portas sempre é uma boa medida reportar-se às experiências anteriores. Isto não é muito fácil em se tratando de circuitos comerciais, já que a competição é grande e obriga os fabricantes a manter segredo sobre seus projetos.

Uma maneira de superar esta falta de informação é utilizar a engenharia reversa. A engenharia reversa constitui-se basicamente em abrir um componente e através de sua análise obter informações relativas ao circuito projetado e às características de dimensionamento e espaçamento de seus componentes.

Deve-se deixar claro que o direito de patente existe, e o circuito analisado não pode ser copiado. Entretanto, nada impede que se realize estudos e se aprenda com o que for observado.

Nos trechos que se seguem, reportamos os métodos utilizados para a realização de engenharia reversa , e os resultados obtidos da análise de uma matriz de portas comercial.

### 7.2 TÉCNICAS UTILIZADAS

A imagem de um circuito integrado, obtida através de um microscópio ótico, fornece informações que não são normalmente reveladas pelo projetista.

A decodificação de um circuito corresponde à passagem pelos seguintes níveis de representação:

1. Nível das máscaras ou dimensões físicas

2. Nível dos transistores ou elétrico

3. Nível lógico

4. Nível funcional

No nosso caso, a obtenção de informação se restringirá aos três primeiros níveis, já que o objetivo deste trabalho é levantar as características da matriz básica, e não a do circuito projetado.

Uma descrição detalhada dos métodos normalmente empregados em engenharia reversa, pode ser encontrada em [10]. A seguir descrevemos a metodologia que utilizamos no levantamento das características da matriz básica.

#### a) Abertura do Circuito Integrado

É uma tarefa que deve ser realizada com cuidado pois muitas vezes dispõe-se apenas de uma única amostra, e qualquer erro pode ser fatal. A técnica de abertura varia de acordo com o tipo de encapsulamento.

O encapsulamento mais fácil de abrir é aquele que possui uma janela metálica, sendo normalmente de cerâmica. Neste caso, com ajuda de um canivete ou estilete, força-se um dos cantos da janela até que ela solte totalmente. No caso do encapsulamento de cerâmica não possuir esta janela, pode-se prender a amostra em uma morsa, forçando-a no sentido horizontal, até que a parte superior se desprenda da parte inferior, tendo-se acesso ao circuito.

Finalmente, no caso do encapsulamento de plástico, pode-se ainda desbastar o encapsulamento pouco a pouco, até se ter acesso à cavidade onde se encontra o circuito. Forçando-se com estilete, consegue-se separar a parte superior da parte inferior do chip. Uma outra possibilidade, como descrito em [10] é derreter o encapsulamento de plástico pela ação do calor ou ataque de ácido.

#### b) Corrosão

Depois que o circuito integrado for aberto, pode haver a necessidade de se retirar a camada de passivação ( $\text{SiO}_2$  espesso), para obter-se uma imagem mais nítida do circuito em análise. Deve-se então corroer o  $\text{SiO}_2$  com uma solução de ácido fluorídrico diluído em água destilada na proporção de 1:10 a 1:20. Quanto mais lenta a reação, melhor o controle sobre ela e mais uniforme é a corrosão. Quando começar o surgimento de bolhas na superfície do circuito, a reação deve ser interrompida,

lavando-se o componente com água destilada em abundância. Para proceder-se à observação pelo microscópio, necessita-se ter a amostra convenientemente seca, com o uso de um secador elétrico ou similar.

### c) Fotografia

A fotografia do circuito integrado pode ser realizada em um microscópio ótico, que permita adaptar uma câmara fotográfica e que possua capacidade de ampliação entre 25 e 1000 vezes. Relatos anteriores nos indicavam o uso de luz polarizada, entretanto as observações realizadas foram feitas com luz comum, utilizando filtros coloridos.

Os filmes utilizados foram um P&B, com ASA 32 e outro colorido, com ASA 100. Quanto MENOR a sensibilidade do filme, melhor a qualidade das cópias obtidas. O uso de um fotômetro mostrou-se ser essencial para calcular o tempo adequado de exposição, já que a intensidade luminosa varia de acordo com o tipo de filtro e com a cena que está sendo observada. No trabalho realizado, utilizamos dois filtros: o de cor azul e o de cor marrom. O filtro de cor azul apresenta melhores resultados para fotografia P&B, obtendo-se um maior contraste. Já para as fotografias coloridas, o filtro de melhor resultado foi o marrom, e o filtro azul apresentou péssima visibilidade.

Para segurança é conveniente obter-se sempre mais de uma foto sobre a cena em questão, com iluminação, ampliação e filtros diferentes, pois o que está sendo visto nem sempre corresponde àquilo que vai aparecer depois nas fotos. Finalmente, deve-se ter o cuidado para fotografar algum circuito de referência, com dimensões conhecidas, para poder-se extrair as dimensões corretas dos componentes do circuito em estudo.

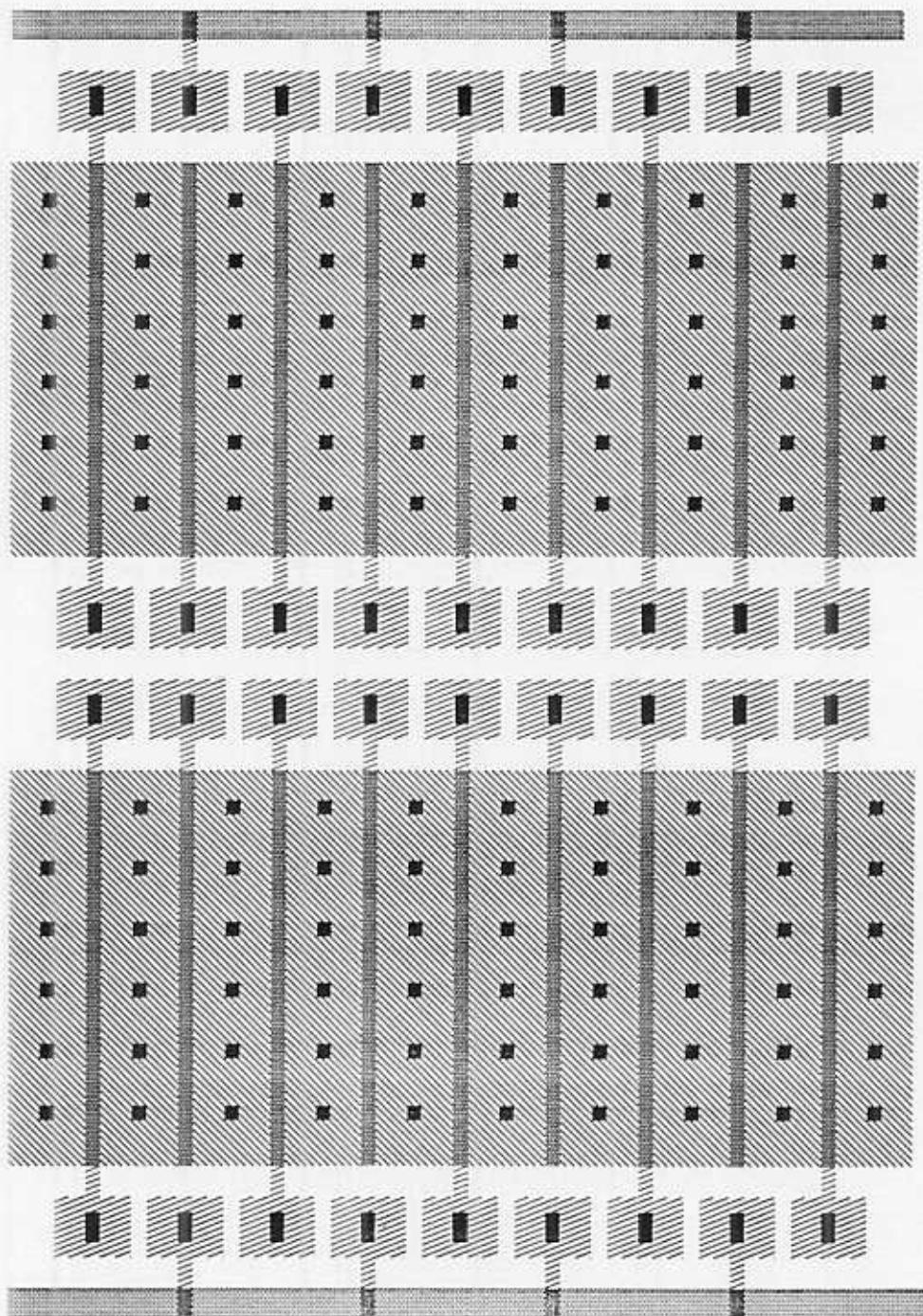

## 7.3 ANÁLISE DO CIRCUITO

Dividiremos nossa análise em dois aspectos básicos: macro-arquitetura e micro-arquitetura. Na macro-arquitetura analisaremos o circuito integrado de uma maneira global, avaliando as distribuições em termos de número de canais, largura dos mesmos e distribuição de alimentação, entre outros. Na micro-arquitetura procuraremos avaliar as células básicas, regras de projeto e circuitos de E/S.

### a) Macro-arquitetura

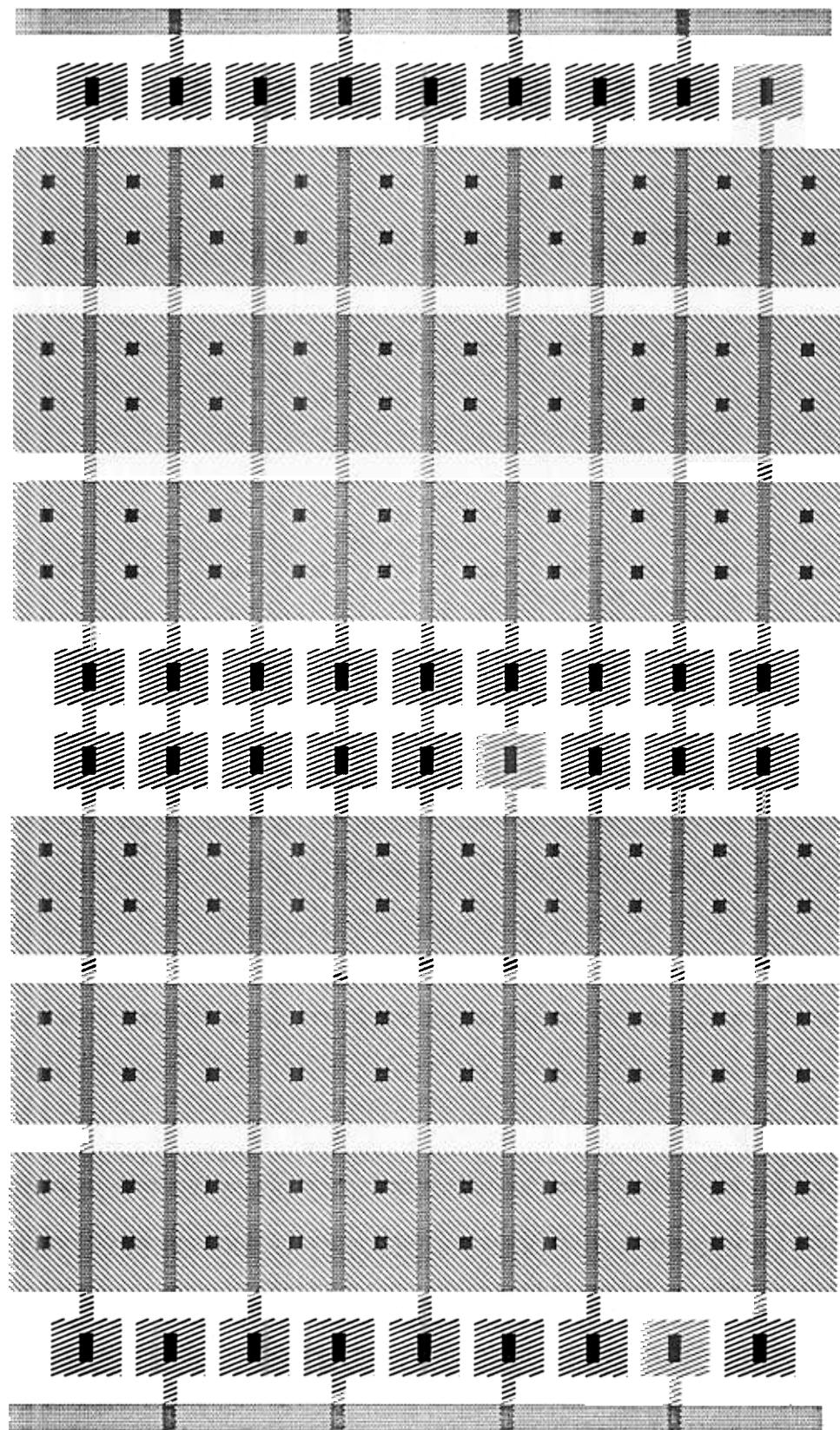

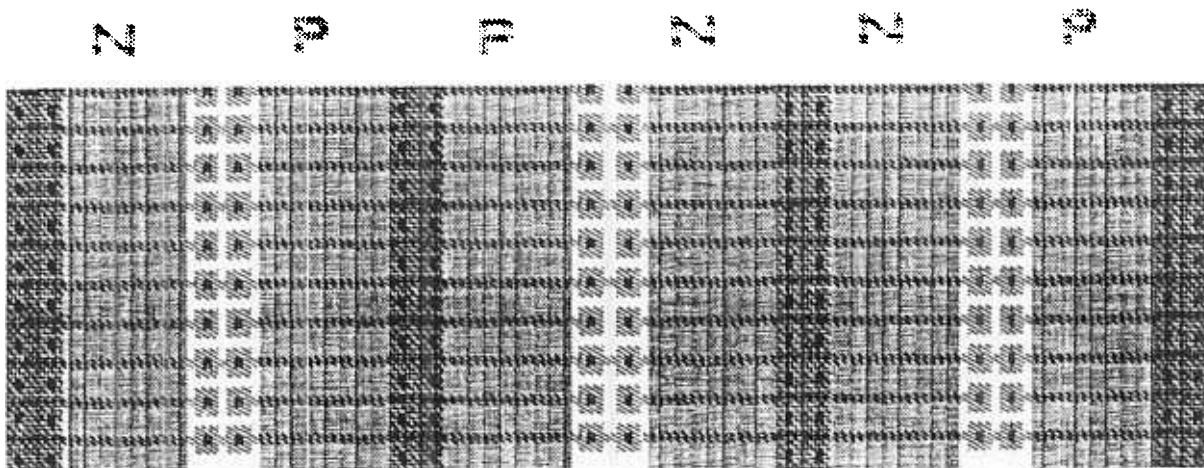

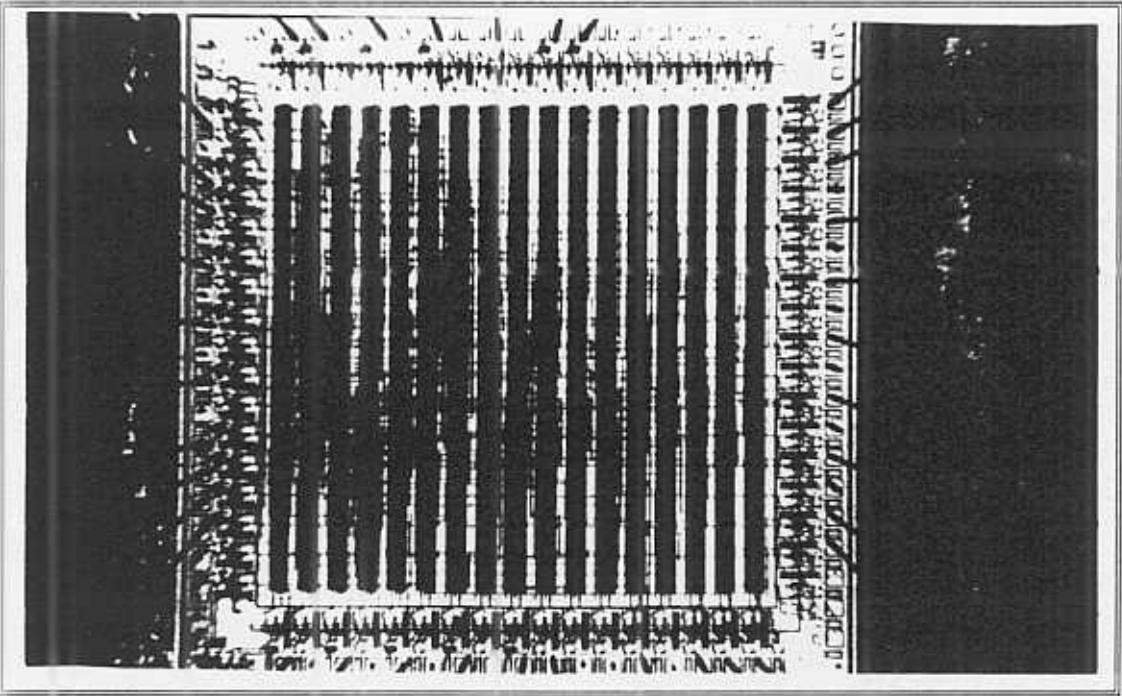

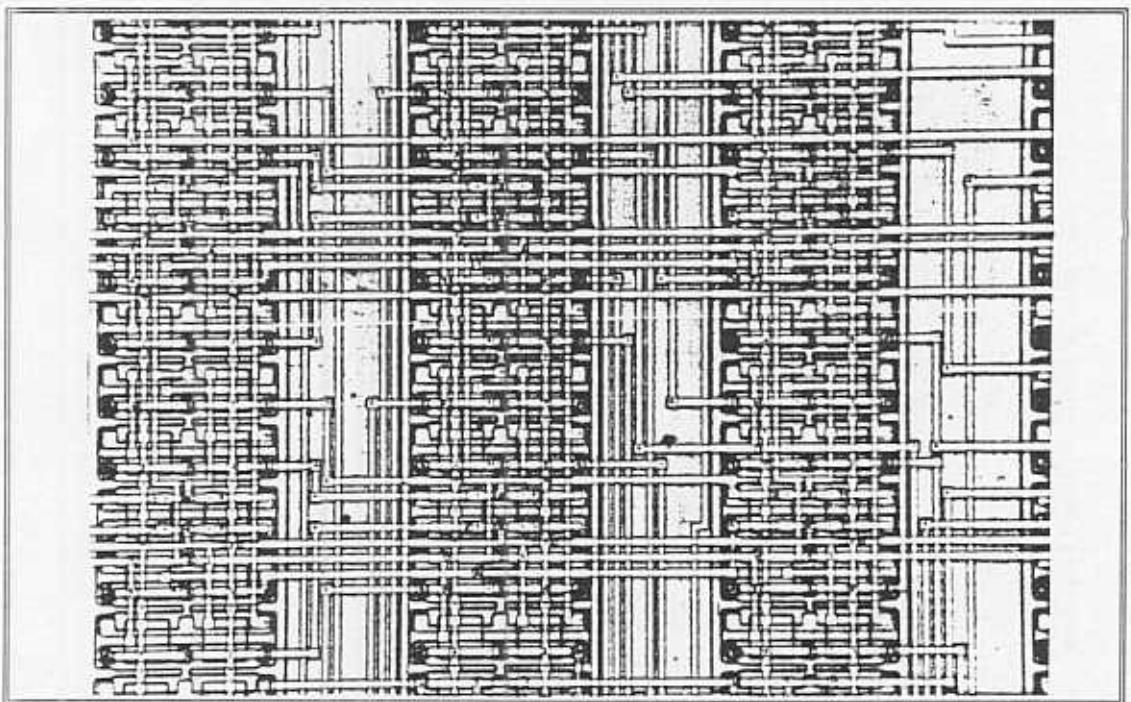

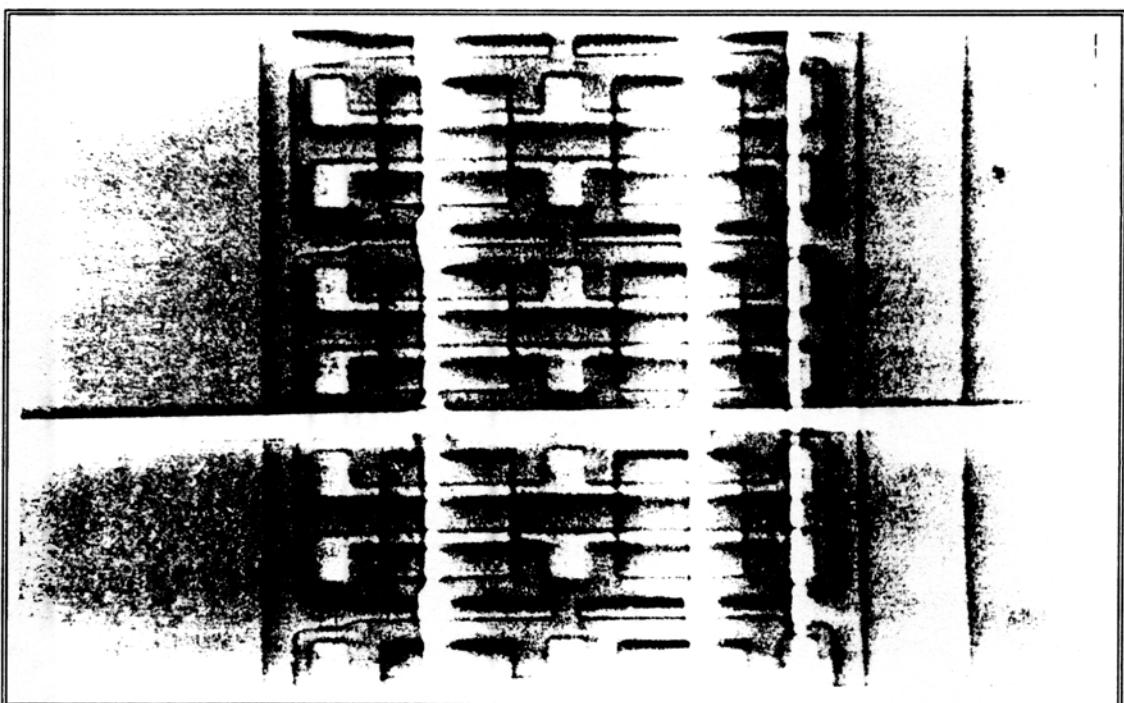

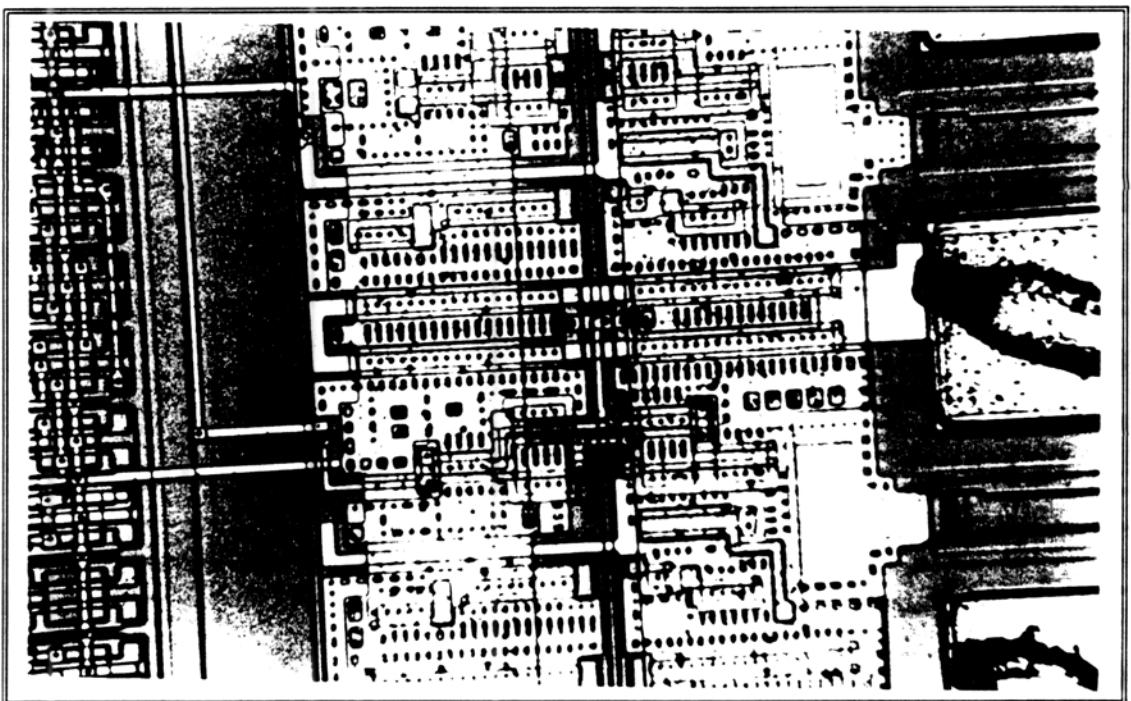

Da foto global do circuito integrado (1), podemos obter o seu tamanho: 9 mm X 9 mm. Encontramos também 19 canais de roteamento e 17 fileiras de células. Pode-se observar ainda 73 PAD's, dos quais 37 utilizados, sendo 21 de entrada e 16 de saída. Estas informações conferem com as existentes com o fornecedor da amostra.

Da foto (2) podemos obter dados bastante importantes para o roteamento dos sinais: largura do canal ( $73 \mu\text{m}$ ), altura da coluna de células ( $118 \mu\text{m}$ ), número máximo de trilhas por canal (10), número máximo de trilhas no interior de uma fileira de células (15). Estes dados são importantes porque o seu cálculo é difícil e advém da experiência com a fabricação e projeto de matrizes de portas.

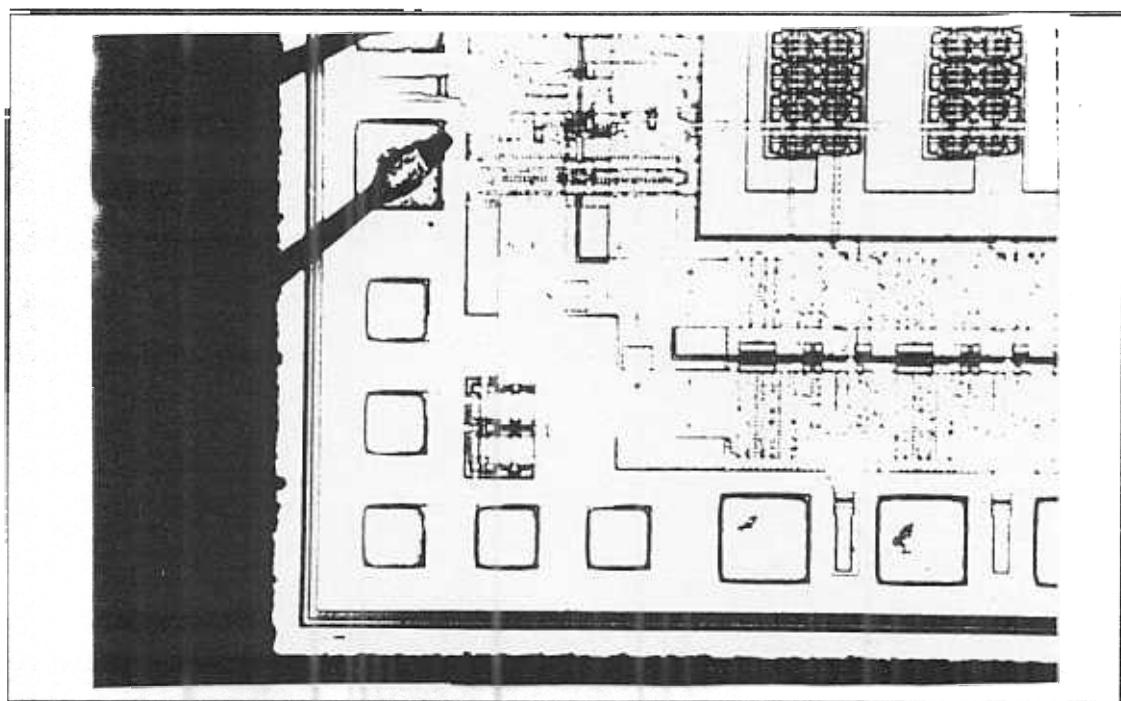

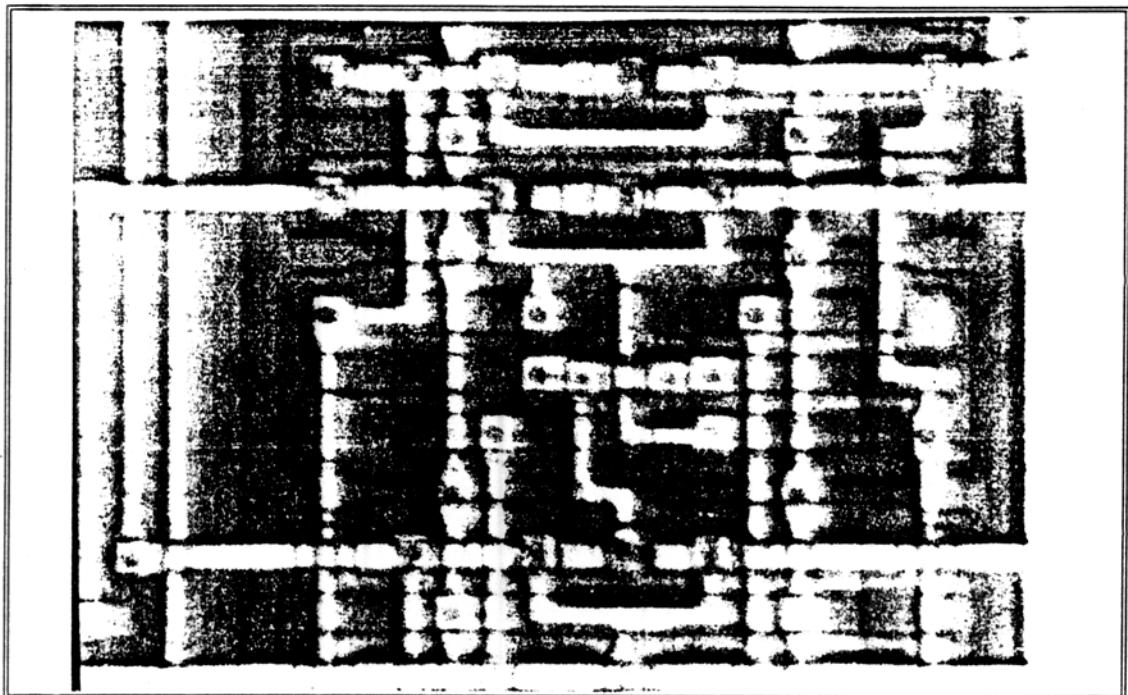

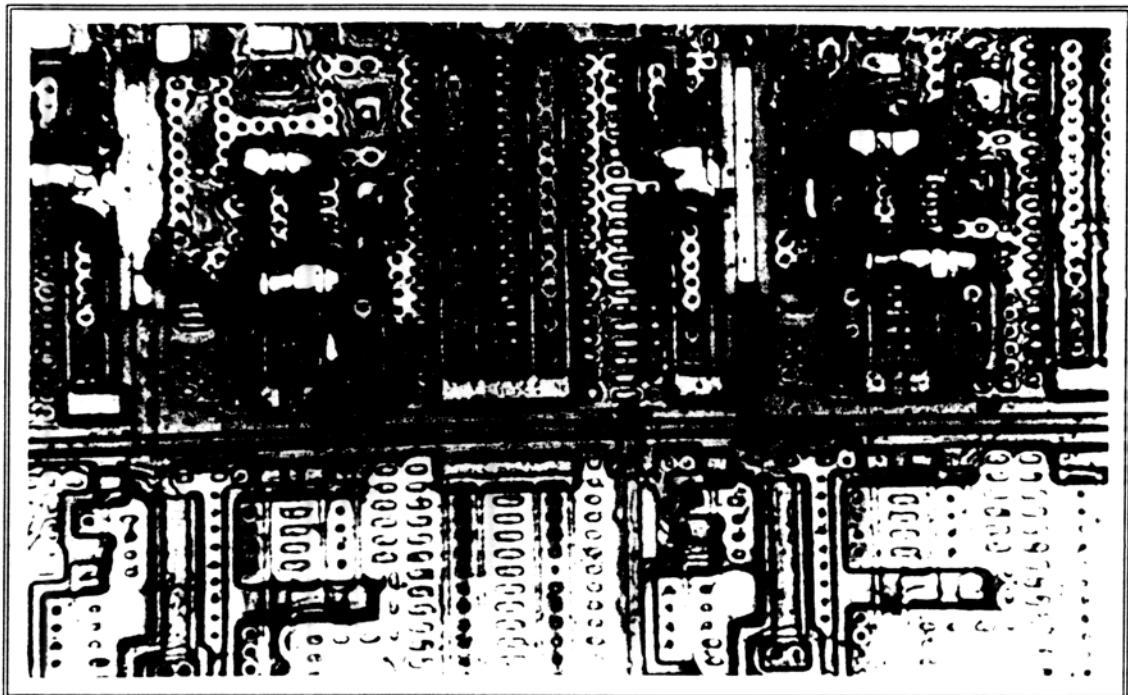

Na foto (3) vemos um detalhe interessante: um circuito de teste no canto do circuito integrado, eventualmente para caracterização de parâmetros elétricos, composto de uma célula básica e um pequeno buffer de saída. Podemos extrair também a largura dos anéis de VDD e VSS ( $80 \mu\text{m}$ ) e notar um espaçamento cuidadoso entre VDD e VSS de  $23 \mu\text{m}$ .

Na foto (4) observamos a periferia e um conjunto de células básicas que nos permite extrair os seguintes parâmetros: número de células em uma fila (85) e a partir daí calcular o número total de células da matriz: 1445. Nesta foto extraímos também a largura do canal vertical ( $90 \mu\text{m}$ ), o espaçamento dos PAD's para a periferia ( $27 \mu\text{m}$ ), a distância entre PAD's ( $82 \mu\text{m}$ ) e do PAD para a borda do circuito ( $32 \mu\text{m}$ ). Em comparação com a foto (5) utilizada como referência , podemos obter a dimensão do PAD:  $80 \mu\text{m} \times 80 \mu\text{m}$ .

### b) Micro-arquitetura

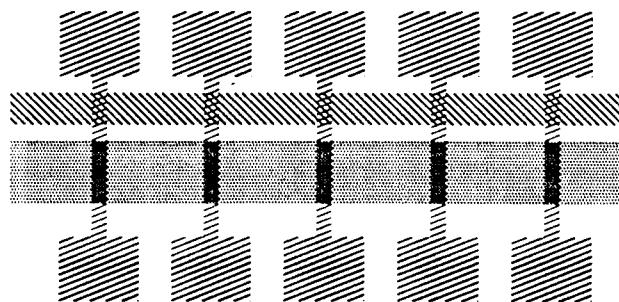

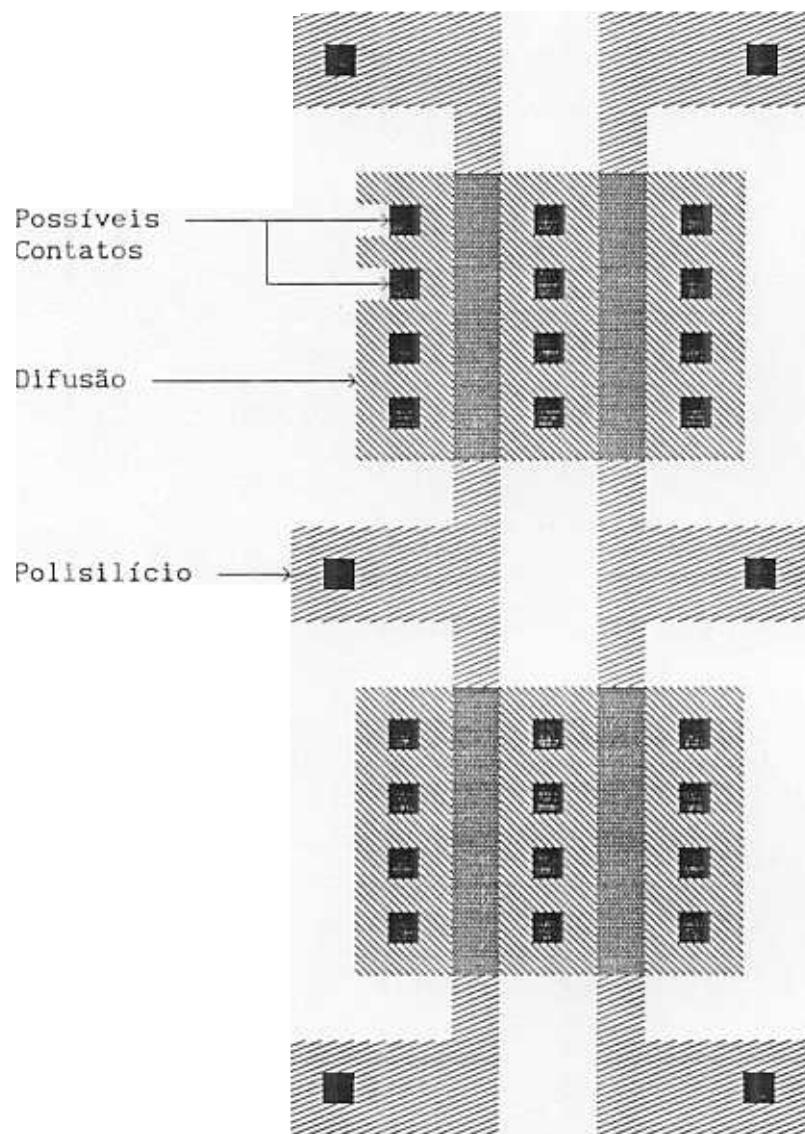

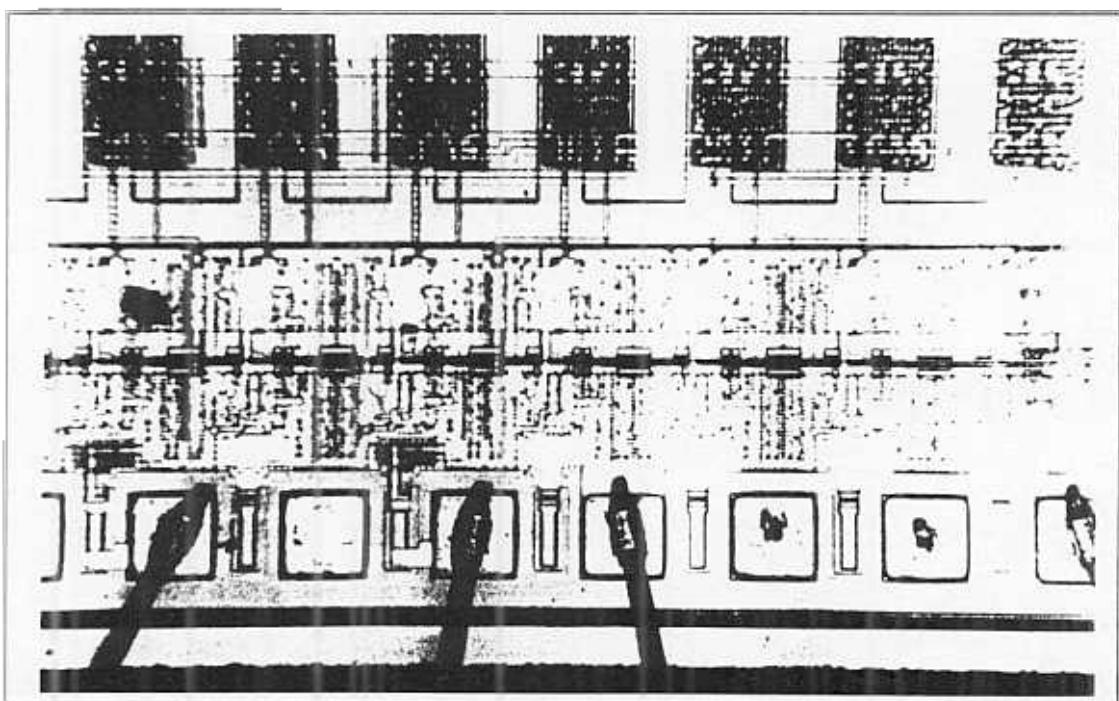

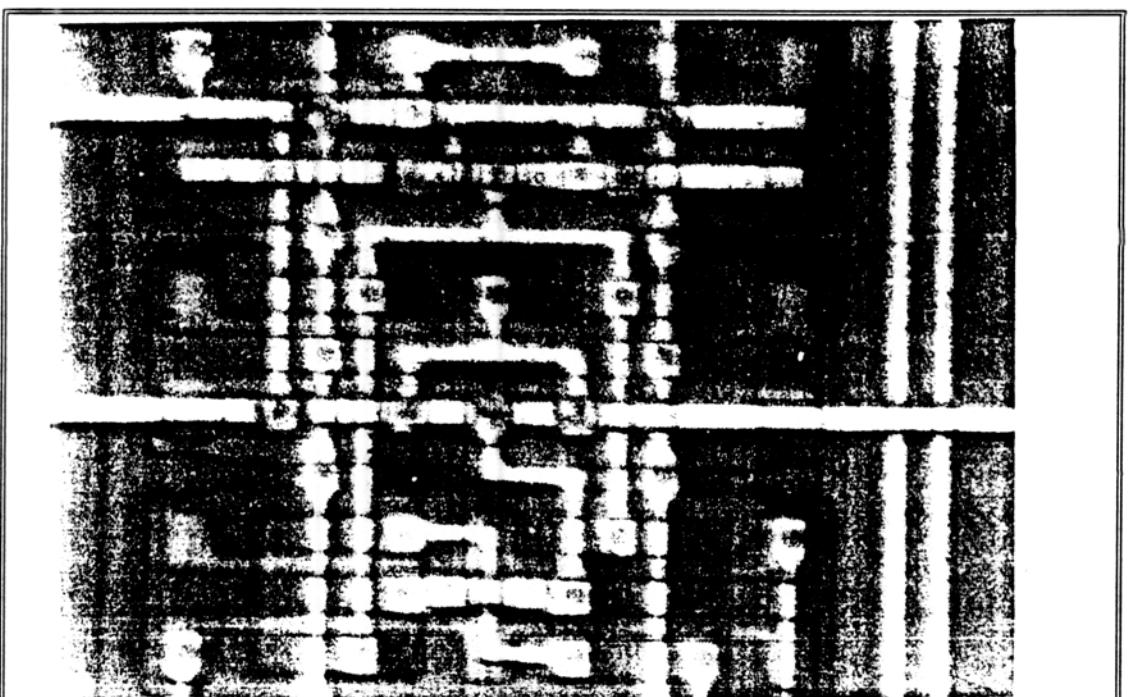

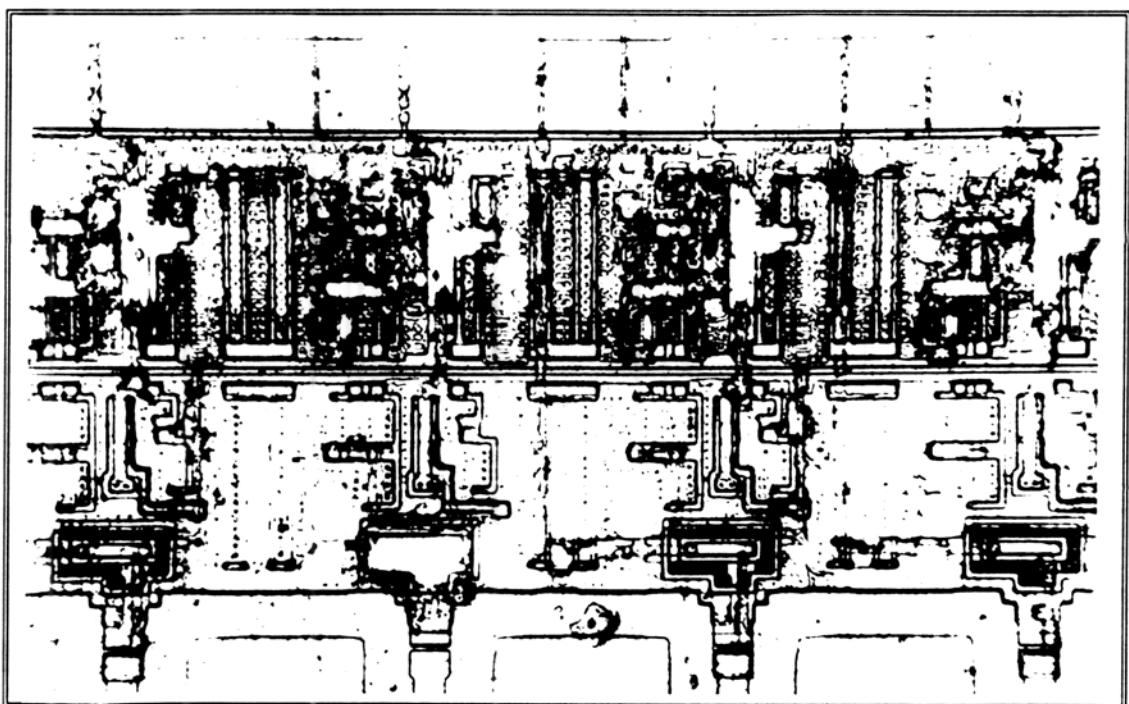

Na foto (6) pode-se ver claramente o tipo de célula básica utilizada: um típico "osso-de-cachorro", com um par de inversores, com a porta dos dois transistores conectados, e com isolamento geométrico. Um esquema completo da célula pode ser visto na figura 7.1, mostrando a proporção entre as linhas de poli-silício e metal, os possíveis pontos de contato e a razão W/L, no caso 8.5 para todos os transistores.

Nas fotos (7,8) foi extraída a maior parte dos parâmetros relativos às regras de projeto. Alguns deles, como os relativos à difusão, não puderam ser levantados. Observa-se claramente o uso de dois níveis de metal, sendo o segundo nível mais largo que o primeiro. Os resultados levantados se encontram resumidos na TABELA I.

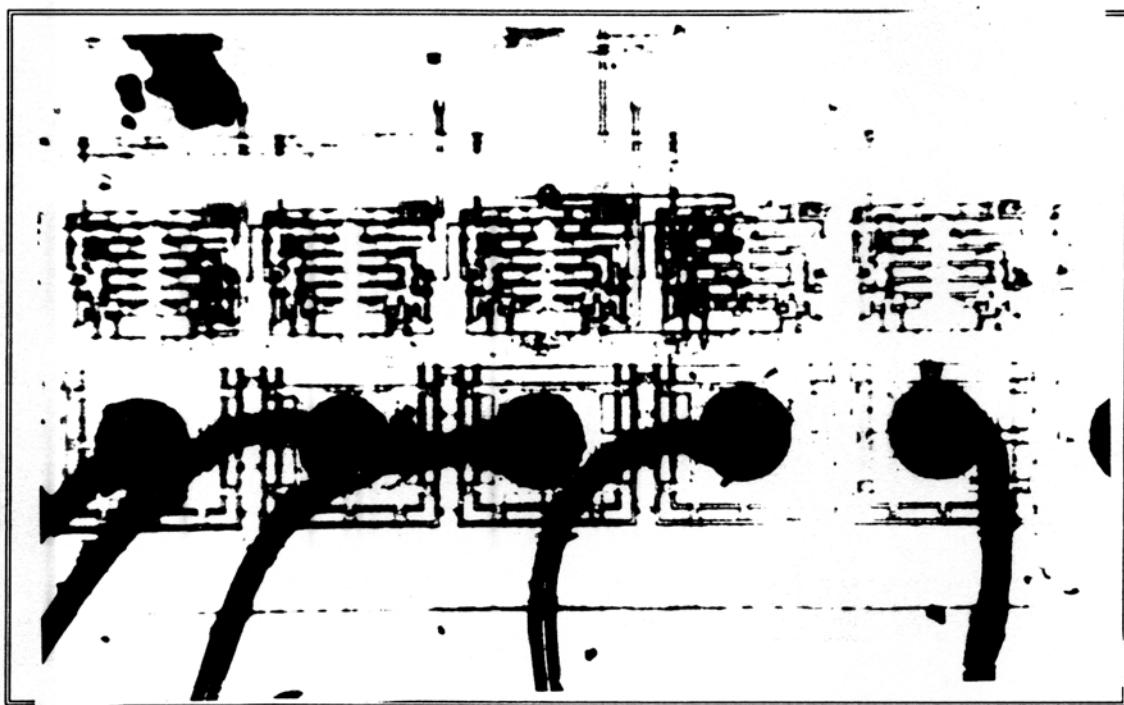

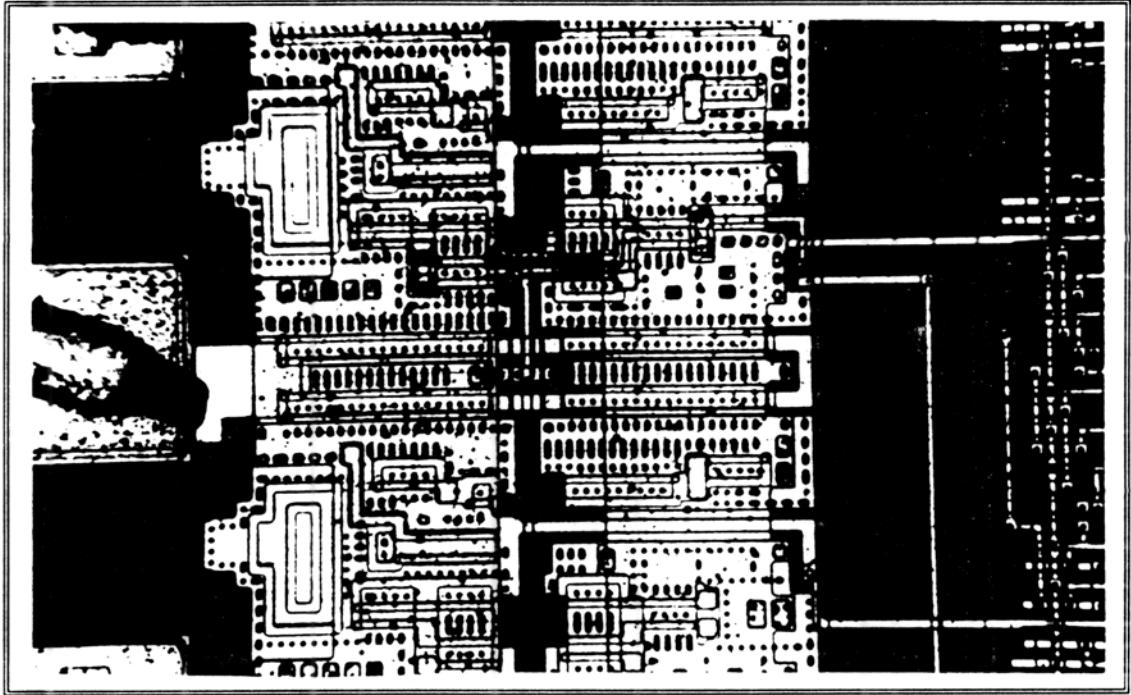

A periferia do circuito integrado pode ser vista em detalhe nas fotos (9,10) : os "pads", o resistor de polisilício e os diodos de proteção e alguns transistores menores, possivelmente de conversão de nível e "pré-driver". Bem abaixo dos "pads" podem ser vistos dois grandes transistores de saída, cuja razão W/L não pudemos determinar. Nota-se também a versatilidade do PAD, que de acordo com a metalização utilizada, pode ser configurado como entrada, saída ou alta impedância.

Finalmente, nas fotos (11,12) os mesmos circuitos podem ser vistos após a corrosão total do metal, quando as linhas de VDD e VSS puderam ser retiradas, mostrando alguns detalhes a mais sobre os circuitos. O maior problema nesta etapa é obter uma corrosão uniforme do metal, de modo que o poli-silício e difusão não sejam atacados, o que infelizmente não pudemos conseguir, prejudicando uma melhor análise destes circuitos.

## REGRAS DE PROJETO

### 1. Difusão

|                                       |    |

|---------------------------------------|----|

| 1.1 Largura mínima .....              | ND |

| 1.2 Espaçamento D-D .....             | ND |

| 1.3 Espaçamento para um contato ..... | ND |

| 1.4 Espaçamento P-D .....             | ND |

### 2. Poli-silício

|                                          |           |

|------------------------------------------|-----------|

| 2.1 Largura mínima do gate.....          | 3.0 $\mu$ |

| 2.2 Largura mínima do poly .....         | ND        |

| 2.3 Espaçamento mínimo P-P .....         | ND        |

| 2.4 End-cap (comp. mínimo) .....         | ND        |

| 2.5 Espaçamento mínimo poly to S/D ..... | 6.0 $\mu$ |

### 3. Contato

|                                                                         |           |

|-------------------------------------------------------------------------|-----------|

| 3.1 Largura mínima .....                                                | 2.5 $\mu$ |

| 3.2 Largura máxima .....                                                | ND        |

| 3.3 Espaçamento mínimo entre contatos de difusão                        | 3.0 $\mu$ |

| 3.4 Espaçamento mínimo entre cont. dif. e gate .                        | 0.0       |

| 3.5 Largura mínima borda de metal p/ contato de<br>difusão e poly ..... | 1.5 $\mu$ |

| 3.6 Mínimo overlap do poly<br>direção da corrente....                   | 1.5 $\mu$ |

| outras direções .....                                                   | 1.0 $\mu$ |

| 3.7 Mínimo espaçamento contato poly para difusão                        | ND        |

### 4. Metal

|                                           |           |

|-------------------------------------------|-----------|

| 4.1 Largura mínima metal 1 .....          | 2.5 $\mu$ |

| 4.2 Largura mínima metal 2 .....          | 4.5 $\mu$ |

| 4.3 Espaçamento mínimo entre metais ..... | 2.5 $\mu$ |

| 4.4 Largura mínima vs. corrente .....     | ND        |

**5. Via**

|                                                  |           |

|--------------------------------------------------|-----------|

| 5.1 Largura mínima contato de via .....          | 2.5 $\mu$ |

| 5.2 Largura mínima borda de metal .....          | 1.5 $\mu$ |

| 5.3 Espaçamento mínimo entre contatos de via ... | ND        |

| 5.4 Espaçamento mínimo entre via e gate .....    | ND        |

## 6. PADS

|                                           |                         |

|-------------------------------------------|-------------------------|

| 6.1 Número de PADS .....                  | 73                      |

| 6.2 Utilizados:.....                      | 37                      |

|                                           | Entrada: 21 / Saída: 16 |

| 6.3 Tamanho do PAD .....                  | 80 x 80                 |

| 6.4 Resistor de poly .....                | 82 x 18                 |

| 6.5 Distância do PAD para periferia ..... | 27 $\mu$                |

| 6.6 Distância PAD para borda .....        | 32 $\mu$                |

| 6.7 Distância PAD-PAD .....               | 82 $\mu$                |

## 7. Micro-arquitetura

|                                             |           |

|---------------------------------------------|-----------|

| 7.1 Altura da célula .....                  | 100 $\mu$ |

| 7.2 Largura da célula .....                 | 26 $\mu$  |

| 7.3 Altura da coluna de células .....       | 118 $\mu$ |

| 7.4 Número máximo de trilhas internas ..... | 15        |

| 7.5 Razão W/L .....                         | 26/3      |

### 8. Macro-arquitetura

|                                              |           |

|----------------------------------------------|-----------|

| 8.1 Tamanho do die .....                     | 9mm x 9mm |

| 8.2 Número de canais .....                   | 19        |

| 8.3 Número de filas de células .....         | 17        |

| 8.4 Número de células em uma fila .....      | 85        |

| 8.5 Número estimado de células .....         | 1445      |

| 8.6 Número máximo de trilhas por canal ..... | 10        |

| 8.7 Número máximo de trilhas internas .....  | 15        |

| 8.8 Altura da coluna de células .....        | 118 $\mu$ |

| 8.9 Largura do canal .....                   | 73 $\mu$  |

| 8.10 Largura canal vertical .....            | 90 $\mu$  |

| 8.11 Largura do VDD e VSS .....              | 80 $\mu$  |

8.12 Distância VDD & VSS .....  $23 \mu$

8.13 Alternância dos transistores ..... P-N-P-N

fig. 7.1 - Esquema da célula básica

fig. 7.2 - Foto 1 : Planta baixa do CI

fig. 7.3 - Foto 2 : Detalhe dos canais

fig 7.4 - Foto 3 Circuito de teste

fig 7.5 - Foto 4 Detalhe da periferia

fig. 7.6 - Foto 5 : CI de referência

fig. 7.7 - Foto 6 : Detalhe da célula básica (I)

fig. 7.8 - Foto 7 : Detalhe da célula básica (II)

fig. 7.9 - Foto 8 : Detalhe da célula básica (III)

fig. 7.10 - Foto 9 : Detalhe da periferia (I)

fig. 7.11 - Foto 10 : Detalhe da periferia (II)

fig. 7.12 - Foto 11 : Circuitos de E/S (I)

fig. 7.13 - Foto 12 : Circuitos de E/S (II)

## 8. Referências Bibliográficas

- [1] Saigo, T. et al., "A 20K-gate CMOS gate array", *IEEE Journal of Solid State Circuits*, SC-18(5), pp 578-584, Out. 83.

- [2] Ushiku, Y. et al., "An optimized 1.0 $\mu$ m CMOS technology for next generation channelless gate array", *IEEE Journal of Solid State Circuits*, SC-23(2), pp 507-513, Abr. 88.

- [3] Beunder, M. A. et al, "The CMOS Gate Forest: an efficient and flexible high-performance ASIC design environment", *IEEE Journal of Solid State Circuits*, SC-23(2), pp 387-399, Abr. 88.

- [4] Bennett, P. S. et al, "Embedded RAM in gate array: configurability and testability", *VLSI Systems Design*, 8(11), pp 60-66, Nov. 87.

- [5] Tago, H. et al., "A 6K CMOS gate array", *IEEE Journal of Solid State Circuits*, SC-17(5), pp 907-912, Out. 82.

- [6] Meyer, E. L., "Garnering gates in high density array", *VLSI Systems design*, Manhessel, N. Y., CMP Publ. Semicustom Design Guide 1988.

- [7] Blumberg, R. e Waggoner, C., "Aluminium screen gives superior power distribution in a sea-of-gates array", *VLSI Systems Design*, 9(2), pp 16-19, Fev. 1988.

- [8] Percival, R. e Fitchett, M., "Designing a laser-personalized gate array", *VLSI Systems Design*, 5(2), pp 54-61, Fev. 84.

- [9] Moullion, M., "Automatic customization for single-layer gate arrays", *VLSI Systems Design*, 5(11), pp 86-94, Nov. 84.

- [10] Reis, R. A. L., "Análise de circuitos VLSI", *Anais do VIII Congresso da SBC*, Rio de Janeiro, 17-22 Jul. 1988.

- [11] Weste, N. H. E. e Eshraghian, K., *Principles of CMOS VLSI Design*, Addison-Wesley Publishing, 1985.

- [12] Eshraghian, K. e Pucknell, D. A., *Basic VLSI Design*, Prentice Hall,

1988.

- [13] Glasser, L. A. e Dobberpuhl, D. W., *The Design and Analysis of VLSI Circuits*, Addison-Wesley Publishing, 1985.

- [14] Chua, S. J., "Current and resistivity dependence of electromigration from a statistical analysis of metallization failure data", *Solid State Electronics*, 1981.

- [15] Black, J. R., "Electromigration failure modes in aluminium metallization for semiconductor devices", *Proceedings of IEEE*, vol. 57, no. 9, Set. 69.

- [16] D'Heurle, F. M., "Electromigration and failure in electronics: an introduction", *Proceedings of IEEE*, vol. 59, no. 10, Out. 71.

- [17] National Semiconductor Corp., *Audio Radio Handbook*, 1978.