# DIGITAL ONE-CYCLE CONTROL TECHNIQUE WITH GRID VOLTAGE MEASUREMENT APPLIED TO THREE-PHASE POWER FACTOR CORRECTED RECTIFIERS AND ACTIVE POWER FILTERS

Armando José Gomes Abrantes Ferreira

Dissertação de Mestrado apresentada ao Programa de Pós-graduação em Engenharia Elétrica, COPPE, da Universidade Federal do Rio de Janeiro, como parte dos requisitos necessários à obtenção do título de Mestre em Engenharia Elétrica.

Orientadores: Luís Guilherme Barbosa Rolim Robson Francisco da Silva Dias

Rio de Janeiro Março de 2019

#### DIGITAL ONE-CYCLE CONTROL TECHNIQUE WITH GRID VOLTAGE MEASUREMENT APPLIED TO THREE-PHASE POWER FACTOR CORRECTED RECTIFIERS AND ACTIVE POWER FILTERS

#### Armando José Gomes Abrantes Ferreira

DISSERTAÇÃO SUBMETIDA AO CORPO DOCENTE DO INSTITUTO ALBERTO LUIZ COIMBRA DE PÓS-GRADUAÇÃO E PESQUISA DE ENGENHARIA (COPPE) DA UNIVERSIDADE FEDERAL DO RIO DE JANEIRO COMO PARTE DOS REQUISITOS NECESSÁRIOS PARA A OBTENÇÃO DO GRAU DE MESTRE EM CIÊNCIAS EM ENGENHARIA ELÉTRICA.

Examinada por:

Prof. Luís Guilherme Barbosa Rolim, Dr.-Ing

rof. Aluisio Alves de Melo Bento, D.Sc.

Prof. Maria Dias Bellar, Ph.D.

Ferreira, Armando José Gomes Abrantes

Digital One-Cycle Control Technique with Grid Voltage Measurement Applied to Three-Phase Power Factor Corrected Rectifiers and Active Power Filters/Armando José Gomes Abrantes Ferreira. – Rio de Janeiro: UFRJ/COPPE, 2019.

XXIV, 130 p.: il.; 29,7cm.

Orientadores: Luís Guilherme Barbosa Rolim

Robson Francisco da Silva Dias

Dissertação (mestrado) – UFRJ/COPPE/Programa de Engenharia Elétrica, 2019.

Referências Bibliográficas: p. 112 – 123.

1. Non-Linear-Control. 2. One-Cycle-Control. 3. Digital-Control. 4. Low-Cost. I. Rolim, Luís Guilherme Barbosa *et al.* II. Universidade Federal do Rio de Janeiro, COPPE, Programa de Engenharia Elétrica. III. Título.

To my Father, Who is always with me, Guiding me.

## Acknowledgements

To my mother Antonia and my daughter Fernanda, who are the most important people of my life, being my reference for past, present and future.

To my auntie/mother Tica and my little father Vagner for their huge heart and for being a safe harbor of love and careness during this time of my Master studies in Rio.

To my advisors, Prof. Rolim and Dias, for all the help and orientation during this time, providing me with out-of-box ideas and giving me opportunities for professional and personal growth.

To Profs. Aluisio Bento and Maria Bellar for the suggestions and orientation to elevate the level of this work.

To my colleagues and friends from Power Electronics Laboratory (ElePot-Coppe/UFRJ): Márcia Coelho, Lucas Gomes, Laís Crispino, Ryan Berriel, Lauro Ferreira and Sersan Guedes for the help with experiments, discussions on technical and philosophical issues and for the laughs during this time, that for sure made my work time much more pleasant and natural. Thank you for showing me the *ElePot Way of Life*: Do the Best You can in each Minimal thing You Do ("until you Know better").

To the friends/gifts life gave me: Vitória Aguiar, Yuri Macedo, Dênis Guedes and Rafael Fernandes for all the love, fondness and wisdom you gave me. I am carrying you guys all the time with me.

To all the musicians who played every single note I have listened to so far. What you do is just so important to keep me running on.

This study was financed in part by Coordenação de Aperfeiçoamento de Pessoal de Nível Superior - Brasil (CAPES) Finance Code 001.

To doubt everything and to believe everything are two equally convenient solutions; each saves us from thinking.

— Jules Henri Poincaré (1854 - 1912)

Resumo da Dissertação apresentada à COPPE/UFRJ como parte dos requisitos necessários para a obtenção do grau de Mestre em Ciências (M.Sc.)

TÉCNICA DE CONTROLE POR UM CICLO DIGITAL COM MEDIÇÕES DE TENSÃO DE REDE APLICADA A RETIFICADORES FATOR DE POTÊNCIA CONTROLADO E FILTROS ATIVOS DE POTÊNCIA TRIFÁSICOS

Armando José Gomes Abrantes Ferreira

Março/2019

Orientadores: Luís Guilherme Barbosa Rolim Robson Francisco da Silva Dias

Programa: Engenharia Elétrica

Considerando a demanda por melhorias nas cargas elétricas domésticas e industriais para atender às metas desafiadoras de satisfazer a demanda cada vez maior de energia elétrica e reduzir as emissões de gases de efeito estufa, o presente trabalho visa aplicar o Controle de Um Ciclo Digital (DOCC) com medição de tensão de rede para retificadores de fator de potência corrigida (PFC) e filtro ativo de potência (APF) trifásicos. O uso de tensão de rede é explorado em uma abordagem generalizada, definindo a influência dessas medições nas taxas de distorção harmônicas, fator de potência e limites de operação de carga. A compensação de queda de tensão indutiva e o uso de PWM Híbrido também são aplicados para melhorar o fator de potência e o uso do barramento CC. Resultados de simulação e experimentais da técnica OCC Digital aplicada a retificadores PFC e APF são apresentados, analisados e comparados com resultados experimentais e de simulação de técnicas convencionais para cada sistema.

Abstract of Dissertation presented to COPPE/UFRJ as a partial fulfillment of the requirements for the degree of Master of Science (M.Sc.)

# DIGITAL ONE-CYCLE CONTROL TECHNIQUE WITH GRID VOLTAGE MEASUREMENT APPLIED TO THREE-PHASE POWER FACTOR CORRECTED RECTIFIERS AND ACTIVE POWER FILTERS

Armando José Gomes Abrantes Ferreira

March/2019

Advisors: Luís Guilherme Barbosa Rolim Robson Francisco da Silva Dias

Department: Electrical Engineering

Considering the demand for improvements on domestic and industrial electrical loads to meet challenging goals of keeping up to an ever increasing demand of electrical energy and on the reduction of greenhouse gas emissions, the present work aims to apply the Digital One Cycle Control (DOCC) with grid voltage measurement to three-phase Power Corrected (PFC) Rectifier and Active Power Filter (APF). The use of grid voltage is explored in a generalized approach, by defining the influence of these measurements on harmonics, power factor and load limits. The compensation of inductive voltage drop and the use of Hybrid PWM are also applied to improve the power factor and the DC bus usage. Simulation and experimental results of the OCC digital technique applied to PFC and APF rectifiers are presented, analyzed and compared to simulation and experimental results of conventional technique for each system.

# Contents

| Li                        | ist of | Figure  | es                                              |     | xi    |

|---------------------------|--------|---------|-------------------------------------------------|-----|-------|

| Li                        | ist of | Tables  | s                                               | 3   | cviii |

| $\mathbf{L}\mathbf{i}$    | ist of | Abbre   | eviations                                       |     | xxi   |

| $\mathbf{L}_{\mathbf{i}}$ | ist of | Symbo   | ols                                             |     | xxii  |

| 1                         | Intr   | oducti  | ion                                             |     | 1     |

|                           | 1.1    | Backgr  | round of the Problem                            |     | 1     |

|                           | 1.2    | Cascao  | de Control of Converters                        |     | 3     |

|                           | 1.3    | Motiva  | ation                                           |     | 4     |

|                           | 1.4    | Object  | tives                                           |     | 5     |

|                           | 1.5    | Contri  | ibutions of the Dissertation                    |     | 5     |

|                           | 1.6    | Organ   | ization of the Dissertation                     |     | 6     |

|                           | 1.7    | Partial | l Conclusions                                   |     | 7     |

| 2                         | Rev    | iew on  | Active Compensation of Power Factor and Harmoni | ics | 8     |

|                           | 2.1    | Introd  | luction                                         |     | 8     |

|                           | 2.2    | PFC F   | Rectifiers                                      |     | 8     |

|                           |        | 2.2.1   | Classification                                  |     | 9     |

|                           |        | 2.2.2   | Review on Control of PFC Rectifiers             |     | 10    |

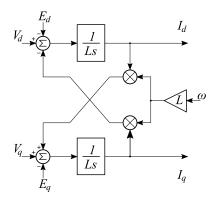

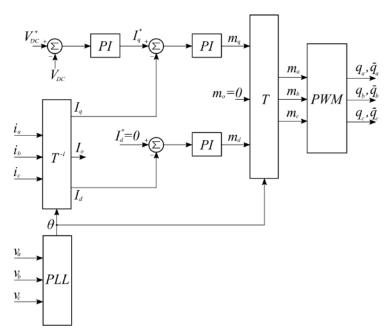

|                           |        | 2.2.3   | Control in dq-Frame for PFC Rectifiers          |     | 10    |

|                           |        |         | 2.2.3.1 Current Control Design                  |     | 13    |

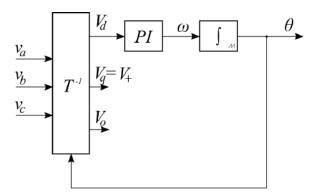

|                           |        |         | 2.2.3.2 PLL design                              |     | 15    |

|                           | 2.3    | APF     |                                                 |     | 16    |

|                           |        | 2.3.1   | Classification                                  |     | 16    |

|                           |        | 2.3.2   | Review on Control of Shunt APF                  |     | 18    |

|                           |        | 2.3.3   | pq-PWM Control for APF                          |     | 19    |

|                           |        |         | 2.3.3.1 PI Control                              |     | 20    |

|                           |        |         | 2.3.3.2 Hysteresis-Band                         |     | 21    |

|                           | 2.4    | Partia  | l Conclusions                                   |     | 21    |

| 3 | Rev | view on One Cycle Control                                       | <b>22</b> |

|---|-----|-----------------------------------------------------------------|-----------|

|   | 3.1 | Introduction                                                    | 22        |

|   | 3.2 | Analog OCC                                                      | 22        |

|   |     | 3.2.1 Resistor Emulation                                        | 27        |

|   | 3.3 | Single-Phase OCC                                                | 29        |

|   |     | 3.3.1 Unidirectional Rectifier                                  | 29        |

|   |     | 3.3.2 Bidirectional Rectifier                                   | 32        |

|   |     | 3.3.3 Grid Connected Inverter                                   | 33        |

|   | 3.4 | Digital OCC                                                     | 36        |

|   | 3.5 | Three-Phase OCC                                                 | 37        |

|   |     | 3.5.1 Bipolar OCC                                               | 37        |

|   |     | 3.5.2 Vector-Based OCC                                          | 40        |

|   |     | 3.5.3 OCC with Hybrid PWM                                       | 44        |

|   |     | 3.5.4 PFC Rectifier                                             | 46        |

|   |     | 3.5.5 Shunt APF                                                 | 47        |

|   | 3.6 | Feedforward Inductive Voltage Drop Compensation                 | 48        |

|   | 3.7 | Partial Conclusions                                             | 51        |

| 4 | Cor | ntributions and Discussion                                      | <b>52</b> |

|   | 4.1 | Introduction                                                    | 52        |

|   | 4.2 | Influence of Carrier Waveform on Stability of OCC Technique     | 52        |

|   |     | 4.2.1 Poincaré Maps                                             | 53        |

|   |     | 4.2.2 One-cycle Control with Triangular Carrier                 | 55        |

|   |     | 4.2.2.1 Mandatory Minimum Inductance                            | 61        |

|   | 4.3 | General Approach for Use of Grid Voltage Measurements in OCC $$ | 62        |

|   |     | 4.3.0.1 APF and PFC                                             | 67        |

|   |     | 4.3.0.2 GCI                                                     | 67        |

|   |     | 4.3.1 Three-Phase DOCC                                          | 68        |

|   | 4.4 | Frequency Analysis of Analog OCC                                | 70        |

|   | 4.5 | Frequency Analysis Digital OCC                                  | 73        |

|   | 4.6 | Improvements on Feedforward Inductive Voltage Drop Compensation | 76        |

|   | 4.7 | DOCC with HPWM                                                  | 78        |

|   | 4.8 | Partial Conclusions                                             | 80        |

| 5 | Sim | nulation Results of Medium Power Level Model                    | 82        |

|   | 5.1 | Introduction                                                    | 82        |

|   | 5.2 | Three-Phase PFC                                                 | 82        |

|   |     | 5.2.1 Conventional dq-PWM                                       | 83        |

|   |     | 5.2.2 DOCC                                                      | 84        |

|   |     | 5.2.2.1 DOCC with Grid Voltage Measurement                      | 85        |

|              |       |             | 5.2.2.2 DOCC with Feed-forward Inductive Voltage Drop |       |

|--------------|-------|-------------|-------------------------------------------------------|-------|

|              |       |             | Compensation                                          | . 86  |

|              |       |             | 5.2.2.3 DOCC with HPWM                                | . 87  |

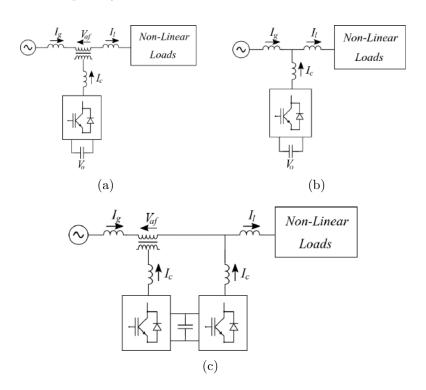

|              | 5.3   | Three-      | -Phase Shunt APF                                      | . 88  |

|              |       | 5.3.1       | Conventional pq-PWM                                   | . 90  |

|              |       |             | 5.3.1.1 Hysteresis Current Control                    | . 90  |

|              |       |             | 5.3.1.2 PI Current Control                            | . 90  |

|              |       | 5.3.2       | DOCC                                                  | . 91  |

|              |       | 5.3.3       | Comparative Analysis                                  | . 93  |

|              | 5.4   | Partia      | d Conclusions                                         | . 95  |

| 6            | Mo    | del Va      | lidation and Experimental Results                     | 96    |

|              | 6.1   | Introd      | luction                                               | . 96  |

|              | 6.2   |             | Power Level Setup                                     |       |

|              | 6.3   |             | ations $\dots$                                        |       |

|              |       | 6.3.1       | Three-Phase PFC                                       |       |

|              |       |             | 6.3.1.1 dq-PWM Control                                | . 99  |

|              |       |             | 6.3.1.2 DOCC                                          |       |

|              |       | 6.3.2       | APF                                                   | . 100 |

|              |       |             | 6.3.2.1 pq-PWM Control                                |       |

|              |       |             | 6.3.2.2 DOCC                                          |       |

|              | 6.4   | Exper       | imental                                               |       |

|              |       | 6.4.1       | PFC                                                   |       |

|              |       |             | 6.4.1.1 dq-PWM Control                                | . 102 |

|              |       |             | 6.4.1.2 DOCC Strategies                               |       |

|              |       | 6.4.2       |                                                       |       |

|              |       |             | 6.4.2.1 DOCC Strategies                               | . 106 |

|              | 6.5   | Analy       | $\mathrm{sis}$                                        |       |

|              | 6.6   |             | d Conclusions                                         |       |

| 7            | Ger   | neral C     | Conclusions and Future works                          | 110   |

| ъ.           | 1 10  |             |                                                       | 110   |

| Bı           | gorld | graphy      |                                                       | 112   |

| $\mathbf{A}$ |       | ndards<br>- |                                                       | 124   |

|              |       |             | ean Standard EN 61000-3-2                             |       |

|              | A.2   | IEEE        | 519-2014                                              | . 125 |

| В            | Dec   | luction     | n of the Dynamic Model                                | 127   |

# List of Figures

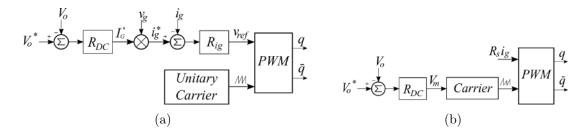

| 1.1  | Schematics of Cascade Control Techniques for Converters: (a) Conventional Current Mode PI Control, (b) Current Mode One-Cycle |    |

|------|-------------------------------------------------------------------------------------------------------------------------------|----|

|      | Control                                                                                                                       | 3  |

| 1.2  | Schematics of Digital OCC Technique.                                                                                          | 4  |

| 1.3  | Schematic of Analog OCC with Grid Voltage Measurement                                                                         | 5  |

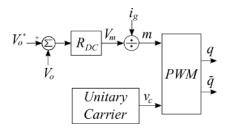

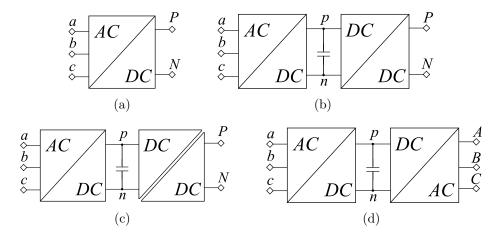

| 2.1  | Schematics of Typical Converter Arrangement for Supplying Electri-                                                            |    |

|      | cal Loads From Three-Phase AC Utility: (a) AC-DC Conversion, (b)                                                              |    |

|      | AC-DC-DC Conversion with Non-Isolated DC-DC Converter, (c) AC-                                                                |    |

|      | DC-DC Conversion with Isolated DC-DC Converter, (d) AC-DC-DC                                                                  |    |

|      | (Back-to-Back) Conversion                                                                                                     | 9  |

| 2.2  | Classification of Rectifiers Based on Energy Flow Direction and Con-                                                          |    |

|      | verter Topology                                                                                                               | 9  |

| 2.3  | Space Vector of a Generic Three-Phase Set of Variables in Static abc                                                          |    |

|      | and Rotating dq Reference Frames                                                                                              | 11 |

| 2.4  | Block Diagram for dq Currents for Control in dq-Frame of PFC Rec-                                                             |    |

|      | tifiers                                                                                                                       | 13 |

| 2.5  | Block Diagram of Control in dq-Frame for Three-Phase Full-Bridge                                                              |    |

|      | PFC Rectifier                                                                                                                 | 13 |

| 2.6  | Block Diagram of Current Loop Control for Control in dq-Frame of                                                              |    |

|      | PFC Rectifiers                                                                                                                | 13 |

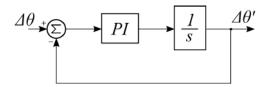

| 2.7  | Block Diagram of d-PLL                                                                                                        | 15 |

| 2.8  | Block Diagram of d-PLL - Small Signal Model                                                                                   | 15 |

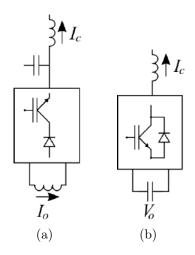

| 2.9  | APF Classification based on Converter Type: (a) CSI-based APF (b)                                                             |    |

|      | VSI-based APF                                                                                                                 | 17 |

| 2.10 | APF System Topologies: (a) Shunt APF, (b) Series APF (b) Shunt-                                                               |    |

|      | Series APF - Unified Power Quality Conditioner - UPQC                                                                         | 17 |

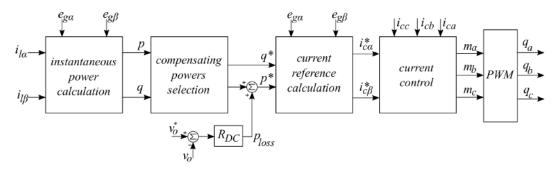

| 2.11 | Block Diagram of pq-PWM APF                                                                                                   | 20 |

|      | Hysteresis Control Principle                                                                                                  |    |

| 3.1  | Generic Switch: (a) Schematics, (b) Switching Pattern                                                                         | 23 |

| 3.2  | Pulse-Width Modulation Technique Principle                            | 24 |

|------|-----------------------------------------------------------------------|----|

| 3.3  | Generation of Output Pulse with PWM Technique                         | 24 |

| 3.4  | OCC Modulation Operation: Switch Input, Carrier, Switch Gate Sig-     |    |

|      | nal and Switch Output                                                 | 26 |

| 3.5  | Implementation Circuitry for OCC                                      | 27 |

| 3.6  | The Principle the Resistor Emulator Approach for Control of a Single- |    |

|      | Phase Converter                                                       | 27 |

| 3.7  | Generalized PWM Circuit - Adapted from [1]                            | 28 |

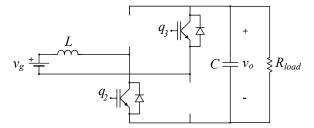

| 3.8  | Model of Single Phase Unidirectional Boost Rectifier                  | 30 |

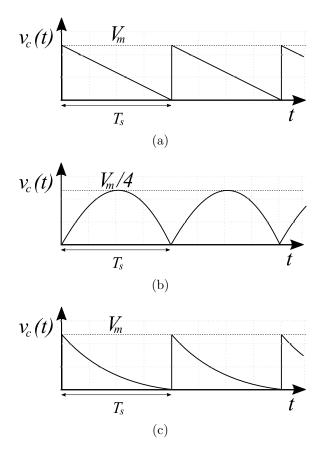

| 3.9  | Carriers of Control with Unipolar OCC: (a) Average Inductor Cur-      |    |

|      | rent, (b) Average Switch Current and (c) Average Diode Current        | 31 |

| 3.10 | Schematic of Unipolar OCC with Resistor Emulator with Average         |    |

|      | Inductor Current                                                      | 31 |

| 3.11 | Single-Phase Unidirectional Boost Rectifier with OCC: Input Voltage   |    |

|      | (5 V/div.) and Input Current (1 A/div.)                               | 32 |

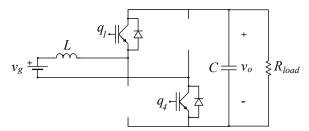

| 3.12 | Model of Single-Phase Bidirectional Boost Rectifier                   | 32 |

| 3.13 | Bipolar OCC: (a) Schematic (b) Sawtooth Carrier Waveform              | 33 |

| 3.14 | Single-Phase Bidirectional Boost Rectifier with OCC: Input Voltage    |    |

|      | (5 V/div.) and Input Current (1 A/div.)                               | 34 |

| 3.15 | Model of Single-Phase Grid Connected Inverter                         | 34 |

| 3.16 | Block Diagram of OCC with Voltage Measurement for Single-Phase        |    |

|      | Grid Connected Inverter                                               | 35 |

| 3.17 | Block Diagram of OCC with no Voltage Measurement for Single-          |    |

|      | Phase Grid Connected Inverter                                         | 35 |

| 3.18 | Grid Connected Inverter with OCC: Input Voltage (5 V/div.) and        |    |

|      | Input Current (1 A/div.)                                              | 36 |

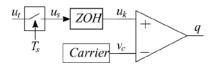

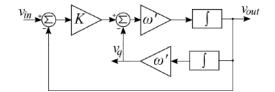

| 3.19 | Block Diagram of DOCC Technique                                       | 37 |

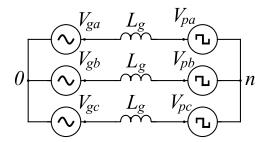

| 3.20 | Three-Phase Full-Bridge Converter Connected to a Three-Phase Grid     |    |

|      | - General Model                                                       | 38 |

| 3.21 | Two level three phase full bridge rectifier - Average Model           | 38 |

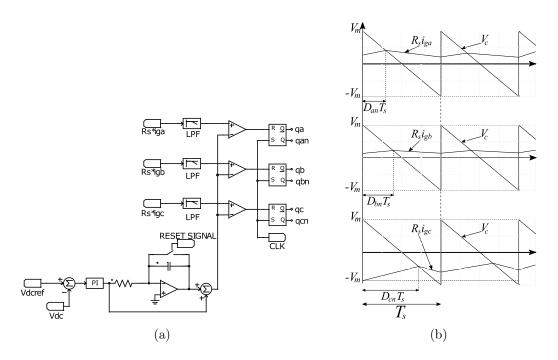

| 3.22 | Analog Implementation of OCC to three-phase Converter operating       |    |

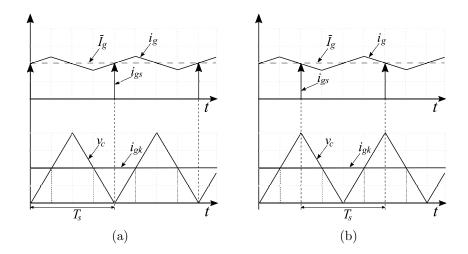

|      | as PFC or APF: (a) Implementation Circuitry, (b) Waveforms            | 41 |

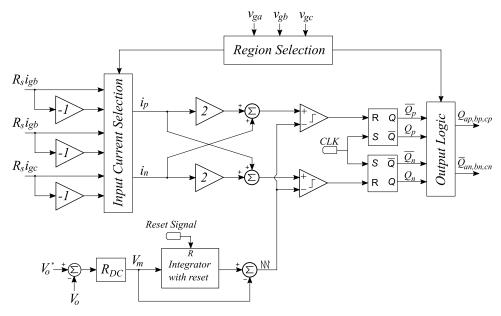

| 3.23 | Control Schematics for OCC with Vector Operation                      | 42 |

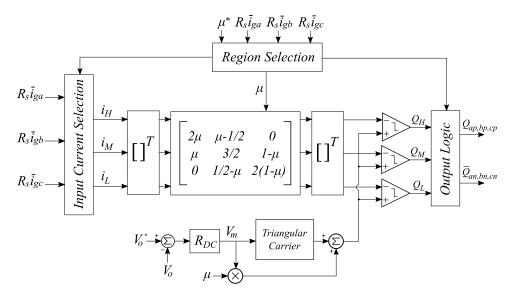

| 3.24 | Control Schematics for Generalized Analog Vector-Based OCC for        |    |

|      | Two Level Converters with $\mu$                                       | 43 |

| 3.25 | Control Schematics for Generalized Analog Hybrid PWM OCC with         |    |

|      | Linear Carrier                                                        | 45 |

| 3.26 | Control Schematics for Generalized Analog Hybrid PWM OCC with         |    |

|      | Non-Linear Carrier                                                    | 45 |

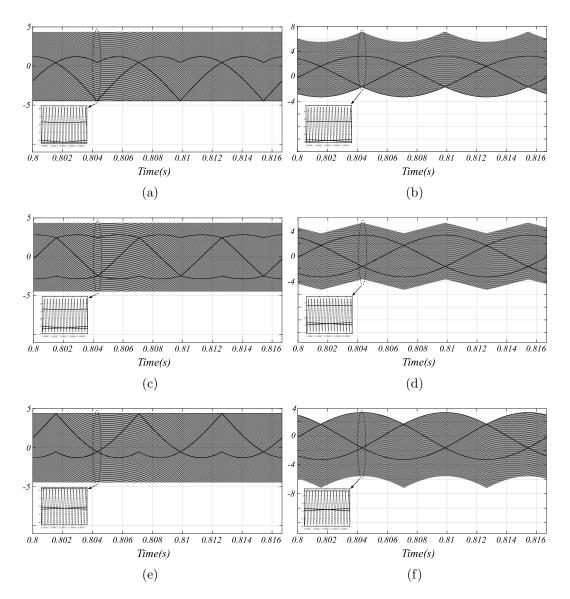

| 3.27 | Modulation Signals for Generalized Analog Hybrid PWM OCC. Right                   |    |

|------|-----------------------------------------------------------------------------------|----|

|      | Column - Linear Carrier: (a) $\mu = 0$ , (c) $\mu = 0.5$ , (e) $\mu = 1.0$ . Left |    |

|      | Column - Non-Linear Carrier: (b) $\mu = 0$ , (d) $\mu = 0.5$ , (f) $\mu = 1.0$    | 46 |

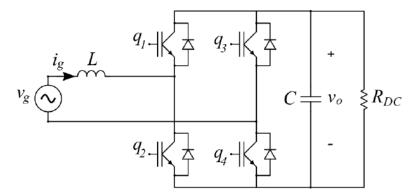

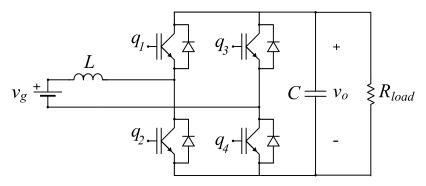

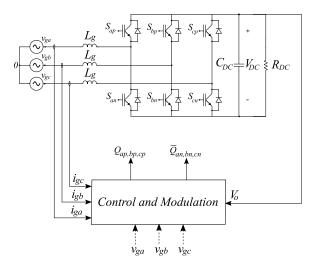

| 3.28 | Three-Phase Full-Bridge PFC Rectifier - General Model                             | 47 |

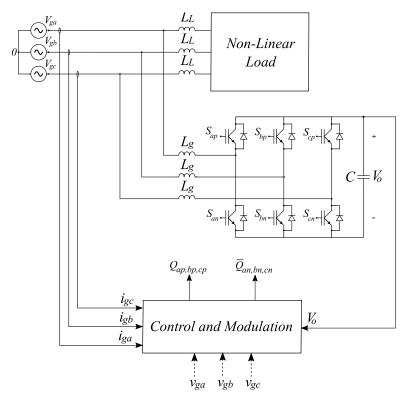

| 3.29 | Three-Phase Full-Bridge Shunt APF - General Model                                 | 48 |

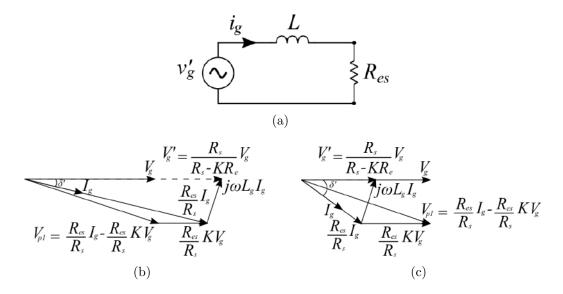

| 3.30 | Equivalent RL Circuit for Converter with OCC with Resistor Emu-                   |    |

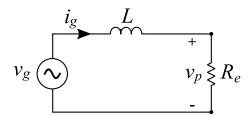

|      | lator Approach                                                                    | 49 |

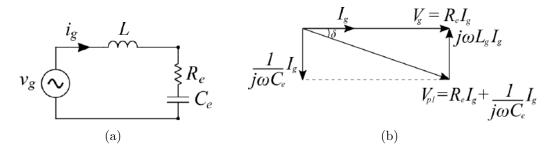

| 3.31 | Phasor Diagram of Equivalent RL circuit of Single-Phase Bidirec-                  |    |

|      | tional Rectifier controlled by OCC with Resistor Emulator Approach.               | 49 |

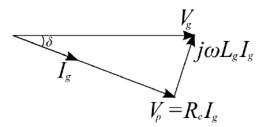

| 3.32 | Feed-Forward Inductive Voltage Drop Compensation: (a) General                     |    |

|      | Block Diagram, (b) Block Diagram of the $90^{\circ}$ Phase Lag Shifter -          |    |

|      | Adapted from [2]                                                                  | 51 |

| 3.33 | Feed-Forward Inductive Voltage Drop Compensation: (a) RLC                         |    |

|      | Equivalent circuit, (b) Phasor Diagram with Inductive Voltage Drop                |    |

|      | Compensation                                                                      | 51 |

|      |                                                                                   |    |

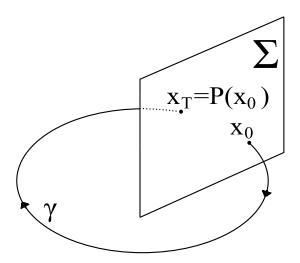

| 4.1  | Poincaré Map and Boundary Value Condition - Adapted from [3]                      | 53 |

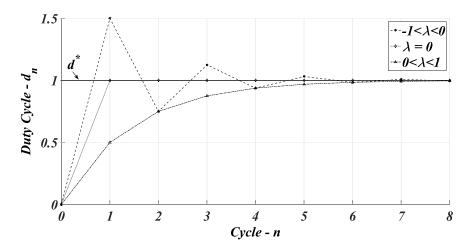

| 4.2  | Duty-Cycle Convergence of Convergent Mapping Systems                              | 54 |

| 4.3  | Model of DC-DC Full-Bridge Boost Converter                                        | 55 |

| 4.4  | DC-DC Full-Bridge Boost Converter with OCC - Waveforms of Mea-                    |    |

|      | sured Current and Triangular Carrier During Transient                             | 55 |

| 4.5  | DC-DC Full-Bridge Boost Converter with OCC - Waveforms of First                   |    |

|      | Equalizing Path of Measured Current and Triangular Carrier During                 |    |

|      | Transient                                                                         | 56 |

| 4.6  | DC-DC Full-Bridge Boost Converter with OCC - Waveforms of Sec-                    |    |

|      | ond Equalizing Path of Measured Current and Triangular Carrier                    |    |

|      | During Transient                                                                  | 57 |

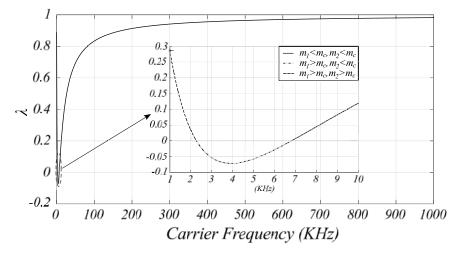

| 4.7  | Behavior of $\lambda$ with Variation of Inductance $L$ for OCC with Triangular    |    |

|      | Carrier                                                                           | 59 |

| 4.8  | Behavior $\lambda$ with Variation of Switching Frequency $f_s$ for OCC with       |    |

|      | Triangular Carrier                                                                | 59 |

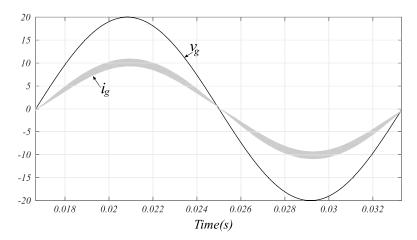

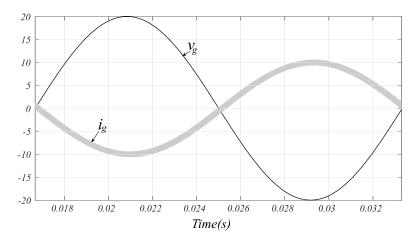

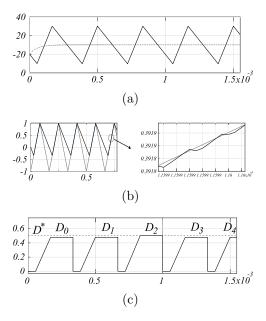

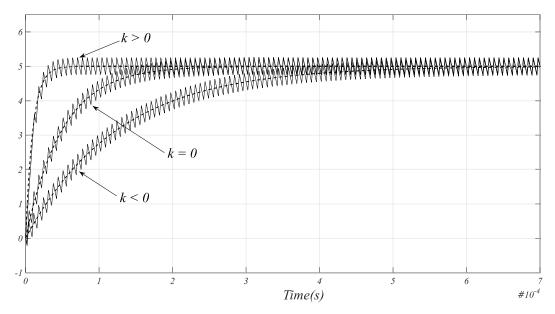

| 4.9  | Converter response for $\lambda=0.5$ : Input current (black) and reference        |    |

|      | current from equivalent RL circuit (grey). (b) Behavior of duty-cycle             |    |

|      | over time. (c) Carrier (grey), current (black)                                    | 60 |

| 4.10 | Converter Response for $\lambda=0$ . (a) Input Current (Solid) and Ref-           |    |

|      | erence Current from Equivalent RL Circuit (Dashed), (b) Carrier                   |    |

|      | (Grey), Current (black), (c) Behavior of Duty-Cycle Over Time                     | 61 |

| 4.11 | Converter Response for $\lambda < 0$ . (a) Input Current (Solid) and Ref- |    |

|------|---------------------------------------------------------------------------|----|

|      | erence Current from Equivalent RL Circuit (Dashed), (b) Carrier           |    |

|      | (Grey), Current (Black), (c) Behavior of Duty-Cycle Over Time             | 62 |

| 4.12 | Block Diagram of OCC with Grid Voltage Measurement: (a) Analog            |    |

|      | Implementation (b) Digital Implementation                                 | 64 |

| 4.13 | (a) Modified RL equivalent circuit; Phasor Diagram FOCC with (b)          |    |

|      | k > 0; (c) $k < 0$                                                        | 65 |

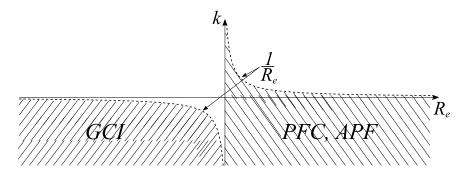

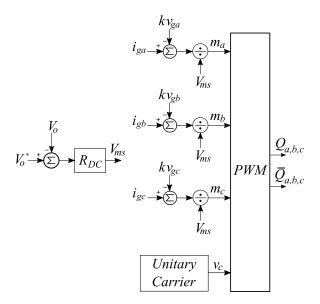

| 4.14 | Step Responses for Input Current of a DC-DC Converter Controlled          |    |

|      | by OCC with $k = 0$ (Conventional OCC), $k > 0$ (Faster Response)         |    |

|      | and $k < 0$ (Slower Response) (1 A/div.)                                  | 66 |

| 4.15 | Operation Ranges of $k$ and $R_e$ in APF, PFC and GCI Operating Modes.    | 66 |

| 4.16 | Schematic of Implementation of DOCC with Grid Voltage Measure-            |    |

|      | ment                                                                      | 69 |

| 4.17 | Model of Single-phase Full-Bridge with OCC                                | 70 |

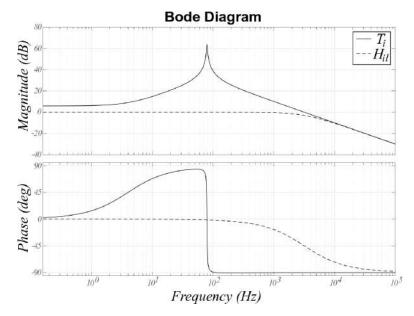

| 4.18 | Small Signal Block Diagram of OCC                                         | 71 |

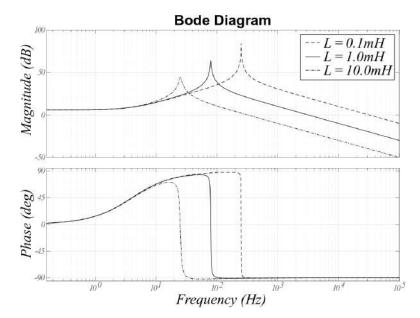

| 4.19 | Bode plot - Current Loop Gain for Full-Bridge Boost Converter with        |    |

|      | Load and for RL circuit response                                          | 72 |

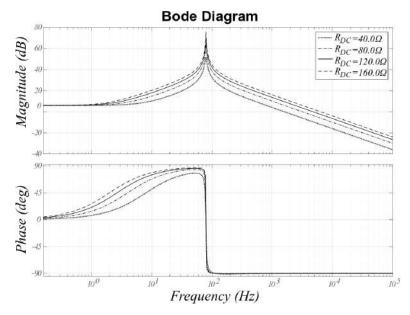

| 4.20 | Bode Plot - Variation of Current Loop Gain for Full-Bridge Boost          |    |

|      | Converter with Load Variation                                             | 73 |

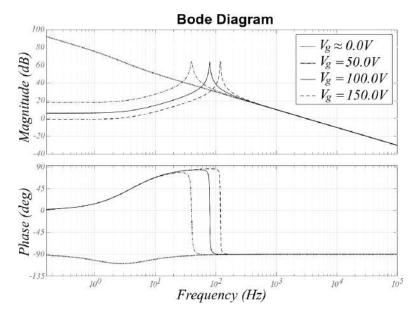

| 4.21 | Bode plot - Variation of Current Loop Gain for Full-Bridge Boost          |    |

|      | Converter with Input Voltage                                              | 74 |

| 4.22 | Bode plot - Variation of Current Loop Gain for Full-Bridge Boost          |    |

|      | Converter with Input DC-Bus Capacitance Variation                         | 75 |

| 4.23 | Bode plot - Variation of Current Loop Gain for Full-Bridge Boost          |    |

|      | Converter with Inductance Variation                                       | 76 |

| 4.24 | Instantaneous Inductor Current with Constant Input and Output             |    |

|      | Voltage                                                                   | 76 |

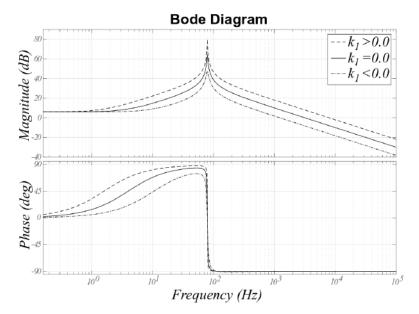

| 4.25 | Bode plot - Variation of Current Loop Gain for Full-Bridge Boost          |    |

|      | Converter with OCC with Grid Voltage Measurement                          | 77 |

| 4.26 | Sampling Strategy for Inductor Current of Symmetrical Modulation          |    |

|      | PWM: (a) Valley Point Instant, (a) Peak Point Instant                     | 77 |

| 4.27 | General Model for Uniformly-Sampled PWM Modulator                         | 78 |

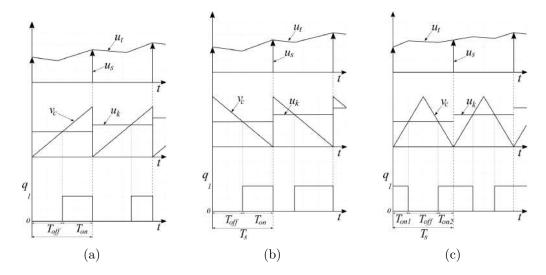

| 4.28 | Uniformly sampled Pulse Width Modulators: (a) Trailing Edge Saw-          |    |

|      | tooth Carrier, (b) Leading Edge Sawtooth Carrier (c) Symmetrical          |    |

|      | Triangular Carrier                                                        | 78 |

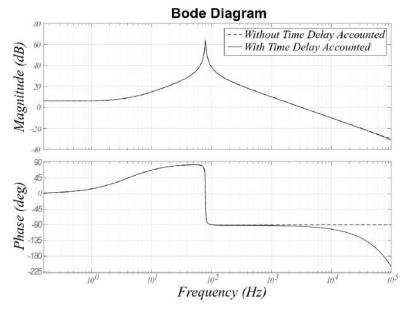

| 4.29 | Small Signal Block Diagram - Digital OCC                                  | 79 |

| 4.30 | Bode plot - Influence of Time Delay Accounted to the Model                | 79 |

| 4.31 | SOGI Schematic                                                            | 80 |

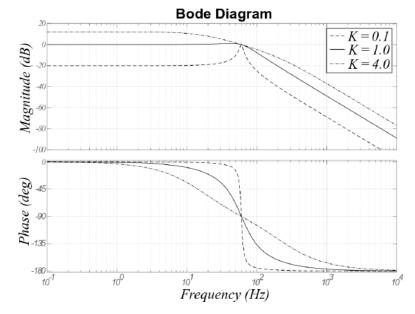

| 4.32 | Bode Plot - SOGI Dynamics with Variation of Gain $K$                      | 80 |

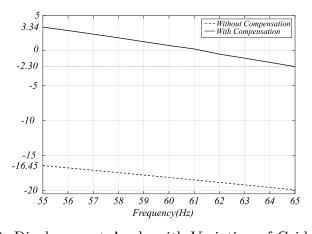

| 4.33 | Displacement Angle with Variation of Grid Frequency                                                                                                                                                                                                       | 80  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1  | Circuit Schematics of Model of Medium Power Level Three-Phase Full-Bridge PFC Rectifier                                                                                                                                                                   | 83  |

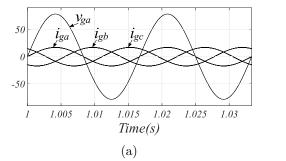

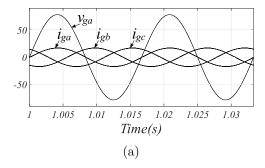

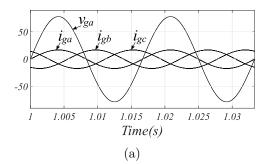

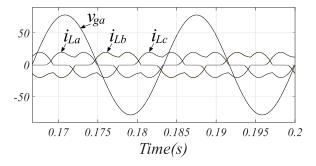

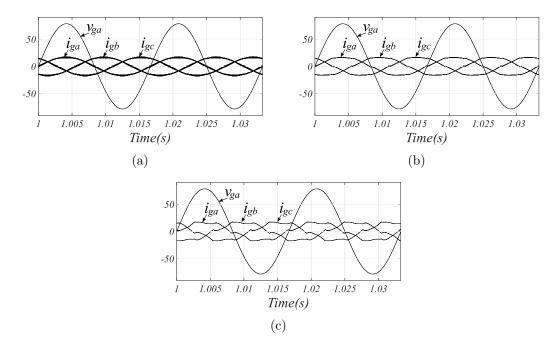

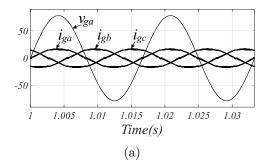

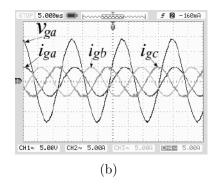

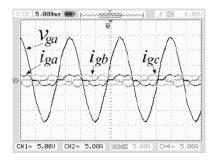

| 5.2  | Simulation Results for Medium Power Level Three-Phase Full-Bridge PFC Rectifier Model with Standard dq-PWM Control - Phase Voltage a (5 V/div.) and Phase Currents (1 A/div.): (a) $L_g = 3.48mH$ , (b)                                                   |     |

| 5.3  | $L_g=12.51mH.$                                                                                                                                                                                                                                            | 84  |

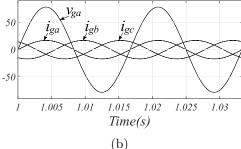

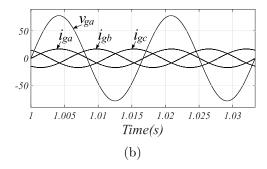

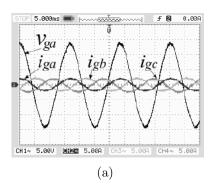

| 5.4  | Phase Currents (1 A/div.): (a) $L_g=3.48mH$ , (b) $L_g=12.51mH$ Simulation Results for Medium Power Level Three-Phase Full-Bridge                                                                                                                         | 85  |

|      | PFC Rectifier Model with DOCC With Grid Voltage Measurement for $k = 0.025$ (faster) - Phase Voltage a (5 V/div.) and Phase Currents                                                                                                                      | or. |

| 5.5  | (1 A/div.): (a) $L_g = 3.48mH$ , (b) $L_g = 12.51mH$                                                                                                                                                                                                      | 85  |

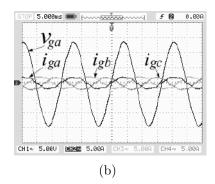

| 5.6  | Currents (1 A/div.): (a) $L_g = 3.48mH$ , (b) $L_g = 12.51mH$ Simulation Results for Medium Power Level Three-Phase Full-Bridge PFC Rectifier Model with DOCC With Feed-forward Inductive Voltage Prop. Compared in Phase voltage a (5 V/div.) and Phase  | 86  |

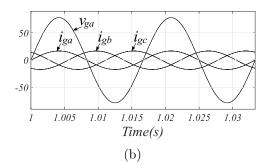

| 5.7  | age Drop Compensation - Phase voltage a (5 V/div.) and Phase Currents (1 A/div.): (a) $L_g = 3.48mH$ , (b) $L_g = 12.51mH$ Simulation Results for Medium Power Level Three-Phase Full-Bridge PFC Rectifier Model - Modulation Signals for DOCC with HPWM: | 87  |

| 5.8  | (a) $\mu = 0.5$ , (b) with $\mu = 0.0$ , (c) $\mu = 1.0$                                                                                                                                                                                                  | 87  |

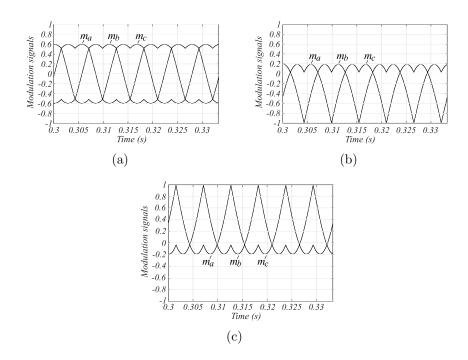

| 5.9  | Full-Bridge Shunt APF                                                                                                                                                                                                                                     | 88  |

|      | Model with Standard pq-PWM with PI Current Control - Phase voltage a (5 V/div.) and Phase Currents (1 A/div.): Non-Linear Load Current                                                                                                                    | 89  |

| 5.10 |                                                                                                                                                                                                                                                           |     |

|      | 3.48 $mH$ , (b) $L_g = 12.51 mH$                                                                                                                                                                                                                          | 90  |

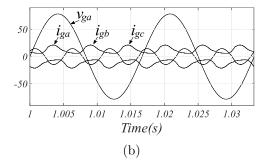

| 5.11  | Simulation Results for Medium Power Level Three-Phase Shunt APF                                                                 |     |

|-------|---------------------------------------------------------------------------------------------------------------------------------|-----|

|       | Model with Standard pq-PWM with PI Current Control - Phase volt-                                                                |     |

|       | age a (5 V/div.) and Phase Currents (1 A/div.): (a) $L_g = 3.48mH$ ,                                                            | 0.1 |

|       | (b) $L_g = 12.51mH$                                                                                                             | 91  |

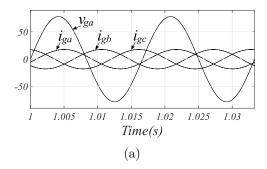

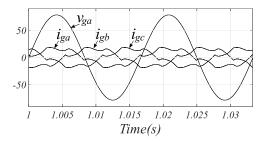

| 5.12  | Simulation Results for Medium Power Level Three-Phase Shunt APF                                                                 |     |

|       | Model with DOCC - Phase voltage a (5 V/div.) and Phase Currents                                                                 |     |

|       | $(1 \text{ A/div.})$ : (a) $L_g = 3.48mH$ , (b) $L_g = 12.51mH$                                                                 | 92  |

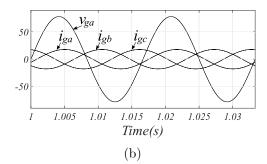

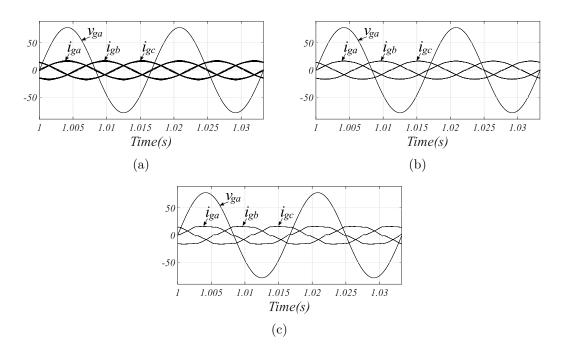

| 5.13  | Simulation Results for Medium Power Level Three-Phase Shunt APF                                                                 |     |

|       | Model with DOCC With Grid Voltage Measurement for $k = 0.0159$                                                                  |     |

|       | (faster) - Phase voltage a (5 V/div.) and Phase Currents (1 A/div.):                                                            |     |

| 5 1 1 | (a) $L_g = 3.48mH$ , (b) $L_g = 12.51mH$                                                                                        | 92  |

| 0.14  | Simulation Results for Medium Power Level Three-Phase Shunt APF  Model with DOCC With Crid Voltage Measurement for k = 0.0217   |     |

|       | Model with DOCC With Grid Voltage Measurement for $k = 0.0317$                                                                  |     |

|       | (faster) - Phase voltage a (5 V/div.) and Phase Currents (1 A/div.):                                                            | 02  |

| E 1E  | (a) $L_g = 3.48mH$ , (b) $L_g = 12.51mH$                                                                                        | 93  |

| 5.15  |                                                                                                                                 |     |

|       | Model with DOCC With Grid Voltage Measurement for $k = -0.0159$                                                                 |     |

|       | (slower) - Phase voltage a (5 V/div.) and Phase Currents (1 A/div.):                                                            | 0.4 |

|       | (a) $L_g = 3.48mH$ , (b) $L_g = 12.51mH$                                                                                        | 94  |

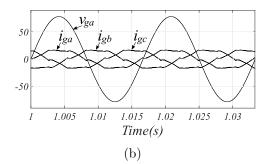

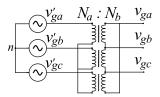

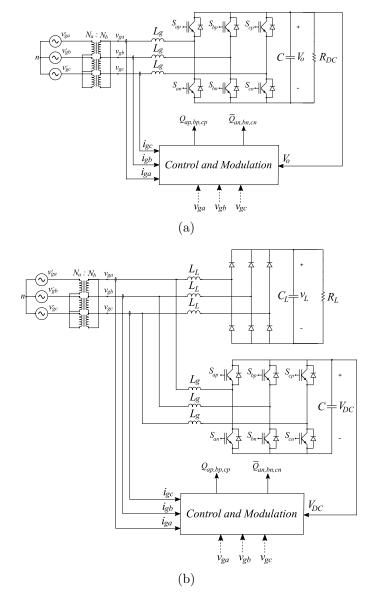

| 6.1   | Three-Phase Step-up Transformer Arrangement for Low Scale Setup.                                                                | 97  |

| 6.2   | Circuit Schematics of Medium Power Level Three-Phase Models: (a)                                                                |     |

|       | Full-Bridge PFC Rectifier, (b) Shunt APF                                                                                        | 98  |

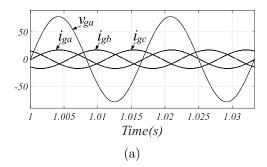

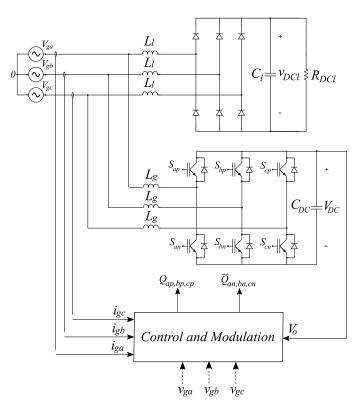

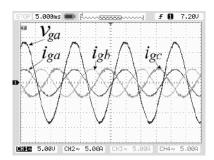

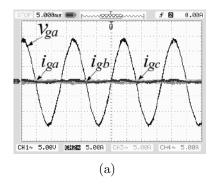

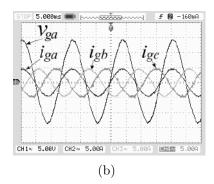

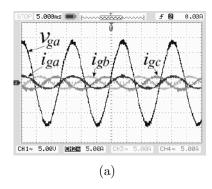

| 6.3   | Experimental Results Low Power Level Three-Phase Full-Bridge PFC                                                                |     |

|       | Rectifier with Standard dq-PWM Control - Phase voltage a (5 V/div.)                                                             |     |

|       | and Phase Currents (5 A/div.): $L_g = 600 \mu H.$                                                                               | 102 |

| 6.4   | Experimental Results Low Power Level Three-Phase Full-Bridge PFC                                                                |     |

|       | Rectifier with DOCC - Phase voltage a (5 $V/div.$ ) and Phase Currents                                                          |     |

|       | (5 A/div.): (a) $L_g = 600 \mu H$ ., (b) $L_g = 2.13 mH$                                                                        | 103 |

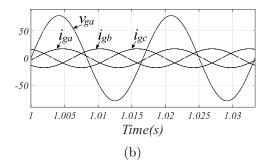

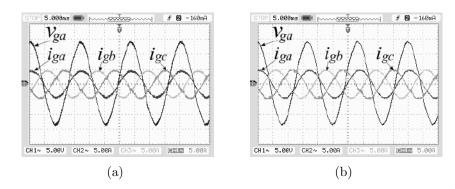

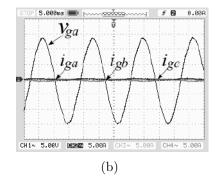

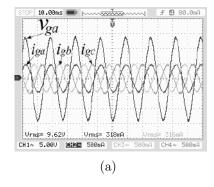

| 6.5   | Experimental Results Low Power Level Three-Phase Full-Bridge PFC                                                                |     |

|       | Rectifier with DOCC with Grid Voltage Measurement for $k=0.015$                                                                 |     |

|       | (faster)- Phase voltage a (5 V/div.) and Phase Currents (5 A/div.):                                                             |     |

|       | $L_g = 600\mu H.  \dots $ | 103 |

| 6.6   | Experimental Results Low Power Level Three-Phase Full-Bridge PFC                                                                |     |

|       | Rectifier with DOCC with Grid Voltage Measurement for $k = -0.015$                                                              |     |

|       | (slower) - Phase Voltage a (5 V/div.) and Phase Currents (5 A/div.):                                                            |     |

|       | (a) $L_g = 600 \mu H$ , (b) $L_g = 2.13 m H$                                                                                    | 104 |

|       | \ / B                                                                                                                           |     |

| 6.7  | Experimental Results Low Power Level Three-Phase Full-Bridge PFC                                                            |     |

|------|-----------------------------------------------------------------------------------------------------------------------------|-----|

|      | Rectifier with DOCC with Grid Voltage Measurement for $k=-0.015$                                                            |     |

|      | (slower) at null load operating point - Phase Voltage a (5 $V/div.$ ) and                                                   |     |

|      | Phase Currents (5 A/div.): (a) $L_g = 600 \mu H$ , $L_g = L_g = 2.13 H$                                                     | 104 |

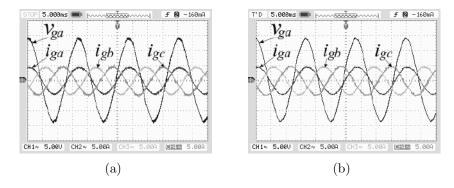

| 6.8  | Experimental Results Low Power Level Three-Phase Full-Bridge PFC                                                            |     |

|      | Rectifier with DOCC with Feed-forward Inductive Drop Compensa-                                                              |     |

|      | tion - Phase voltage a (5 V/div.) and Phase Currents (5 A/div.): $L_g$                                                      |     |

|      | $= 600 \mu H. \dots $ | 105 |

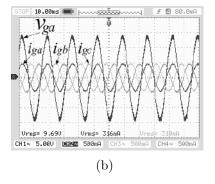

| 6.9  | Experimental Results Low Power Level Three-Phase Full-Bridge PFC                                                            |     |

|      | Rectifier with DOCC with Hybrid PWM - Phase voltage a (5 V/div.)                                                            |     |

|      | and Phase Currents (5 A/div.): (a) $\mu = 0.5$ , (b) $\mu = 0.99$                                                           | 105 |

| 6.10 | Experimental Results Low Power Level Three-Phase Full-Bridge PFC                                                            |     |

|      | Rectifier with DOCC with Hybrid PWM - Phase Current a (10                                                                   |     |

|      | A/div.) and Switch Gating Signals (5 V/div.): (a) Conventional,                                                             |     |

|      | (b) $\mu = 0.5$ , (c) $\mu = 0.99$                                                                                          | 106 |

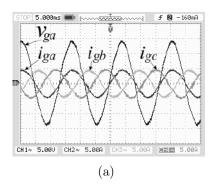

| 6.11 | Experimental Results non-linear load without APF: Grid Phase Volt-                                                          |     |

|      | age a (5 V/div.) and Grid Phase Currents (5 A/div.)                                                                         | 106 |

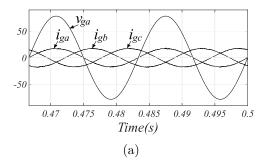

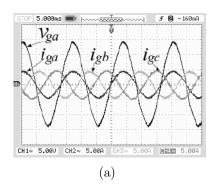

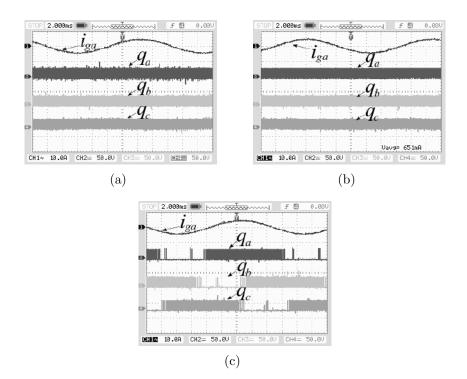

| 6.12 | Experimental Results Low Power Level Three-Phase Shunt APF with                                                             |     |

|      | DOCC - Phase Voltage a (5 V/div.) and Phase Currents (5 A/div.):                                                            |     |

|      | (a) $L_g = 600 \mu H$ , (b) $L_g = 2.13 mH$                                                                                 | 107 |

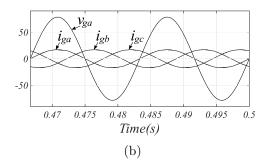

| 6.13 | Experimental Results Low Power Level Three-Phase Shunt APF with                                                             |     |

|      | DOCC with Grid Voltage Measurement for $k = 0.05$ (faster)- Phase                                                           |     |

|      | Voltage a (5 V/div.) and Phase Currents (5 A/div.): (a) $L_g = 600 \mu H$ ,                                                 |     |

|      | (b) $L_g = 2.13mH$                                                                                                          | 107 |

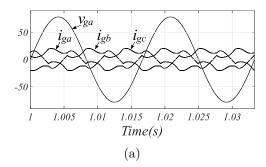

| 6.14 | Experimental Results Low Power Level Three-Phase Shunt APF with                                                             |     |

|      | DOCC with Voltage Measurement with $k = -0.594667$ (slower) -                                                               |     |

|      | Phase Voltage a (5 V/div.) and Phase Currents (5 A/div.): (a) $L_g =$                                                       |     |

|      | $600\mu H$ , (b) $L_g = 2.13mH$                                                                                             | 108 |

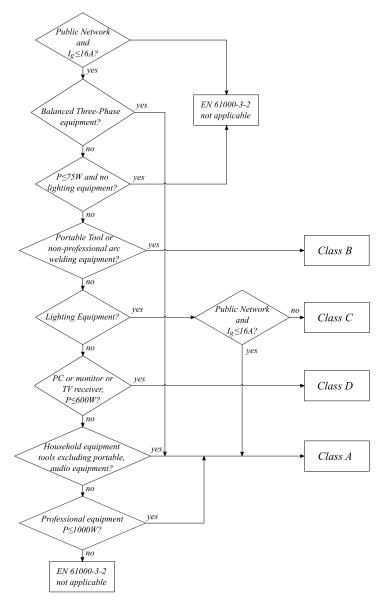

| A.1  | Flow Chart for Classification of Electrical Equipment according to                                                          |     |

|      | Standard EN 61000-3-2                                                                                                       | 125 |

|      |                                                                                                                             | -3  |

| B.1  | Operation Configurations for bipolar PWM operation mode of the                                                              |     |

|      | Full-Bridge Single-Phase Converter                                                                                          | 127 |

## List of Tables

| 1.1 | European Standard IEC 61000-3-2: Classes of Equipments $\ \ldots \ \ldots$                      | 2  |

|-----|-------------------------------------------------------------------------------------------------|----|

| 1.2 | Solution for Harmonics Issues                                                                   | 2  |

| 3.1 | Solution candidates for resistance emulation control goal for Unidi-                            |    |

|     | rectional DC-DC Boost                                                                           | 30 |

| 3.2 | Vector-based OCC - Summarization of Input Control Parameters According to Line Cycle Region [4] | 41 |

| 3.3 | Generalized Vector-based OCC - Summarization of Input Control Pa-                               | 41 |

| 5.5 | rameters According to Line Cycle Region [5]                                                     | 44 |

| 4.1 | Operating Point Parameters of a current loop gain for Single-phase                              |    |

|     | Full-Bridge OCC controlled converter                                                            | 72 |

| 4.2 | Laplace-Domain models for Uniformly-Sampled Pulse-Width Modu-                                   |    |

|     | lators                                                                                          | 75 |

| 5.1 | Parameters for Simulations of Medium Power Level Three-Phase Full-                              |    |

|     | Bridge PFC Rectifier Model                                                                      | 83 |

| 5.2 | Simulation Results for Medium Power Level Three-Phase Full-Bridge                               |    |

|     | PFC Rectifier Model with Standard dq-PWM control                                                | 84 |

| 5.3 | Simulation Results for Medium Power Level Three-Phase Full-Bridge                               |    |

|     | PFC Rectifier Model with DOCC                                                                   | 85 |

| 5.4 | Simulation Results for Medium Power Level Three-Phase Full-Bridge                               |    |

|     | PFC Rectifier Model with DOCC with Grid Voltage Measurement. $$ .                               | 86 |

| 5.5 | Simulation Results for Medium Power Level Three-Phase Full-Bridge                               |    |

|     | PFC Rectifier Model with DOCC with Inductive Voltage Drop Com-                                  |    |

|     | pensation                                                                                       | 86 |

| 5.6 | Simulation Results for Medium Power Level Three-Phase Full-Bridge                               |    |

|     | PFC Rectifier Model with DOCC with HPWM                                                         | 88 |

| 5.7 | Parameters for Simulations of Medium Power Level Three-Phase                                    |    |

|     | Shunt APF Model                                                                                 | 89 |

| 5.8  | Simulation Results for Medium Power Level Three-Phase Shunt APF                 |     |

|------|---------------------------------------------------------------------------------|-----|

|      | Model with DOCC with Standard pq-PWM with Hysteresis Current                    |     |

|      | Control                                                                         | 90  |

| 5.9  | Simulation Results for Medium Power Level Three-Phase Shunt APF                 |     |

|      | Model with DOCC with Standard pq-PWM with PI Current Control. $$                | 91  |

| 5.10 | Simulation Results for Medium Power Level Three-Phase Shunt APF                 |     |

|      | Model with DOCC                                                                 | 93  |

| 5.11 | Simulation Results for Medium Power Level Three-Phase Shunt APF                 |     |

|      | Model with DOCC with Grid Voltage Measurement                                   | 94  |

| 6.1  | Parameters for Simulations of Low Power Level Three-Phase Full-                 |     |

|      | Bridge PFC Rectifier and Shunt APF Models                                       | 99  |

| 6.2  | Simulation Results for Low Power Level Three-Phase Full-Bridge                  |     |

|      | PFC Rectifier Model with Standard dq-PWM                                        | 99  |

| 6.3  | Simulation Results for Low Power Level Three-Phase Full-Bridge                  |     |

|      | PFC Rectifier Model with DOCC Grid with Voltage Measurement. $$ .               | 100 |

| 6.4  | Simulation Results for Low Power Level Three-Phase Full-Bridge                  |     |

|      | PFC Rectifier Model with DOCC with Feed-forward Inductive Volt-                 |     |

|      | age Drop Compensation                                                           | 100 |

| 6.5  | Simulation Results for Low Power Level Three-Phase Full-Bridge                  |     |

|      | PFC Rectifier Model with DOCC with Hybrid PWM                                   | 100 |

| 6.6  | Simulation Results for Low Power Level Three-Phase Shunt APF                    |     |

|      | Model with Standard pq-PWM with Hysteresis and PI Current Con-                  |     |

|      | trols                                                                           | 101 |

| 6.7  | Simulation Results for Low Power Level Three-Phase Shunt APF                    |     |

|      | Model with DOCC with Voltage Measurement. $\ \ldots \ \ldots \ \ldots \ \ldots$ | 102 |

| 6.8  | Experimental Results for Low Power Level Three-Phase Full-Bridge                |     |

|      | PFC Rectifier Model with Standard dq-PWM Control                                | 102 |

| 6.9  | Experimental Results for Low Power Level Three-Phase Full-Bridge                |     |

|      | PFC Rectifier Model with DOCC with Voltage Measurement. $\ \ .$                 | 104 |

| 6.10 | Experimental Results for Low Power Level Three-Phase Full-Bridge                |     |

|      | PFC Rectifier with DOCC with Feed-forward Inductive Voltage Drop                |     |

|      | Compensation                                                                    | 105 |

| 6.11 | Experimental Results for Low Power Level Three-Phase Shunt APF                  |     |

|      | with DOCC with Grid Voltage Measurement                                         | 108 |

| A.1  | European Standard EN 61000-3-2: Harmonics Limits for Equipment                  |     |

|      | Classes                                                                         | 124 |

| A.2  | Current Distortion Limits for General Distribution Systems (120 $\rm V$         |     |

|      | Through 69 000 V)                                                               | 126 |

| A.3 | Current Distortion Limits for General Subtransmission Systems (69 |   |

|-----|-------------------------------------------------------------------|---|

|     | 001 V Through 161 000 V)                                          | 6 |

### List of Abbreviations

APF Active Power Filters, p. 3

BEBS Balanced Energy Based Schemes for Control of APF, p. 18

CBPWM Carrier-Based PWM Modulation, p. 45

CCM Continuous Conduction-Mode, p. 28

DOCC Digital One-Cycle Control, p. 4

FOCC Fast Response One-Cycle Control, p. 4

GCI Grid Connected Inverter, p. 4

HEBS Harmonic Extractor-Based Strategies for Control of APF, p.

17

HPWM Hybrid PWM Modulation, p. 45

NLC Non-Linear Carrier, p. 29

OCC One Cycle Control, p. 3

PCC Point of Common Coupling, p. 1

PF Power Factor, p. 3

PLL Phase-Lock-Loop, p. 6

PLL Phase-Locked Loops, p. 10

PWM Pulse Width Modulation, p. 3

SVPWM Space Vector PWM Modulation, p. 45

THD Total Harmonic Distortion, p. 5

d Duty-Cycle, p. 24

# List of Symbols

| $I_g^*$           | Grid Current Reference Amplitude, p. 3                                             |

|-------------------|------------------------------------------------------------------------------------|

| $L_g$             | Converter Inductance, p. 12                                                        |

| $R_{DC}$          | DC-bus Voltage Regulator, p. 3                                                     |

| $R_{es}$          | Modified Emulated Resistance, p. 66                                                |

| $R_{ig}$          | Current Regulator, p. 3                                                            |

| $T_s$             | Switching Period, p. 24                                                            |

| $V_m$             | Output of DC-bus Regulator in One-Cycle-Control, p. 3                              |

| $V_o$             | Converter Output Voltage, p. 29                                                    |

| $V_{N0}$          | Common-Mode Voltage, p. 11                                                         |

| $V_{ms}$          | Modified Output of DC-bus Voltage Regulator, p. 36                                 |

| $X_s$             | Amplitude of Space Vector of Generic Variable, p. 11                               |

| $ar{p}$           | Average Part of Instantaneous Active Power, p. 20                                  |

| $ar{q}$           | Average Part of Instantaneous Imaginary Power, p. 20                               |

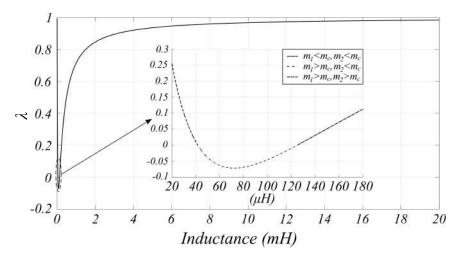

| $\lambda$         | Duty Cycle Convergence Ratio of Poincaré Maps, p. 56                               |

| $\mathbf{I}_{dq}$ | Vector of Converter Pole Voltages in dq-Reference Frame in Frequency Domain, p. 12 |

| $\mathbf{I}_{dq}$ | Vector of Grid Currents in dq-Reference Frame in Frequency<br>Domain, p. 12        |

| P                 | Mapping Relationship of Poincaré Maps, p. 55                                       |

| $\mathbf{V}_{dq}$ | Vector of Grid Voltages in dq-Reference Frame in Frequency<br>Domain, p. 12        |

- a Spatial Operator  $e^{j\frac{2}{3}\pi}$ , p. 11

- $\mathbf{i}_{dq}$  Vector of Grid Currents in dq-Reference Frame, p. 12

- $\mathbf{i}_{gabc}$  Three-Phase Grid Currents Vector, p. 11

- $\mathbf{v}_{dq}$  Vector of Converter Pole Voltages in dq-Reference Frame, p. 12

- $\mathbf{v}_{dq}$  Vector of Grid Voltages in dq-Reference Frame, p. 12

- $\mathbf{v}_{qabc}$  Three-Phase Grid Voltages Vector, p. 11

- $\mathbf{v}_{pabc}$  Three-Phase Converter Pole Voltages Vector, p. 11

- $\mu$  Zero Vector Apportion Ratio, p. 44

- $\omega$  Generic Angular Frequency, p. 11

- $\omega_g$  Grid Angular Frequency, p. 12

- $\tilde{p}$  Oscillating Part of Instantaneous Active Power, p. 20

- $\tilde{q}$  Oscillating Part of Instantaneous Imaginary Power, p. 20

- d Duty Cycle, p. 24

- $f_s$  Switching Frequency, p. 23

- i<sub>D</sub> Converter Diode Current, p. 31

- $i_L$  Converter Inductor Current, p. 31

- $i_S$  Converter Switch Current, p. 31

- $i_g$  Grid Current, p. 4

- $i_a^*$  Grid Current Reference, p. 3

- $i_{N0}$  Common-Mode Current, p. 46

- $i_{\alpha}, i_{\beta}$  Currents in  $\alpha$ - $\beta$  Reference Frame, p. 19

- k Grid Voltage Gain for OCC with Voltage Measurement, p. 4

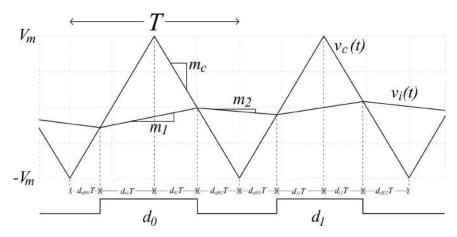

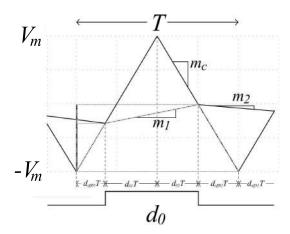

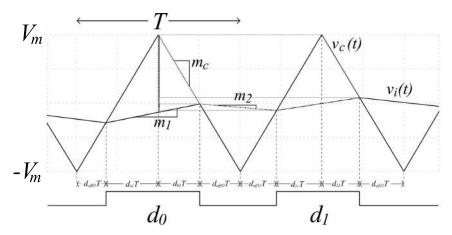

- $m_1$  Rising Slope of Modulating Signal, p. 57

- $m_2$  Falling Slope of Modulating Signal, p. 57

- $m_c$  Rising and Falling Slopes of Carrier Signal, p. 57

- p Instantaneous Active Power, p. 20

- q Instantaneous Imaginary Power, p. 20

- $v_c$  Carrier, p. 29

- $v_{\alpha}, v_{\beta}$  Voltages in  $\alpha$ - $\beta$  Reference Frame, p. 19

- $x^*$  Fixed Point of Poincaré Maps, p. 56

- - $x_s$  Space Vector of Generic Variable, p. 11

## Chapter 1

### Introduction

#### 1.1 Background of the Problem

The challenging goals of keeping up to an ever increasing demand of electrical energy and on the reduction of greenhouse gas emissions are bringing about continuous efforts to improve the Electrical Systems in many perspectives. On the generation side, there is currently an expansion of the use of renewable energy sources [6], [7] and improvements on transmission infrastructure [8]. On the distribution side, most of the manufacturers of domestic and industrial electrical loads are making efforts to improve their efficiency, with the introduction of switched-mode power supplies since the 70's [9]. However, even with these efforts, most of the loads are still fed by uncontrolled rectifiers with diodes and capacitors which are a simple, cost effective and robust solution for AC/DC conversion but making these loads highly non-linear and drawing a highly pulsating current [10].

The highly pulsating currents when flowing through the impedances of the distribution circuits bring serious problems related to voltage drop and voltage distortion, affecting consumers connected to a common grid [11]. Other effects on grid are increased transformer, capacitor, motor or generator heating, additional acoustic noise from motors, malfunction of ripple control systems, protective relays, etc [12].

The European Standard IEC 61000-3-2 [13] has been set to define the limits for harmonics on electronic and electrical equipment with rated phase current up to 16 A, in which the equipments are categorized in four classes according to Table 1.1. A flow chart for classification of Electrical equipment conforming to this Standard and the Harmonics limits for each class are presented in Appendix A.1.

On the other hand, IEEE has a set of recommendations (IEEE 519-2014) [14] for distortion limits. The main difference compared to the IEC Standard is that the harmonics are measured at the Point of Common Coupling (PCC) of a given installation, so what is concerned are the harmonics of the installation reflected to

Table 1.1: European Standard IEC 61000-3-2: Classes of Equipments

| Class | Equipments                                                                   |

|-------|------------------------------------------------------------------------------|

|       | Balanced 3-phase equipment;                                                  |

|       | Household appliances excluding equipment identified as class D;              |

| Λ     | Tools, excluding portable tools;                                             |

| А     | Dimmers for incandescent lamps;                                              |

|       | Audio equipment;                                                             |

|       | All other equipment, except that stated in one of the following classes.     |

| В     | Portable tools;                                                              |

| Ъ     | Arc welding equipment which is not professional equipment.                   |

| С     | Lighting equipment.                                                          |

| D     | PC, PC monitors, radio, or TV receivers. Input power $P \le 600 \text{ W}$ . |

the grid. The Current Distortion Limits for General Distribution Systems (120 V Through 69 000 V) and for General Subtransmission Systems (69 001 V Through 161 000 V) are summarized in Appendix A.2.

The solutions for harmonics issues can be classified into three classes [15], named First, Second and Third Classes. Examples of these solution classes are shown in Table 1.2.

Table 1.2: Solution for Harmonics Issues

| Class  | Solutions                                                                  |

|--------|----------------------------------------------------------------------------|

|        | Supplying the Loads from upstream;                                         |

| First  | Grouping the Disturbing Loads;                                             |

|        | Supplying the Loads from separate transformers.                            |

|        | Use of Transformers with special connections;                              |

| Second | Use of inductors for series connection in association with capacitor bank; |

| Second | Arrangement of System Earthing;                                            |

|        | Improvements on converter topology and/or control.                         |

|        | Passive Power Filters;                                                     |

| Third  | Active Power Filters;                                                      |

|        | Hybrid Power Filters.                                                      |

The first class is related to the distribution system, planning to determine how the installation can be modified to mitigate the effect of harmonics from disturbing loads on sensitive loads.

The second class of solutions is intended to mitigate or to confine harmonics produced by one ore more disturbing loads. The last solution of this class brings the solution to the inside of the load, which is related to philosophy of Standard IEC 61000-3-2.

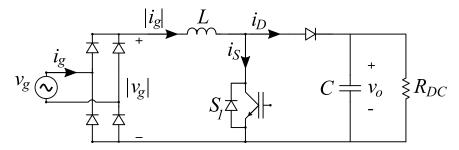

The third class of solutions makes use of dedicated equipment to exempt the grid to provide a path to the harmonics generated by non-linear loads. A passive filter is a path of low impedance for specified harmonics, so that the harmonics generated by the load flows through the filter instead of flowing to the grid. Furthermore,

the passive filters can provide reactive power for PF correction. The Active Power Filters (APF) are converters which are controlled in such a way that voltage and/or current harmonics are produced with same amplitude but in opposite phase as those generated by the non-linear loads.

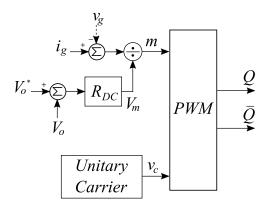

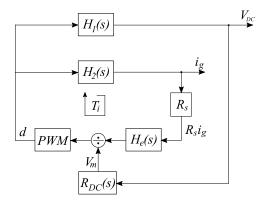

#### 1.2 Cascade Control of Converters

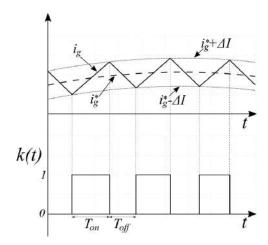

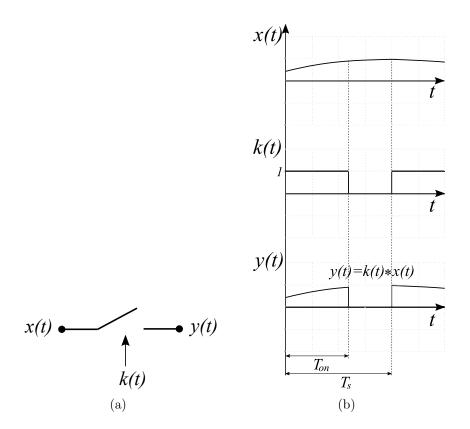

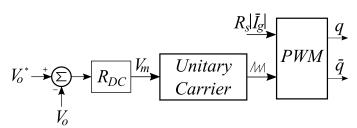

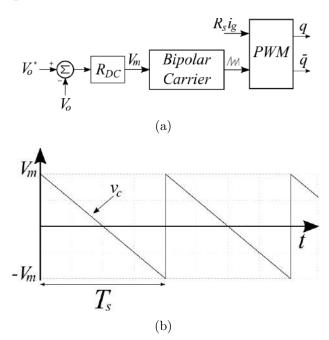

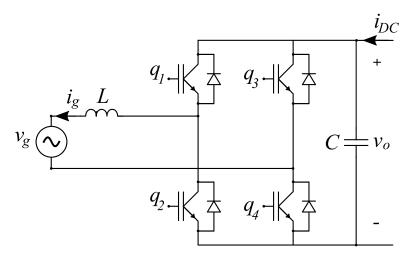

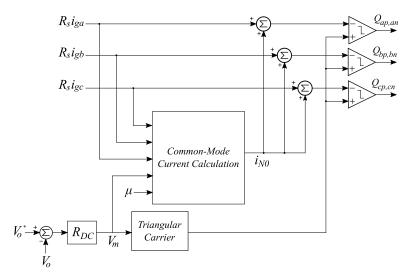

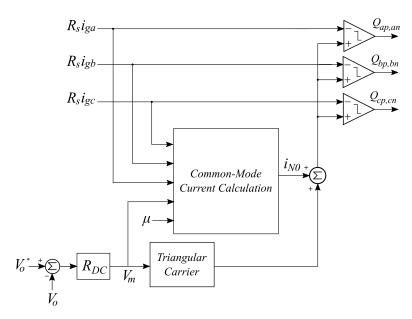

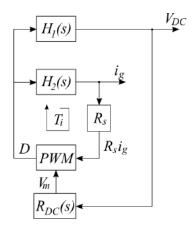

Conventional analog and digital control techniques for converters are based on the cascade structure depicted in Figure 1.1-a, composed of an inner current controller  $R_{ig}$  and an outer DC bus voltage regulator  $R_{DC}$ . The output of  $R_{DC}$  defines the current reference amplitude  $I_g^*$  which is multiplied with the grid voltage measurement to generate the current reference  $i_g^*$ . The output of  $R_{ig}$  is compared to an unitary carrier to define the switch states of the converter for Pulse Width Modulation (PWM) based techniques or controlled by hysteresis band controller.

Even though these techniques are widely used to control power converters, they have disadvantages such as big input inductor size, switch stress, zero-crossing distortion, etc [16]. Furthermore they require grid and DC bus voltage sensors and current sensor. For digital-based techniques, the computational loads of their algorithms demand use of high-cost microprocessor-based devices, which is not suitable for low and medium power applications.

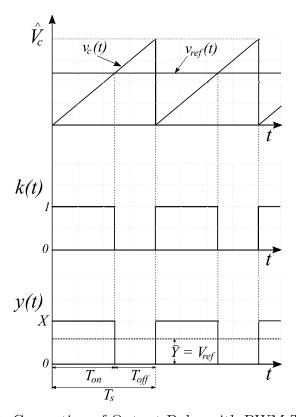

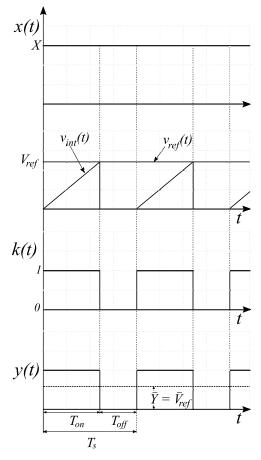

The One Cycle Control (OCC) technique, which is a non-linear PWM method and was proposed initially as an analog control method, realizes simultaneously PWM modulation and current control by the variation of carrier amplitude [17], [18] so that there is no explicit current loop (Figure 1.1-(b)). The output  $V_m$  of the DC bus voltage regulator  $R_{DC}$  defines the carrier amplitude, which is compared to the current measurement. This method requires only DC bus voltage and current sensors. The main advantages of this technique are simplicity, fast response, stability and robustness [18], [19].

Figure 1.1: Schematics of Cascade Control Techniques for Converters: (a) Conventional Current Mode PI Control, (b) Current Mode One-Cycle Control.

#### 1.3 Motivation

PFC Rectifiers and shunt APF are widely used solutions for PF correction and harmonics mitigation [20]. Even though these technologies have been applied since the 80's, these subjects are continuously studied concerning improvements on efficiency and costs, mainly focused in converter topologies and control improvements [21], [22]. On control side, the use of digital-based devices are increasingly spreading their application, since their cost is decreasing over time and at the same time their processing speed are on and on increasing [23].

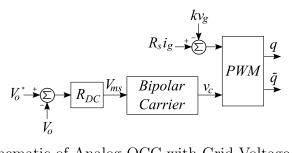

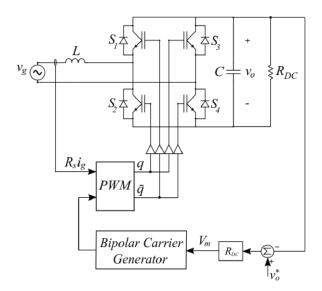

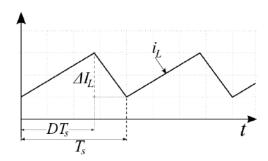

Enhancements on OCC are also a current subject of study of control for PFC rectifiers and APF [24], [25]. In [26] the sawtooth carrier was replaced by a triangular carrier, allowing the simplification of control circuit and avoiding the need of any averaging scheme for the sensed current. However, no study has been done for stability analysis of this technique.

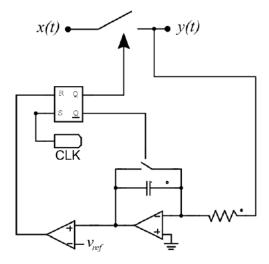

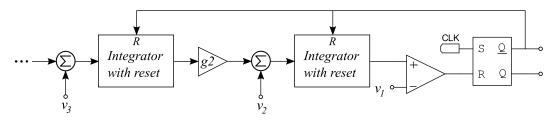

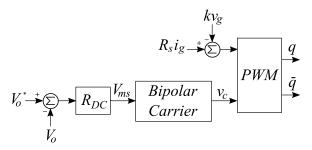

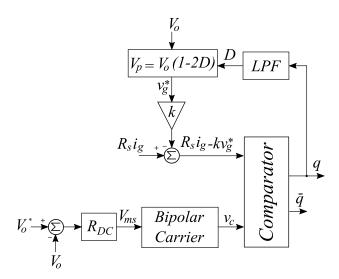

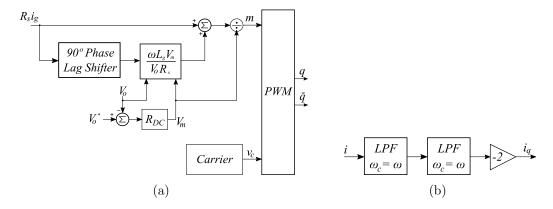

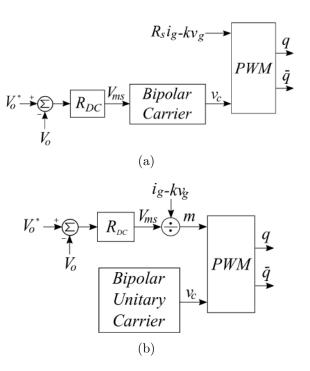

OCC has been digitally implemented in DSP for application in PFC [27] and APF [28]. In these techniques, instead of modulating the carrier amplitude, the output of  $R_{DC}$  divides the current measurement signal  $i_g$  generating the modulation signal m which is compared to an unitary carrier to generate the switch states - see Figure 1.2.

Figure 1.2: Schematics of Digital OCC Technique.

The algorithm of Digital OCC (DOCC) technique has easy implementation, so that systems with this control technique can employ low cost microprocessors to realize their control, what implies on system cost reduction.

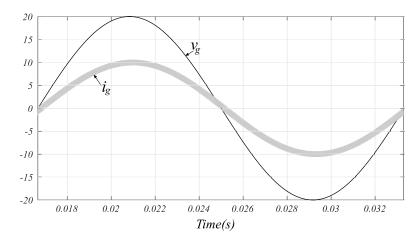

Besides, the OCC technique can be modified to include grid voltage measurement with a gain k, as depicted in Figure 1.3 with resulting signal  $kv_g$  obtained by multiplication of sensed voltage  $v_g$  and gain k, for applications in Grid Connected Inverters (GCI) with k < 0 [29], [30], [31] and recently an analog OCC-based technique so-called Fast Response One-Cycle Control (FOCC) [32] has been proposed, which makes use of grid voltage measurements with k > 0 to improve the dynamic response and perturbation rejection of three-phase APF. However, the application of voltage measurements in OCC-based strategies is done in a stratified way. Aspects such as influence of k on system dynamics and on system stability are not described in a generalized approach.

Figure 1.3: Schematic of Analog OCC with Grid Voltage Measurement.

Some improvements can be done on DOCC strategies, such as incorporation of Hybrid PWM, which has been done only for analog-based OCC strategies [5], and modification of strategy for compensation of inductive voltage drop [2].

#### 1.4 Objectives

The main objective of this work is to analyze the application of DOCC strategies to PFC Rectifier and shunt APF to improve their actuation on correction of PF and mitigation of Total Harmonic Distortion (THD). The control will be implemented in a DSP to control a three-phase boost converter.

To achieve the main objective, the following specific objectives will be fulfilled:

- Modeling the power circuit of single-phase and three-phase PFC Rectifier and shunt APF;

- Application of Poincaré Maps approach to a OCC-controlled single-phase bidirectional boost converter model to analyze its stability;

- Derivation of averaged model of single-phase bidirectional boost converter to be used in frequency analysis of OCC and DOCC;

- Simulation on PSIM Environment of medium and lower power three-phase PFC Rectifier and shunt APF with DOCC strategies;

- Experimental implementation of lower power three-phase PFC Rectifier and shunt APF with DOCC strategies.

#### 1.5 Contributions of the Dissertation

The main contributions of the Dissertation are listed below:

• Derivation of mandatory inductance value for stability of OCC strategies with triangular carrier;

- Proposal of a general approach for the application of grid voltage measurements to OCC techniques;

- Characterization of analog and digital OCC strategies through frequency analysis;

- Improvements on algorithm of feed-forward inductive voltage drop compensation concerning computational effort;

- Application of Hybrid PWM approach to DOCC.

#### 1.6 Organization of the Dissertation

This text is composed of seven Chapters and two Appendices. Besides this Introductory Chapter, Chapter 2 presents a review on Active Compensation of Power Factor and Harmonics, approaching the classification of these solutions based on system and converter topology, and reviewing the main control found in Literature for these applications. Also, the project of standard PWM control methods are present, including a project of a Phase-Lock-Loop (PLL) circuit, mandatory part of these control strategies.

In chapter 3, it is done a review on OCC, starting from the early proposal of the analog technique, passing by the application of Resistor Emulator Approach with OCC to achieve unitary PF and low THD which can be applied to single and three-phase converters. Also, the three-phase OCC strategies are reviewed. Finally, it is presented the problem of inductive voltage drop, a inherent drawback of OCC strategies, and its remedy.

Chapter 4 shows comprehensively the contributions of this work, presenting also discussions about the improvements done in DOCC strategies.

In chapter 5, the results of simulations done in medium power level model of PFC Rectifier and shunt APF are provided, together with analysis of results.

Chapter 6 presents simulation and experimental results with comparative analysis of low scale model of PFC Rectifier and shunt APF, comparing these results also with those obtained in Chapter 5, to validate the control for application in low and medium power applications.

Chapter 7 concludes this work and presents suggestions for future work.

Appendix A shows the main aspects of the Standards for Harmonics Limits concerned in this work and Appendix B presents the deduction of the dynamic model of the H-bridge single-phase AC-DC converter controlled by OCC based on state-space averaging method.

### 1.7 Partial Conclusions

In this chapter it has been shown the general aspects of PF and Harmonics mitigation, covering the introduction to mainly used Standards worldwide, the main solutions. The OCC technique has also been introduced, together with motivations, objectives and contributions of the dissertation.

## Chapter 2

# Review on Active Compensation of Power Factor and Harmonics

#### 2.1 Introduction

In this chapter it will be reviewed the general aspects of PFC Rectifiers and APF which are active solutions for PF and Harmonics correction. It will be studied their main aspects, covering general hardware and system topology classifications and also it will be shown a review on the control for these solutions. Furthermore, the design of conventional controls for each one of the solutions are presented.

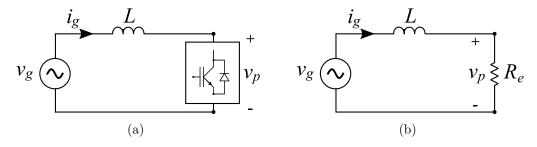

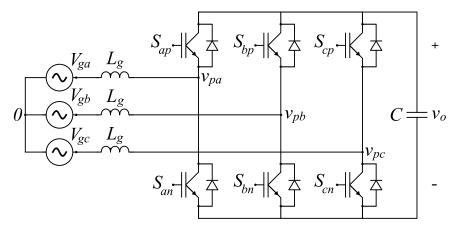

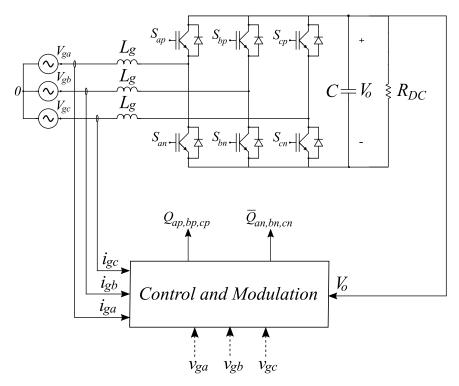

#### 2.2 PFC Rectifiers

Rectifiers are the most commonly used power electronics-based systems, with application ranging from adjustable-speed drive, Uninterruptible Power Supplies (UPS), High-Voltage Direct Current Transmission Systems, DC microgrids, general electronics loads, utility interfaces with renewable energy sources [33]. The main role of those converters is to make the interface between the AC grid and the DC bus. The DC bus voltage feeds electronic loads directly or eventually may be converted to AC by an DC-AC converter also known as inverter, or other DC voltage level by a isolated or non-isolated DC-DC converter as shown in Figure 2.1. The main concerns about the rectifiers are the harmonic content of input currents, low PF and slowly varying rippled DC output [34].

PFC Rectifiers are rectifiers with improved PF as well as harmonics content [35]. They work with a controlled converter operating at the Front-End to the load circuitry, so that they regulate the input grid current and output DC bus voltage. This alternative is highly applied in industrial application [11].

Figure 2.1: Schematics of Typical Converter Arrangement for Supplying Electrical Loads From Three-Phase AC Utility: (a) AC-DC Conversion, (b) AC-DC-DC Conversion with Non-Isolated DC-DC Converter, (c) AC-DC-DC Conversion with Isolated DC-DC Converter, (d) AC-DC-DC (Back-to-Back) Conversion.

#### 2.2.1 Classification

The rectifiers can be classified by different aspects, for example energy flow direction, converter components [36] and converter topology. Based on energy flow direction, a rectifier can be either unidirectional, when the energy flows only from the AC side to DC side, or bidirectional, as the name suggests, allowing the energy flow in both directions. A rectifier can be classified as 1) Passive, when it is constructed by a diode bridge and passive elements for smoothing AC input current THD and DC voltage ripple [37]; 2) Hybrid rectifiers which are solutions based on passive rectifiers but combined with active solutions, for example an active element emulating a reactance behavior [38], bringing improvements in harmonic current level, output voltage ripple and converter volume; 3) Active PFC Systems, when the converter has forced commutation semiconductors, exclusively switching frequency passive components and regulated output voltage, such as the Direct Active Three-Phase PFC Rectifier proposed in [39].

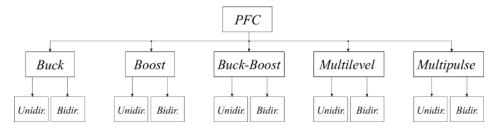

Based on topology, the converter can be classified in Boost, Buck, Buck-Boost, Multilevel, Multipulse [36] as depicted in Figure 2.2.

Figure 2.2: Classification of Rectifiers Based on Energy Flow Direction and Converter Topology.

#### 2.2.2 Review on Control of PFC Rectifiers

The control of rectifiers can have three stages: DC bus control, current control and command pulses generation, or two stages when the current control and pulse generation are integrated.

The DC bus voltage control regulates the output voltage through regulation of active power flow. Traditional control techniques can be used such as PI [40] and PID control [41]. Furthermore sliding-mode control [42], fuzzy controllers [43], adaptive controllers [44], artificial neural network based controllers [45] can be used. These methods have good performance but with the expense of a high computational load. The output of DC bus controller defines the amplitude of input current.

For three stages strategies, the current can be controlled by several methods including PI [46], PID [47], PR [48], Neural Networks [49], Fuzzy Methods [49], Sliding Mode [50] and Adaptive [51]. The output of the current controller define the input signals for the PWM modulators to generate the command pulses for the switches. These methods have advantages of performance and robustness, but have some drawbacks as mandatory grid voltage measurement, control complexity and high computational cost of implementation.