# A COMPARATIVE ANALYSIS OF DYNAMIC VISION SENSORS USING $180\;\mathrm{nm}$ CMOS TECHNOLOGY

Juan Pablo Girón Ruiz

Dissertação de Mestrado apresentada ao Programa de Pós-graduação em Engenharia Elétrica, COPPE, da Universidade Federal do Rio de Janeiro, como parte dos requisitos necessários à obtenção do título de Mestre em Engenharia Elétrica.

Orientador: José Gabriel Rodriguez Carneiro Gomes

Rio de Janeiro Janeiro de 2017

# A COMPARATIVE ANALYSIS OF DYNAMIC VISION SENSORS USING 180 nm CMOS TECHNOLOGY

Juan Pablo Girón Ruiz

DISSERTAÇÃO SUBMETIDA AO CORPO DOCENTE DO INSTITUTO ALBERTO LUIZ COIMBRA DE PÓS-GRADUAÇÃO E PESQUISA DE ENGENHARIA (COPPE) DA UNIVERSIDADE FEDERAL DO RIO DE JANEIRO COMO PARTE DOS REQUISITOS NECESSÁRIOS PARA A OBTENÇÃO DO GRAU DE MESTRE EM CIÊNCIAS EM ENGENHARIA ELÉTRICA.

Examinada por:

Prof. José Gabriel Rodriguez Carneiro Gomes, Ph.D

Prof. Antonio Petraglia, Ph.D

Prof. Mauricio Pamplona Pires, D.Sc.

RIO DE JANEIRO, RJ – BRASIL JANEIRO DE 2017 Girón Ruiz, Juan Pablo

A comparative analysis of Dynamic Vision Sensors Using 180 nm CMOS Technology/Juan Pablo Girón Ruiz.

- Rio de Janeiro: UFRJ/COPPE, 2017.

XVI, 86 p.: il.; 29, 7cm.

Orientador: José Gabriel Rodriguez Carneiro Gomes

Dissertação (mestrado) – UFRJ/COPPE/Programa de Engenharia Elétrica, 2017.

Referências Bibliográficas: p. 66 – 69.

1. Dynamic vision sensors. 2. Frame-free. 3. Temporal contrast changes. 4. Time-based pulse width modulation. 5. Asynchronous delta modulation. 6. Asynchronous logic. 7. Address event representation. I. Gomes, José Gabriel Rodriguez Carneiro. II. Universidade Federal do Rio de Janeiro, COPPE, Programa de Engenharia Elétrica. III. Título.

"Não to mandei eu? Esforça-te, e tem bom ânimo; não te atemorizes, nem te espantes; porque o Senhor teu Deus está contigo, por onde quer que andares." Josué 1:9

# Acknowledgment

Em primeiro lugar, quero lhe agradecer a Deus por ter-me abençoado grandemente nesta experiência na Cidade Maravilhosa. Se falasse todos os milagres que Jesus fez por mim, não alcançaria esta pagina para escrevê-los. Considero que o maior logro que consegui no mestrado foi de reencontrar-me com Cristo Jesus. Aos meus pais, María Esther Ruiz e Luis Eduardo Girón, devo-lhes a minha formação e os valores que hoje levo na minha vida. À minha avó, Fabiola Lopez, por ser a minha segunda mãe incondicional, que Deus te enche de muitos anos de vida. Ao meu avô, Alcides Ruiz, que Deus seja abençoando a tua vida espero vê-lo daqui a pouco. Aos meus irmãos Victor e Andrés, são uns exemplos para mim para ser cada dia melhor pessoa. Aos meus sogros, seu Enrique e Dona Flor, por ser um exemplo para minha vida pela sua coragem para afrontar os problemas. A minha noiva, Ana María Zúñiga, não tenho palavras para lhe agradecer por tudo que tem feito por mim, nunca faltaram palavras de motivação e momentos de muita alegria. Esta experiência não tivesse sido tão enriquecedora sem a sua presença.

Ao meu orientador, Professor José Gabriel, muito obrigado por permitir-me trabalhar com ele e dar-me liberdade para desenvolver esta dissertação de acordo com minha metodologia de estudo. Apesar de seus inumeráveis compromissos com outros estudantes e com a Universidade, sempre separou um espaço em sua agenda para falar sobre este trabalho e fazer que eu pensasse de forma diferente para solucionar as dificuldades. Sem ele este trabalho não teria sido possível.

Aos meus colegas do laboratório de Processamento Analógico e Digital de Sinais (PADS), fico grato por ter-me acolhido nestes dois anos, especialmente a: Thiago Valentin, Fabian Olivera, João, Allan, Fernanda, Pedro e Roberto por dar-me a mão nos momentos que mais precisei. Ao Pastor Tubino por sempre ter uma palavra de vida eterna e de conforto espiritual, sua igreja me permitiu chegar mais perto de Cristo Jesus.

Por último, à CAPES pelo apoio financeiro para a realização de esta dissertação, igualmente para o pessoal administrativo da PEE/COPPE por estar sempre dispostos a orientar-me nos tramites do mestrado. Resumo da Dissertação apresentada à COPPE/UFRJ como parte dos requisitos necessários para a obtenção do grau de Mestre em Ciências (M.Sc.)

### UMA ANÁLISE COMPARATIVA DE SENSORES DE VISÃO DINÂMICA USANDO TECNOLOGIA CMOS 180 nm

Juan Pablo Girón Ruiz

Janeiro/2017

Orientador: José Gabriel Rodriguez Carneiro Gomes

Programa: Engenharia Elétrica

O desenvolvimento de sensores de visão dinâmicos (DVS) é considerado um dos avanços mais relevantes em termos de processamento de dados no plano focal de câmeras CMOS, por estar fundamentado em processamento neural. O tipo de pixel usado por um DVS é baseado na funcionalidade de um caminho neural conhecido como magno-cellular pathway, encontrado na conexão entre a retina biológica e o sistema nervoso central, e caracterizado por responder de forma assíncrona às mudanças temporárias de intensidade de luz e por codificar a informação de entrada por meio de pulsos. Neste trabalho, são projetadas e comparadas três arquiteturas DVS: DVS básico, ATIS (asynchronous time-based image sensor) e ADMDVS (asynchronous delta modulation dynamic vision sensor). Entre estas, somente a arquitetura ATIS implementa um sistema de codificação de intensidade da luz, utilizando modulação por largura de pulso no domínio do tempo. No processo de projeto, a metodologia  $g_m/I_d$  é usada como ferramenta adequada para o dimensionamento dos transistores que compõem os pixels. Usando diferentes linguagens de programação, são desenvolvidos vários scripts para automatizar as etapas de simulação. O funcionamento correto de cada arquitetura é verificado através da comparação entre o resultado obtido por simulação elétrica e o resultado previsto através de simulação numérica usando um modelo idealizado. Finalmente, conclui-se que a resposta de cada arquitetura, obtida por simulação elétrica, se aproxima bastante da resposta prevista através dos modelos idealizados, o que valida os projetos propostos. Com base nos resultados obtidos, é possível realizar uma comparação entre as diferentes arquiteturas.

Abstract of Dissertation presented to COPPE/UFRJ as a partial fulfillment of the requirements for the degree of Master of Science (M.Sc.)

### A COMPARATIVE ANALYSIS OF DYNAMIC VISION SENSORS USING 180 nm CMOS TECHNOLOGY

Juan Pablo Girón Ruiz

January/2017

Advisor: José Gabriel Rodriguez Carneiro Gomes

Department: Electrical Engineering

The development of dynamic vision sensors (DVS) is regarded as one of the most relevant advances in CMOS camera focal-plane signal processing, because it is based on neural processing. The type of pixel that is used in a DVS mimicks the functionality of a neural pathway known as magno-cellular pathway, which is responsible for part of the communication between the biological retina and the central nervous system. The magno-cellular pathway responds in asynchronous fashion to light intensity temporal variations, and it encodes such variations by means of neural spike sequences. In this work, we designed and compared three DVS architectures: basic DVS, ATIS (asynchronous time-based image sensor) and ADMDVS (asynchronous delta modulation dynamic vision sensor). Among these architectures, only ATIS implements a light intensity encoding system, using time-based pulse-width modulation. In the design process,  $g_m/I_D$  methodology is used as a suitable tool for pixel design. Using different programming languages, several scripts are developed for making the simulation stages automatic. To verify the correct operation of each architecture, we compare electrical simulation results to numerical simulation predictions that were previously obtained using ideal pixel models. We finally conclude that the behavior of each architecture, which was obtained by electrical simulation, approximates rather well the behavior that was predicted using ideal models, which validates the proposed pixel design for all three sensor types. Based on these results, the basic DVS, ATIS, and ADMDVS architectures may be compared.

# Contents

| Li            | ist of | Figures                                                                          | x |

|---------------|--------|----------------------------------------------------------------------------------|---|

| $\mathbf{Li}$ | ist of | Tables xiv                                                                       | V |

| $\mathbf{Li}$ | ist of | Abbreviations                                                                    | V |

| 1             | Intr   | oduction                                                                         | 1 |

|               | 1.1    | Objectives                                                                       | 3 |

|               | 1.2    |                                                                                  | 3 |

| <b>2</b>      | The    | eory                                                                             | 4 |

|               | 2.1    | Dynamic Vision Sensor                                                            | 4 |

|               |        | 2.1.1 DVS Pixel Model                                                            | 8 |

|               | 2.2    | ATIS Pixel                                                                       | 0 |

|               |        | 2.2.1 Correlated Double Sampling (CDS)                                           | 2 |

|               |        | 2.2.2 True Correlated Double Sampling                                            | 2 |

|               |        | 2.2.3 ATIS Model                                                                 | 4 |

|               |        | 2.2.4 Additional ATIS Sensor Functionality                                       | 5 |

|               | 2.3    | ADMDVS pixel                                                                     | 6 |

|               |        | 2.3.1 ADM in DVS                                                                 | 8 |

|               |        | 2.3.2 ADMDVS Model                                                               | 0 |

|               | 2.4    | Asynchronous Logical Circuit                                                     | 0 |

|               |        | 2.4.1 Delay-Insensitive Designs                                                  | 1 |

|               | 2.5    | Address-Event Representation                                                     | 2 |

|               | 2.6    | Integrated Circuit Design based on the $g_m/I_D$ Method $\ldots \ldots \ldots 2$ | 4 |

| 3             | Pix    | el Design 3                                                                      | 1 |

|               | 3.1    | Photoreceptor based on Transimpedance Amplifier                                  | 1 |

|               | 3.2    | Operational Amplifier                                                            | 4 |

|               | 3.3    | Voltage Comparator with Hysteresis                                               | 8 |

|               | 3.4    | AER Circuit                                                                      | 2 |

|               | 3.5    | Exposure Measurement Logic                                                       | 4 |

|    | 3.6   | Delay Element Circuit                      | 46        |

|----|-------|--------------------------------------------|-----------|

|    | 3.7   | Summary of Designed Pixels                 | 47        |

| 4  | Sim   | ulation Results                            | 48        |

|    | 4.1   | DVS Pixel Simulation                       | 49        |

|    | 4.2   | ATIS Pixel Simulation                      | 52        |

|    | 4.3   | ADMDVS Pixel Simulation                    | 53        |

|    | 4.4   | DVS 8 $\times$ 8 Pixel Array Simulation    | 56        |

|    | 4.5   | ATIS $4 \times 4$ Pixel Array Simulation   | 57        |

|    |       | 4.5.1 Triangular Waveform Input            | 58        |

|    |       | 4.5.2 2-D Spiral Input                     | 60        |

|    | 4.6   | ADMDVS $4 \times 4$ Pixel Array Simulation | 61        |

|    | 4.7   | DVS, ATIS and ADMDVS Comparison            | 62        |

| 5  | Con   | clusions                                   | 64        |

| Bi | bliog | raphy                                      | 66        |

| Α  | Pixe  | el Array Simulation                        | 70        |

| в  | Cod   | es for simulating DVS cameras              | <b>74</b> |

# List of Figures

| 2.1  | Pixel schematic diagram.                                                                          | 5  |

|------|---------------------------------------------------------------------------------------------------|----|

| 2.2  | DVS pixel instance. (a) DVS pixel as a system building block, and                                 |    |

|      | (b) DVS pixel operation fundamentals, adapted from [15]                                           | 8  |

| 2.3  | ATIS pixel instance, which is composed by a DVS pixel (left) and an                               |    |

|      | exposure measurement circuit (right)                                                              | 11 |

| 2.4  | CDS schematic diagram.                                                                            | 12 |

| 2.5  | True CDS operation in time-based vision sensors: (a) single threshold,                            |    |

|      | and (b) two thresholds [18]. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                | 14 |

| 2.6  | True CDS implementation                                                                           | 14 |

| 2.7  | Logical circuit enabling ATIS photograph capture: (a) schematic di-                               |    |

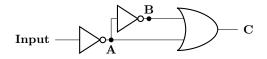

|      | agram, and (b) timing diagram                                                                     | 16 |

| 2.8  | DVS information encoding methods: (a) feedback and reset and (b)                                  |    |

|      | feedback and subtract $[21]$                                                                      | 17 |

| 2.9  | ADMDVS pixel instance                                                                             | 17 |

| 2.10 | ADMDVS basic block diagram [22]                                                                   | 18 |

| 2.11 | Asynchronous delta modulation circuit [21]                                                        | 19 |

| 2.12 | Four-phase handshaking protocol timing diagram                                                    | 21 |

| 2.13 | A fork and the isochronic assumption.                                                             | 22 |

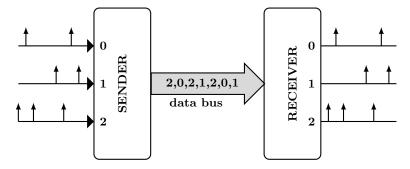

| 2.14 | AER concept [28]                                                                                  | 23 |

| 2.15 | Eight-input arbitered AER example. At each level, a winning input is                              |    |

|      | selected pairwise. Only one index, corresponding to the pixel having a                            |    |

|      | circuit path connecting it to the winning input at Level 3, is encoded                            |    |

|      | for transmission through the data bus                                                             | 24 |

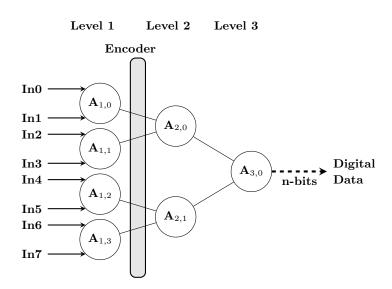

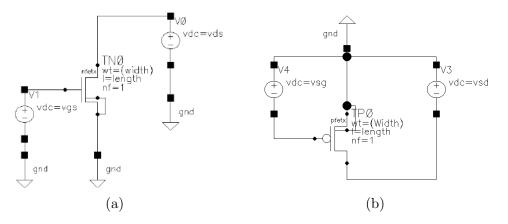

| 2.16 | Transistor setup for the extraction of $g_m/I_D$ versus $I_D$ curves: (a)                         |    |

|      | n-channel transistor, and (b) p-channel transistor                                                | 26 |

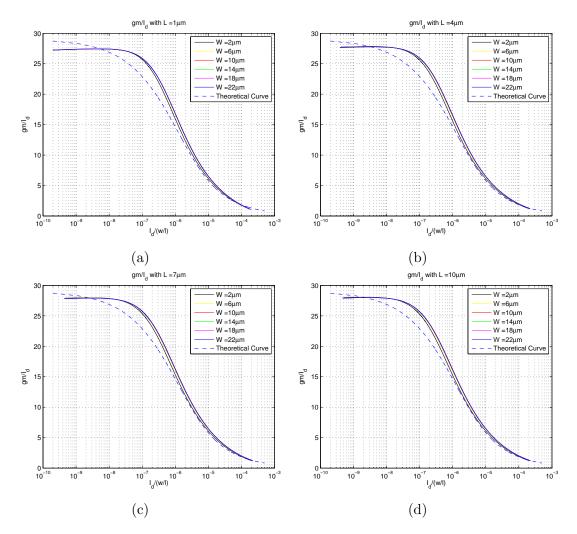

| 2.17 | Simulated $g_m/I_D$ versus $I_D$ curves extracted from an n-channel tran-                         |    |

|      | sistor model. In each plot, transistor width varies from 2 $\mu \mathrm{m}$ to 22                 |    |

|      | $\mu {\rm m}.$ Transistor length varies as follows: (a) $L=1~\mu {\rm m},$ (b) $L=4~\mu {\rm m},$ |    |

|      | (c) $L = 7 \ \mu \text{m}$ , and (d) $L = 10 \ \mu \text{m}$ .                                    | 27 |

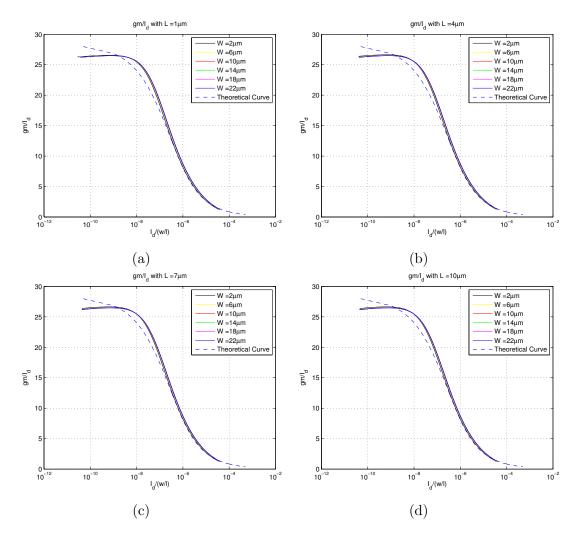

| 2.18 | Simulated $g_m/I_D$ versus $I_D$ curves extracted from a p-channel transistor model. In each plot, transistor width varies from 2 $\mu$ m to 22 $\mu$ m. Transistor length varies as follows: (a) $L = 1 \mu$ m, (b) $L = 4 \mu$ m, (c) $L = 7 \mu$ m and (d) $L = 10 \mu$ m | 28 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.19 | (c) $L = 7 \ \mu m$ , and (d) $L = 10 \ \mu m$                                                                                                                                                                                                                               | 28 |

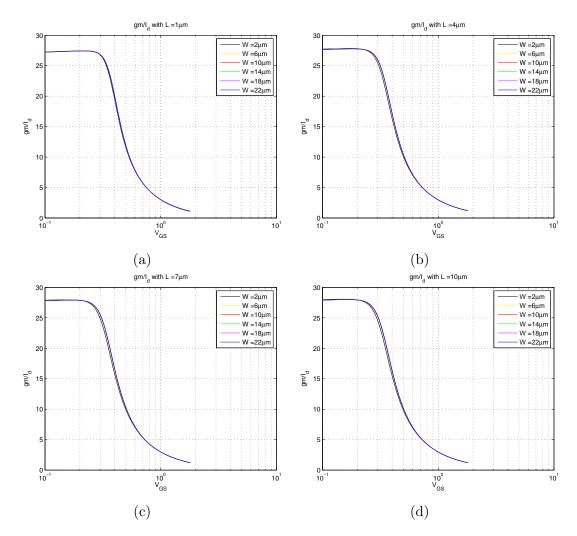

| 2.20 | $\mu$ m, (c) $L = 7 \mu$ m, and (d) $L = 10 \mu$ m                                                                                                                                                                                                                           |    |

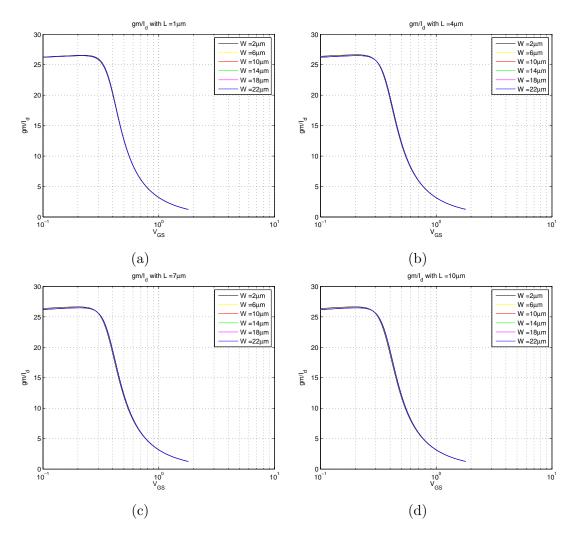

| 9 91 | $L = 7 \ \mu \text{m}$ , and (d) $L = 10 \ \mu \text{m}$                                                                                                                                                                                                                     | 30 |

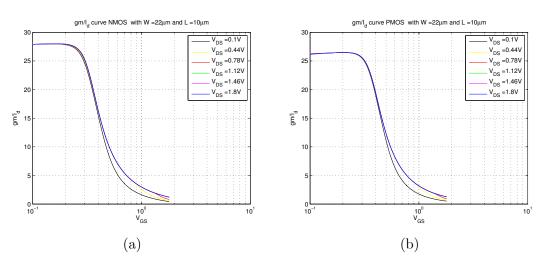

| 2.21 | Relationship between $g_m/I_D$ and $V_{gs}$ in the case of $V_{ds}$ variation: (a) n-channel transistor and (b) p-channel transistor.                                                                                                                                        | 30 |

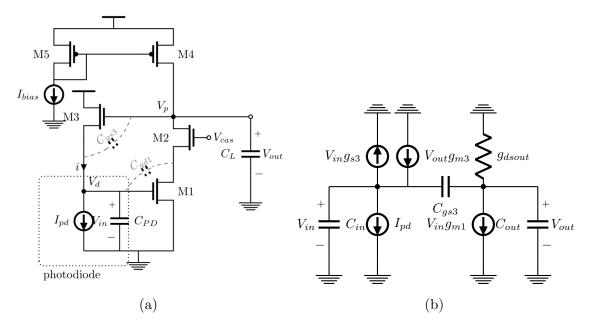

| 3.1  | Photoreceptor based on transimpedance amplifier: (a) schematic di-                                                                                                                                                                                                           |    |

|      | agram and (b) small-signal model                                                                                                                                                                                                                                             | 32 |

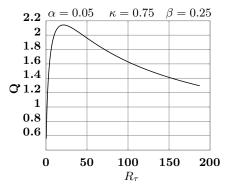

| 3.2  | Quality factor versus $R_{\tau}$                                                                                                                                                                                                                                             | 33 |

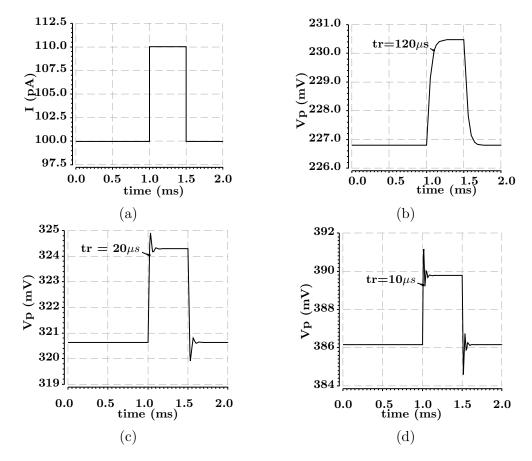

| 3.3  | Photoreceptor input current pulse (a), and photoreceptor pulse re-<br>sponse for three different $I_{bias}$ values: (b) 50 pA, (c) 300 pA, and (d)                                                                                                                           |    |

|      | $1 \text{ nA.} \qquad \dots \qquad $                                                                                                                                 | 34 |

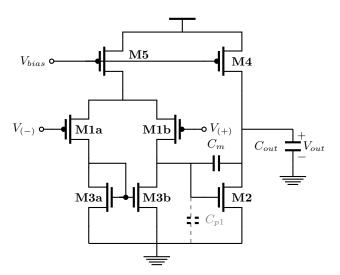

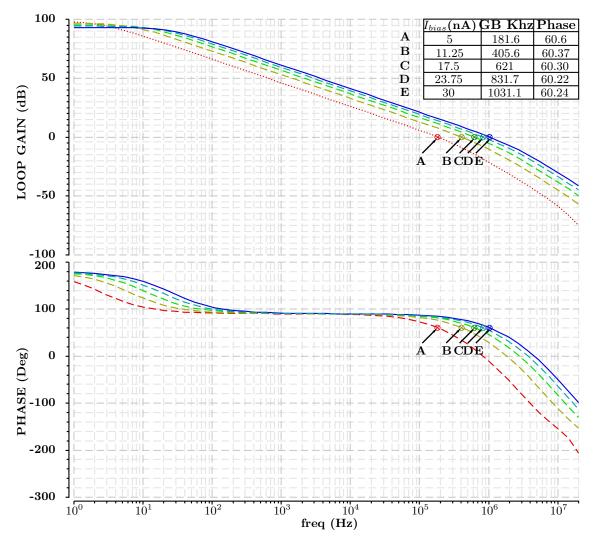

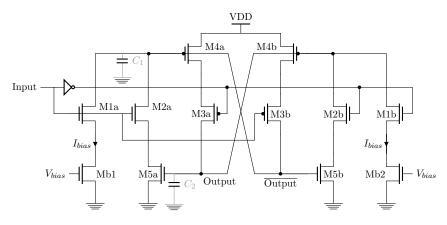

| 3.4  | Two-stage operational amplifier.                                                                                                                                                                                                                                             | 35 |

| 3.5  | Two-stage operational amplifier frequency response.                                                                                                                                                                                                                          | 38 |

| 3.6  | Voltage comparator [18]                                                                                                                                                                                                                                                      | 39 |

| 3.7  | Circuit for verifying the voltage offset based on Monte Carlo simulation.                                                                                                                                                                                                    |    |

| 3.8  | Voltage comparator offset estimation based on Monte Carlo simulation.                                                                                                                                                                                                        |    |

| 3.9  | Voltage comparator simulation results: (a) Spectre simulation indi-                                                                                                                                                                                                          |    |

| 0.0  | cating hysteresis, using $V_h = 170$ mV; (b) hysteresis voltage $V_{hyst}$ ,                                                                                                                                                                                                 |    |

|      | plotted as a function of $V_h$                                                                                                                                                                                                                                               | 42 |

| 3.10 | AER system for $4 \times 4$ pixel array: (a) X-AER system (for enabling                                                                                                                                                                                                      |    |

| 0.20 | column requests); (b) Y-AER system (for enabling row requests)                                                                                                                                                                                                               | 43 |

| 3.11 | Circuits that compose parts of the AER systems: (a) mutual exclusion                                                                                                                                                                                                         |    |

|      | (ME) circuit, (b) basic arbiter, and (c) X-ARBITER                                                                                                                                                                                                                           | 44 |

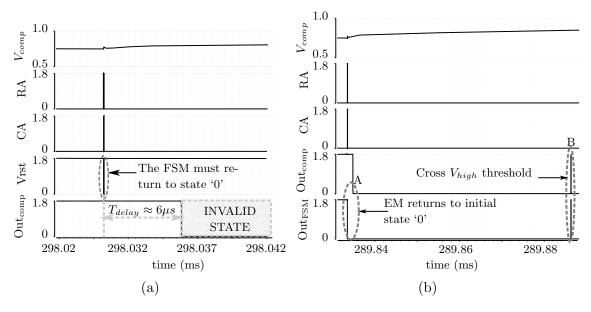

| 3.12 | Timing diagram for a single $off$ event detected at DVS pixel: (a)                                                                                                                                                                                                           |    |

| _    | exposure measurement logic in invalid state because of voltage com-                                                                                                                                                                                                          |    |

|      | parator delay, and (b) correct response $(Out_{FSM})$ obtained with the                                                                                                                                                                                                      |    |

|      | proposed solution.                                                                                                                                                                                                                                                           | 45 |

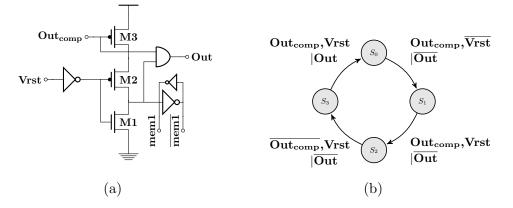

|      |                                                                                                                                                                                                                                                                              |    |

| 3.13 | Circuit for solving the exposure measurement logic invalid state prob-<br>lem: (a) finite state machine implementation, and (b) finite state                                                                                                                                                                                                  | 46       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.14 | machine implementation state diagramDelay element circuit                                                                                                                                                                                                                                                                                     | 46<br>47 |

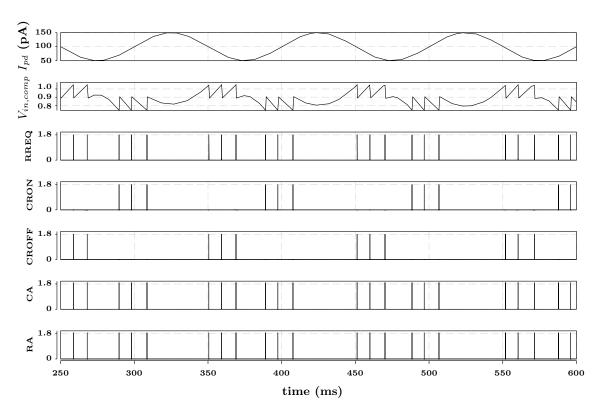

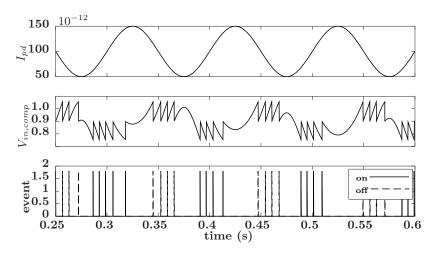

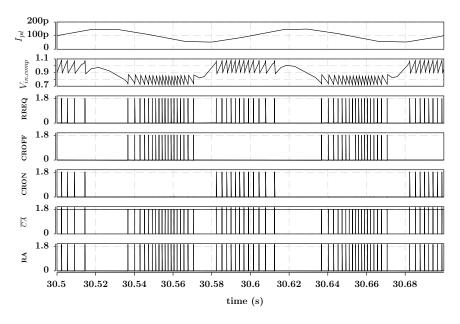

| 4.1  | Single DVS pixel transient simulation (250 ms to 600 ms) with a sinusoidal input $I_{pd}$ (first plot, at the top). The second plot shows the voltage comparator output $V_{comp}$ . The third plot shows data bus pixel request (RREQ). The fourth and fifth plots show on and off events (CRON and CROFF). The sixth and seventh plots show |          |

| 4.0  | column and row acknowledgment (CA and RA) signals                                                                                                                                                                                                                                                                                             | 50       |

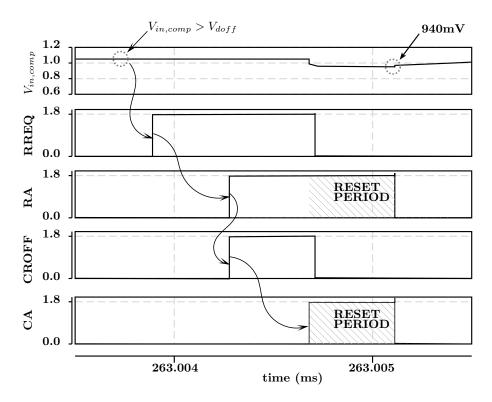

| 4.2  | Timing diagram corresponding to a communication cycle that is trig-<br>gered by a detected <i>off</i> event in Figure 4.1.                                                                                                                                                                                                                    | 50       |

| 4.3  | Single pixel DVS simulation using a numerical model from Section 2.1.1, and the same sinusoidal input shown in Figure 4.1. The second plot shows the predicted voltage comparator output, and the third                                                                                                                                       | 50       |

|      | plot shows predicted events. Communications with row and column control units are not taken into account.                                                                                                                                                                                                                                     | 51       |

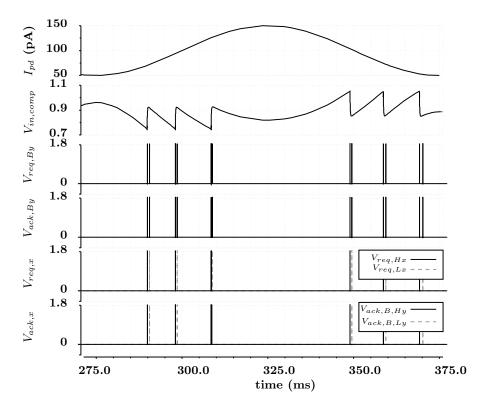

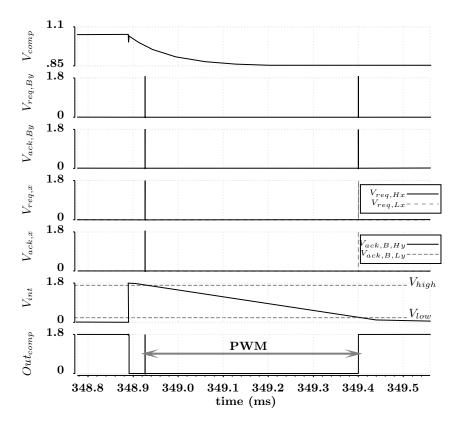

| 4.4  | Single ATIS pixel transient simulation (275 ms to 375 ms) with a sinusoidal input $I_{pd}$ equal to the one used in Figure 4.1. Relevant exposure measurement signals, which are described in the text, are                                                                                                                                   | 91       |

|      | shown in the third, fourth, fifth, and sixth plots                                                                                                                                                                                                                                                                                            | 53       |

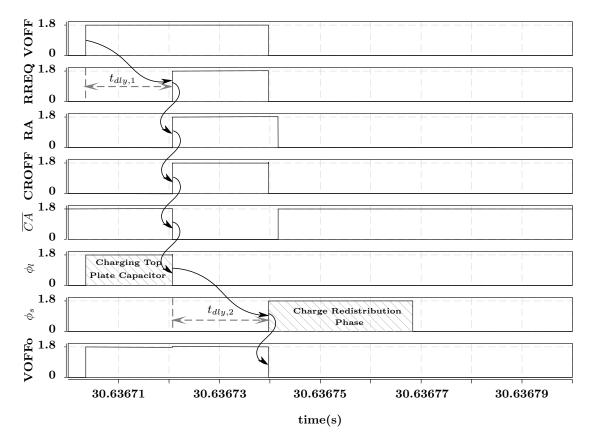

| 4.5  | Timing diagram corresponding to a communication cycle that is trig-<br>gered by a detected <i>off</i> event in Figure 4.4                                                                                                                                                                                                                     | 54       |

| 4.6  | Single ADMDVS pixel transient simulation $(30.5 \text{ s to } 30.7 \text{ s})$ with a                                                                                                                                                                                                                                                         |          |

|      | sinusoidal input $I_{pd}$ equal to the one used in Figure 4.1                                                                                                                                                                                                                                                                                 | 55       |

| 4.7  | Timing diagram corresponding to a communication cycle that is trig-<br>gered by a detected off event in Figure 4.6. Time delays $t_{dly,1}$ and $t_{dly,2}$ allow for capacitor charging $C_f$ and charge redistribution among                                                                                                                |          |

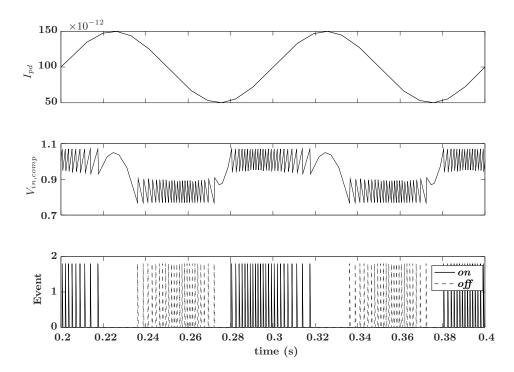

| 4.8  | the capacitors in the ADMDVS pixel (see Figure 2.11) Single pixel ADMDVS simulation using a numerical model from Section 2.3.2, and the same sinusoidal input shown in Figure 4.1. The second plot shows the predicted voltage comparator output, and the                                                                                     | 55       |

|      | third plot shows predicted events. Communication with row and col-                                                                                                                                                                                                                                                                            |          |

|      | umn control units is not taken into account.                                                                                                                                                                                                                                                                                                  | 56       |

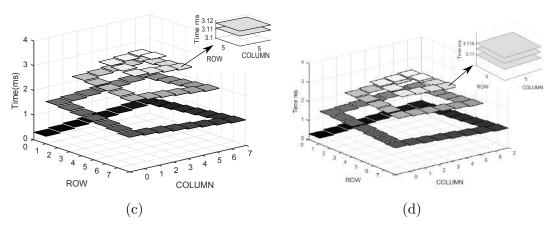

- 4.9 8 × 8 DVS pixel array. Comparison between electrical simulation results and predictions based on the numerical model in Section 2.1.1:

(a) and (c) on and off events generated by electrical simulation; (b) and (d) on and off events estimated from a numerical model. Event timing details are provided for the pixel on row 5 and column 5. . . . 57

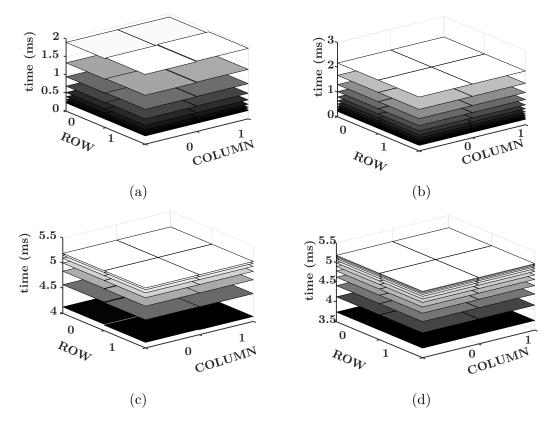

- 4.10 2 × 2 ATIS pixel array. Comparison between electrical simulation results and predictions based on the numerical model in Section 2.2.3:

(a) and (c) on and off events generated by electrical simulation; (b) and (d) on and off events estimated from a numerical model. . . . . 59

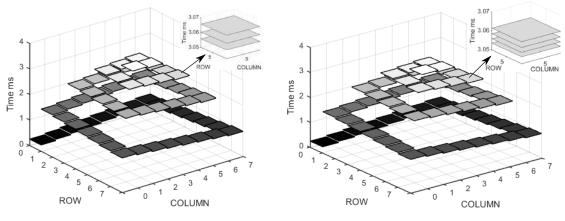

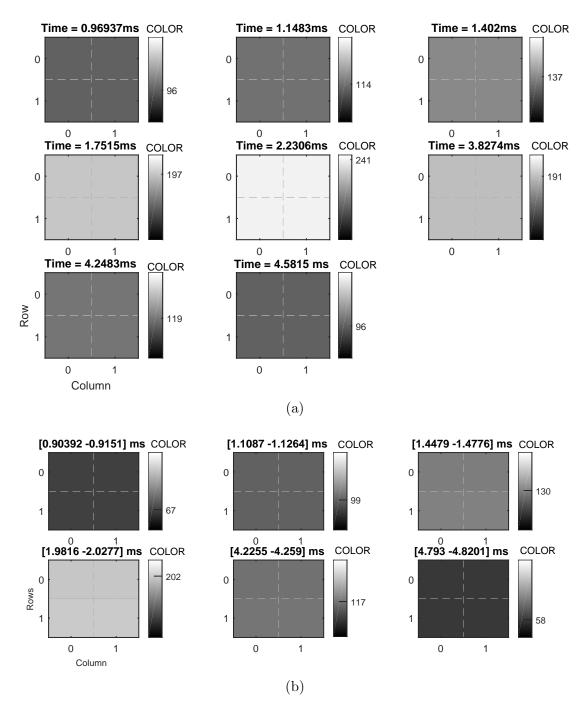

- 4.11 Brightness encoding results from (a) numerical simulations, and (b) electrical simulations, using the same photocurrent input with a time-domain triangular waveform for all pixels.

- 4.12 4 × 4 ATIS pixel array. Comparison between (a) decoded light intensity predictions based on the numerical model in Section 2.2.3, and(b) decoded light intensity values obtained from an electrical simulation. 61

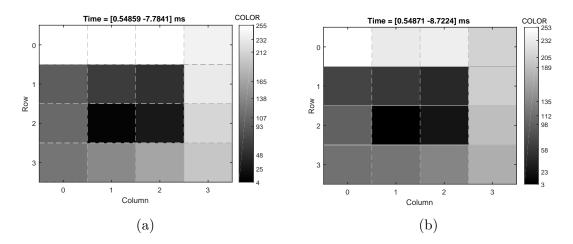

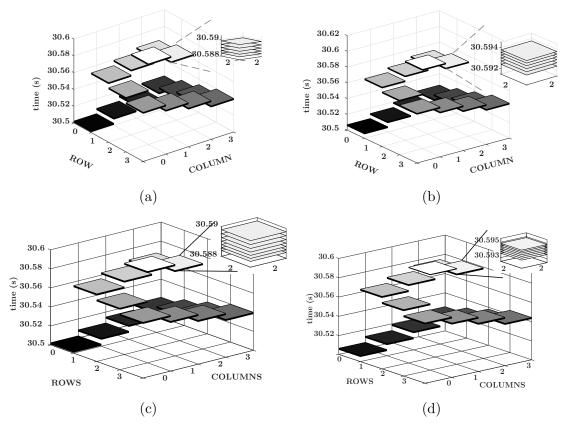

4.13 4 × 4 ADMDVS pixel array. Comparison between electrical simulation results and predictions based on the numerical model in Section

2.3.2: (a) and (b) on and off events generated by electrical simulation; (c) and (d) on and off events estimated from a numerical model. Event timing details are provided for the pixel on row 2 and column 2. 62

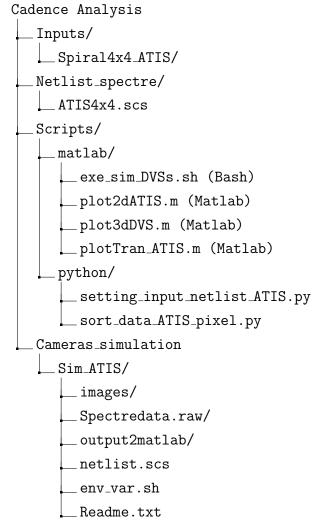

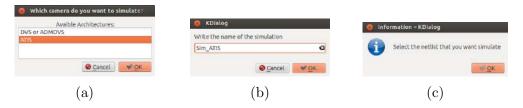

| A.1 | Simulation configuration, first step: (a) pixel array type selection, (b)             |    |

|-----|---------------------------------------------------------------------------------------|----|

|     | simulation name assignment, and (c) confirmation. $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 71 |

| A.2 | Simulation configuration, second step: (a) netlist selection, and (b)                 |    |

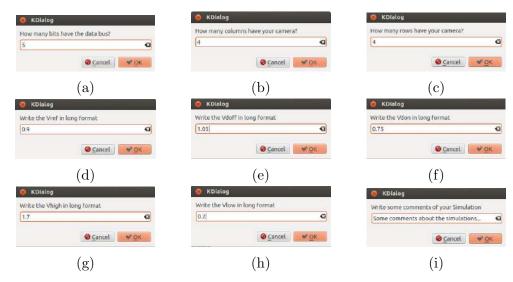

|     | input stimuli folder selection.                                                       | 72 |

| A.3 | Simulation configuration, third step: electrical simulation parameters.               | 72 |

# List of Tables

| 2.1 | DVS pixel input and output signals                                                                         | 5  |

|-----|------------------------------------------------------------------------------------------------------------|----|

| 2.2 | ATIS pixel input and output signals                                                                        | 11 |

| 3.1 | Two-stage operational amplifier transistor sizes                                                           | 38 |

| 3.2 | Active components within each pixel, and estimated area figures $% \left( {{{\bf{x}}_{{\rm{s}}}}} \right)$ | 47 |

| 4.1 | Quantity of spikes with different setting of comparator threshold per                                      |    |

|     | Channel and period signal                                                                                  | 51 |

# List of Abbreviations

| ADMDVS               | Asynchronous Delta Modulation DVS              |

|----------------------|------------------------------------------------|

| ADM                  | Asynchronous Delta Modulation                  |

| AER                  | Address-Event Representation                   |

| AMS                  | austriamicrosystems.com                        |

| APS                  | Active-Pixel Sensor                            |

| ATIS                 | Asynchronous Time-based Image Sensor           |

| CA                   | Column Acknowledgment                          |

| CCD                  | Charge-Coupled Device                          |

| CDS                  | Correlated Double Sampling                     |

| $\operatorname{CSV}$ | Comma-Separated Value                          |

| DC                   | Direct Current                                 |

| DI                   | Delay-Insensitive                              |

| DVS                  | Dynamic Vision Sensor                          |

| EKV                  | Enz, Krummenacher, and Vittoz                  |

| EM                   | Exposure Measurement                           |

| FPN                  | Fixed-Pattern Noise                            |

| GBW                  | Unity-Gain Bandwidth                           |

| KTC                  | Thermal noise, which is defined by Boltzmann   |

|                      | $\mathbf{r}$ and $\mathbf{r}$ and $\mathbf{r}$ |

- KTC Thermal noise, which is defined by Boltzmann constant k, temperature T, and capacitance C

- L Transistor channel length

- ME Mutual Exclusion

- MOS Metal-Oxide Semiconductor

- NDP Non-Dominant Pole

- Op Amp Operational Amplifier

- PWM Pulse Width Modulation

- QDI Quasi-Delay-Insensitive

- Q Quality Factor

- RA Row Acknowledgment

- SF Source Follower

- SR Reset Switch

- SS Signal Switch

- TCS Temporal Contrast Sensitivity

- TIA Transimpedance Amplifier

- W Transistor channel width

# Chapter 1

### Introduction

Nowadays people try to build systems with performance akin to their biological counterparts, but their objectives are in general still far from the reality. Small insects still outperfom powerful computing machines in executing several tasks involving a balanced combination of real-time data processing, control systems, sensory systems, and the optimization of bandwidth and power consumption [1].

Carver Mead, from the California Institute of Technology, introduced in the 80's the concept of *neuromorphic* systems [2], to refer to systems which try to mimic some of the properties of biological neural architectures. Systems based on the neuromorphic approach are, in some aspects, more efficient than conventional designs. A vision sensor inspired on biological retinas, for example, only generates outputs when it detects spatial or temporal changes in its inputs, whereas conventional video sensors are continuously generating output data regardless of changes occurring or not within their fields of view.

Image sensors have evolved greatly since the 70's. The first charge-coupled imaging devices (CCDs) were built around 1969 by Willard Boyle and George Smith at the AT&T Labs [3]. A CCD is composed by an adjacent association of chargecoupled capacitors which are sensitive to light. The implementation usually adopts one of three different architectures [4]: full-frame transfer, frame transfer, and interline transfer. From one architecture to another, the shuttering approach changes. The active-pixel sensor (APS) came out some years later, around the middle 80's [5], [6]. The APS is a metal-oxide semiconductor (MOS) image sensor. The APS pixel typically includes a photodiode, which generates a current proportional to the incident light intensity, and at least three transistors: i) a reset transistor, which is used for clearing charge that has been integrated at the photodiode cathode terminal, ii) an amplifying transistor usually in source follower configuration, and iii) a switch that either blocks or allows pixel read-out. Contrary to CCD the MOS imagers (i.e. APS image sensor) do not use charge transfer to convey the data information to external (off-chip) system. Both the CCD and the APS have been widely used in many applications: scientific surveys, astronomy, satellite imaging, consumer video, cell phones, webcams, and so forth.

In frame-based image sensors, either CCD or APS, the integration time is set according to a global shutter. Many vision sensors follow the frame-based approach. Differently from frame-based vision sensors, the biological retinas do not use the 'frame' concept. They generate output data asynchronously and their data output depends on specific features detected in the sensor field of view. To inform what type of event is being captured, specific structures, for example parvo-cellular and magno-cellular pathways, exist in the biological retina [2].

As neuromorphic engineering expands quickly, some properties of biological vision systems are successfully mimicked today. According to the biological structure examples mentioned in the previous paragraph, vision sensors inspired on biological vision systems are roughly divided into two categories: i) *Spatial Contrast* sensors, which reduce spatial redundancy by replicating aspects of the parvo-cellular pathway [7], [8]; and ii) *Temporal Contrast* sensors, which reduce temporal redundancy by replicating aspects of the magno-cellular pathway [7], [8].

One of the most important vision sensors in the neuromorphic engineering field is the Dynamic Vision Sensor (DVS). The DVS arose from the CAVIAR Project<sup>1</sup>, where the CAVIAR acronym stands for *Convolution Address-Event Representation* (AER) *Vision Architecture for Real Time*. The DVS was the first event-based commercial vision sensor to respond asynchronously to temporal changes. Its output information is encoded by short voltage pulses informally denoted as *spikes*, and the spikes are conveyed to subsequent systems via AER protocols [9]. Temporal waveforms containing spike sequences are informally denoted as *spike trains*. The DVS approach mimicks its biological counterpart, and this approach is usually referred to as the *frame-free* vision sensor.

The DVS has some advantages with respect to frame-based vision sensors. As the DVS pixels only respond to temporal changes, asynchronously and through spike trains, they reduce bandwidth and power consumption, whereas the pixels in framebased sensors have their values transmitted even if no change occurs within the field of view. As the DVS does not have a global shutter, each pixel independently defines its own operation point. Since the DVS invention, research has focused on including additional features that are similar to those found in biological retinas. Pixels with larger temporal contrast sensitivity have been proposed [10], [11]. To efficiently encode light intensity temporal variations, other designs focus on asynchronous timebased modulation [12], [13].

<sup>&</sup>lt;sup>1</sup>http://www2.imse-cnm.csic.es/caviar/introduction.htm

### 1.1 Objectives

This work aims at studying a few different DVS architectures and comparing them. In particular, this work focuses on three architectures: basic DVS, asynchronous time-based image sensor (ATIS), and asynchronous delta modulation DVS (AD-MDVS). Available architectures are analyzed and comparison methods are proposed. To accomplish that task, specific goals were defined:

- Studying bibliography references about free-frame vision sensors (Chapter 2);

- Modelling selected architectures at the system level, in a numerical environment (Chapter 2);

- Studying  $g_m/I_D$  methodology<sup>2</sup> [14] for DVS design (Chapter 2);

- Designing and simulating a single instance for each pixel (Chapters 3 and 4);

- Building input stimulus files that are suitable for pixel model validation (Chapter 4);

- Designing and simulating a small pixel array (i.e. an array with a few pixels) in order to validate pixel operation when two or more pixels simultaneously detect light intensity temporal change (Chapter 4);

- Using different programming languages, to make the test phase automatic (appendices)

### 1.2 Text Organization

In Chapter 2 we will explain basic DVS concepts, including models for each pixel that is studied in this dissertation. In Chapter 3, pixel design details are presented, including a suitable application of  $g_m/I_D$  methodology to pixel design. Chapter 3 also contains an innovative delay comparator design, not found in the papers we studied, that affects the exposure measurement logic in the ATIS architecture. Comparisons among pixel models, based on electrical simulation results, are presented in Chapter 4. The main conclusions and some future research topics are presented in Chapter 5. Some algorithms required for the simulation of a small ATIS camera are included in the appendices.

$<sup>{}^{2}</sup>g_{m}/I_{D}$  is a design method which is used to design integrated circuit based on the efficiency of the transistor transconductance (Section 2.6). We use EKV (Enz, Krummenacher, and Vittoz) model for modelling DVS sensor (Section 2.1.1). The  $g_{m}/I_{D}$  ratio can be obtained using transistor models (i.e. EKV model). The  $g_{m}/I_{D}$  method was used for designing the operational amplifier (Section 3.2) and voltage comparator with hysteresis (Section 3.3).

## Chapter 2

## Theory

In this chapter, we address fundamental concepts about the DVS options studied in this work. The pixel models are described. An introduction to asynchronous circuits, delay models, and AER systems is provided. These explanations lead to an understanding of how a reduced number of bits represents, in the frame-free vision sensor, light intensity values from all pixels in the array. Additional pixel operation details are provided in subsequent chapters.

### 2.1 Dynamic Vision Sensor

The DVS pixel responds to temporal contrast changes, instead of the absolute light intensity sampled at the pixel location. The DVS pixel behavior is inspired by the behavior of neurons in the magno-cellular pathway of a biological vision system [2]. They are primarily sensitive to temporal changes in incoming light intensity (sampled by photoreceptors at the retina), and they tend to ignore constant light intensity values. The temporal contrast in DVS sensors is defined by Equation (2.1) [15]:

$$TCON = \frac{1}{I(t)} \frac{dI(t)}{dt} = \frac{d(\ln(I(t)))}{dt},$$

(2.1)

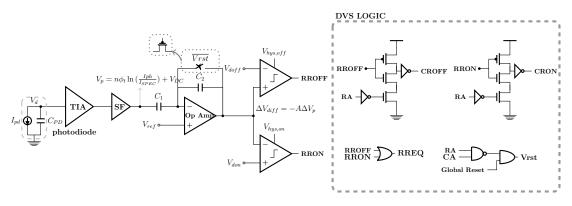

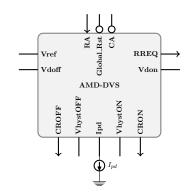

where I(t) is the photocurrent at the local photodiode. Autonomously, the DVS pixel transmits temporal change information through two asynchronous communications channels, also found in the biological vision system, which are denoted as on and off channels [2]. Figure 2.1 indicates that the DVS pixel uses a logarithmic photoreceptor, a circuit for the computation of temporal derivatives with gain equal to  $C_1/C_2$ , two voltage comparators, and a logical circuit for AER communication. Each block is described next.

The original DVS schematic diagram [4], [15] is simpler than the one shown in Figure 2.1. In the original schematic diagram, the temporal derivative circuit

Figure 2.1: Pixel schematic diagram.

| Table $2.1$ : | DVS | pixel | input | and | output signals. |  |

|---------------|-----|-------|-------|-----|-----------------|--|

|---------------|-----|-------|-------|-----|-----------------|--|

| Object Name   | I/0 | Object Description                                                          |

|---------------|-----|-----------------------------------------------------------------------------|

| $V_{ref}$     | In  | Starting voltage level (between $V_{doff}$ and $V_{don}$ ) for DVS pixel    |

| $V_{doff}$    | In  | Off event minimum absolute voltage threshold                                |

| $V_{don}$     | In  | On event minimum absolute voltage threshold                                 |

| Global Reset  | In  | Global command (active at low level) for resetting pixel value to $V_{ref}$ |

| $V_{hys,off}$ | In  | Voltage reference for hysteresis loop in off comparator                     |

| $V_{hys,on}$  | In  | Voltage reference for hysteresis loop in <i>on</i> comparator               |

| $I_{pd}$      | In  | Photodiode current that is due to the photoelectric effect                  |

| $V_d$         | -   | Photodiode cathode terminal                                                 |

| RREQ          | Out | Data bus pixel request (active at high level)                               |

| CRON          | Out | Positive temporal contrast change indication (active at high level)         |

| CROFF         | Out | Negative temporal contrast change indication (active at high level)         |

| RA            | Out | Row AER (Y-AER) acknowledgment, which enables row data                      |

|               |     | transmission                                                                |

| CA            | Out | Column AER (X-AER) acknowledgment                                           |

is implemented by a single common-source amplifier, and the voltage comparators are implemented by logical inverters with independent inputs. In the present work, the common-source amplifier was replaced by a conventional two-stage operational amplifier, and the logical inverters were replaced by two-stage voltage comparators with hysteresis [16]. We decided to replace those parts of the original circuit by these more complex ones for two reasons: i) in the common-source configuration, after an event has occurred, its output is taken to the operation point  $V_{ref}$  because of a short circuit between the gate and drain voltages. The temporal derivative circuit is thus converted into a diode-connected circuit with an active load<sup>1</sup>. For power consumption savings, we would like the analog circuits to operate in the subthreshold regime, and so the bias voltage at the p-channel transistor gate is at least 1.5 V (assuming that the supply voltage is 1.8 V and the transistor threshold voltage is around 0.3 V). To make operation point adjustment easier, we use an

<sup>&</sup>lt;sup>1</sup>The common-source amplifier uses one p-channel transistor (input) and one n-channel transistor (current source). When a reset takes place, the gate and drain terminals of the p-channel transistor are connected, which turns the p-channel transistor into a diode forward biased by a current source (which is the n-channel transistor). The common-source amplifier output is taken to  $V_{ref}$ .

operational amplifier. The operational amplifier has two inputs, while the commonsource amplifier has only one. The  $V_{ref}$  voltage in the common-source amplifier is defined by the bias current, while in the operational amplifier the  $V_{ref}$  voltage is defined at its non-inverting input, and the bias current does not depend on  $V_{ref}$ ; ii) using logical inverters as voltage comparators leads to large MOS transistors, and it is not possible to obtain hysteresis with them. To make comparator operation robust to input noise, using comparators with hysteresis is desirable. To reduce area and power consumption, we use a classical two-stage voltage comparator with hysteresis.

The original DVS has several advantages over conventional frame-based cameras. It only responds to input changes, thus leading to reduced bandwidth data transmission. Because of AER, a few bits represent any pixel in the sensor array. Although the data redundancy is reduced, the timing information is accurately preserved. As the DVS pixel response is independently composed by asynchronous spikes, power consumption is reduced as well. Depending on temporal contrast, each input event is simply classified as either an *on* or an *off* event. As the pixel reset signal (to establish the pixel operating point) is self-generated, an external clock is not required.

The DVS pixel (Figure 2.1) is basically composed by five building blocks, which are described next. For clarity, the symbols representing input and output signals in Figure 2.1 are described in Table 2.1.

- 1. Logarithmic Transimpedance Amplifier (TIA): this amplifier logarithmically converts a photocurrent signal into a voltage-mode signal. The circuit is designed to rapidly respond to temporal changes. As the  $V_d$  node is kept at virtual ground, the transimpedance amplifier bandwidth is increased;

- 2. Source Follower (SF): this amplifier drives the large capacitive load that is present at the input of the circuit for temporal derivative computation;

- 3. Temporal Derivative Circuit: this circuit amplifies, with gain equal to  $C_1/C_2$ , relative changes in log intensity that take place after the latest reset [15]. The DC signal component is cancelled. If the pixel detects a temporal contrast change event, and if this event is acknowledged by an off-chip acknowledgment system<sup>2</sup>, then the temporal derivative circuit output is reset to the starting voltage level ( $V_{ref}$ , according to Table 2.1). After that, the temporal contrast change detection process restarts. The differencing circuit output keeps increasing (negative temporal contrast change) or decreasing (positive temporal

<sup>&</sup>lt;sup>2</sup>The AER systems (row and column) generate acknowledgment signals. The simplest implementation of an acknowledgment system involves delays (logical inverter pairs). The output of the highest level arbiter generates a delayed version of RREQ, which returns to the ACK input (Figure 3.10) for self-acknowledgment.

contrast change). It returns to  $V_{ref}$  after a request (threshold crossing) is acknowledged.

The DC signal component is cancelled. If the pixel detects a temporal contrast change event, and if this event is acknowledged by an off-chip acknowledgment system, then the temporal derivative circuit output is reset to the starting voltage level ( $V_{ref}$ , according to Table 2.1). After that, the temporal contrast change detection process restarts;

- 4. Comparators: to decide whether the temporal contrast change was large enough to generate an event, the DVS pixel uses two voltage comparators. The arbitrary thresholds that are set by both comparators define the pixel temporal contrast sensitivity (TCS). Comparator outputs are connected to a logical interface. The comparators also feature hysteresis, and the hysteresis voltage range may be defined by means of a control voltage, which is denoted as  $V_{hyst}$  in Figure 2.1. The RROFF signal indicates that the temporal contrast change event was negative, and the RRON signal indicates that the temporal contrast change event was positive;

- 5. Logical Interface: to establish a handshaking protocol with an AER circuit, a logical interface generates a reset signal, which is denoted as  $V_{rst}$  in Figure 2.1, after the temporal contrast change event was acknowledged by an external (off-chip) system.

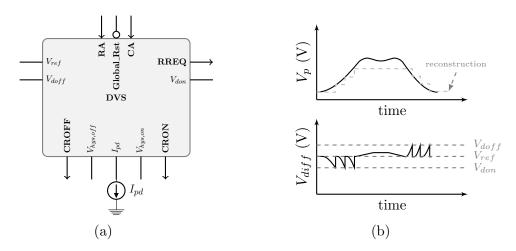

Figure 2.2a illustrates the DVS pixel as a building block. This building block has the same input and output signals that were already described in Table 2.1. The DVS pixel operation is illustrated by the diagram in Figure 2.2b. In Figure 2.2b, the solid curve at the top refers to the photodiode cathode voltage, after amplification by the transimpedance amplifier and the source follower blocks, which is denoted as  $V_p$ . The dotted line corresponds to an approximate  $V_p$  reconstruction, which is obtainable from the pulses shown at the bottom plot. This bottom plot of Figure 2.2b shows the pulses generated at the temporal derivative circuit output, which is denoted as  $V_{diff}$ . The  $V_{diff}$  signal is obtained by integrating the  $\Delta V_{diff}$  signal in Figure 2.1. The comparators continuously verify whether  $V_{diff}$  exceeds on or off threshold levels, which are denoted as  $V_{don}$  and  $V_{doff}$  in Figure 2.1 and Table 2.1. If the  $V_{diff}$  absolute value corresponds to sufficiently high temporal contrast change, then one of the comparator outputs changes into 'active' (e.g. high voltage level), which means that the pixel requests data bus access in order to transmit that high temporal contrast change event. This activity starts communication with an external AER circuit. After the pixel request is acknowledged by the AER circuit, the AER circuit sends a reset signal back to the pixel. This reset signal brings the operation point (i.e. the output  $V_{diff}$  voltage level) back to  $V_{ref}$ , which means that the pixel is ready to detect new temporal contrast change events.

Figure 2.2: DVS pixel instance. (a) DVS pixel as a system building block, and (b) DVS pixel operation fundamentals, adapted from [15].

Because of transistor mismatch (threshold voltage and geometrical aspect variation) at the photoreceptor level, the DVS pixel array suffers from a high mismatch among the pixels. That mismatch is partially compensated by using temporal derivative circuits with an accurate gain, which is obtained by carefully matching the capacitors that realize the  $C_1/C_2$  ratio [4], [10], [15].

#### 2.1.1 DVS Pixel Model

The following analysis is based on [10]. Using the EKV (Enz, Krummenacher, and Vittoz) model for subthreshold regime operation [17], the  $V_{diff}$  signal can be modelled by Equation (2.4). To obtain the  $V_{diff}$  signal we need to find the source follower output as next:

$$V_p = n\phi_t \ln\left(\frac{I_{pd}}{I_s}\right) + V_{DC} \tag{2.2}$$

where n is the subthreshold slope factor,  $\phi_t$  is the thermal voltage,  $I_s = 2n\phi_t^2 K p W/L$ is the subthreshold current factor of a MOS transistor,  $V_{DC} = V_d + V_T$ , W is transistor channel width and L is transistor channel length. Because of  $V_p$  feeds the differencing circuit then we have that:

$$dV_{diff} = -AdV_p$$

=  $-\frac{C_1}{C_2}n\phi_t d\ln\left(\frac{I_{pd}}{I_{spec}}\right)$

=  $-\frac{C_1}{C_2}n\phi_t d\frac{I_{pd}}{I_{pd}}$  (2.3)

Integrating Equation (2.3) we have  $V_{diff}$  equal to:

$$V_{diff} = -\frac{C_1}{C_2} n\phi_t \ln\left(I_{pd}\right) \tag{2.4}$$

To define whether temporal contrast change is positive or negative, the  $V_{diff}$  signal is compared to two threshold voltages, which are denoted as  $V_{diff,on}$  and  $V_{diff,off}$  in Equations (2.5) and (2.6). The  $V_{diff,on}$  threshold voltage is negative, and the  $V_{diff,off}$  threshold voltage is positive. To define  $V_{diff,on}$ , we compute the difference between  $V_{don}$  and  $V_{ref}$ , taking into account the fact that  $V_{don}$  sets the threshold for a minimum voltage (relative to  $V_{ref}$ ) that is required for firing an on event. The  $V_{don} - V_{ref}$  voltage difference is compensated by  $V_{os,comp} + V_{os,opamp}$ . The  $V_{os,comp}$  voltage represents the offset voltage at the comparators, and  $V_{os,opamp}$  represents the offset voltage at the temporal derivative circuit. The definition of  $V_{diff,off}$  is similar to the definition of  $V_{diff,on}$ , but it is based on  $V_{doff}$ , which sets the threshold for a maximum voltage (relative to  $V_{ref}$ ) that is required for firing an off event.

$$V_{diff,on} = (V_{don} - V_{ref}) + (V_{os,comp} + V_{os,opamp}) < 0$$

$$(2.5)$$

$$V_{diff,off} = (V_{doff} - V_{ref}) + (V_{os,comp} + V_{os,opamp}) > 0$$

$$(2.6)$$

To compute the minimum temporal contrast inputs that generate events (either on or off events), we define  $\theta^+$  as the minimum temporal contrast that generates an on event. Similarly,  $\theta^-$  is the minimum temporal constrast that generates an off event. Integrating Equation (2.3) yields

$$\theta^{+} = \left| \ln \frac{I_{bright}}{I_{dark}} \right| = \left| \frac{V_{diff,on}C_2}{C_1 n \phi_t} \right|$$

$$= \left| \frac{C_2((V_{don} - V_{ref}) + (V_{os,comp} + V_{os,opamp}))}{C_1 n \phi_t} \right|$$

$$\theta^{-} = \left| \ln \frac{I_{dark}}{I_{bright}} \right| = \left| \frac{V_{diff,off}C_2}{C_1 n \phi_t} \right|$$

$$= \left| \frac{C_2((V_{doff} - V_{ref}) + (V_{os,comp} + V_{os,opamp}))}{C_1 n \phi_t} \right|$$

(2.7)

(2.8)

(2.8)

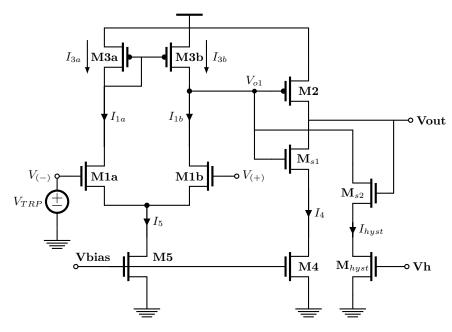

#### 2.2ATIS Pixel

Improving the dynamic range of vision cameras is currently an active research topic. Using time-based encoding in CMOS technology improves pixel performance with respect to dynamic range [16], [18]. Each pixel may choose its own integration time, as it responds to input variations in autonomous and asynchronous fashion.

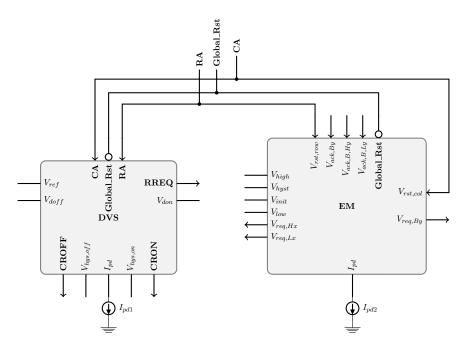

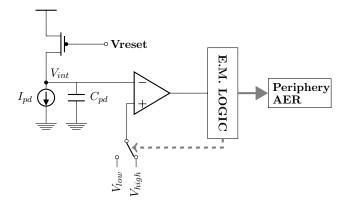

Like the DVS, the ATIS pixel is time-based. It was conceived in an attempt to mimic the magno-cellular and parvo-cellular pathways of biological vision systems. Roughly speaking, the magno-cellular pathway uses a spatially coarse representation system, which allows for quick detection of a new incoming event. The parvo-cellular pathway focuses on the event detailed description, thus allowing for a definition of the object that generated the incoming event [2]. As Figure 2.3 shows, the ATIS pixel is composed by one DVS pixel, which works as a temporal change detector, and one exposure measurement (EM) circuit, which encodes the light intensity associated with the event generated by the DVS pixel. The DVS pixel roughly plays the role of a magno-cellular pathway input, whereas the exposure measurement circuit plays the role of a parvo-cellular pathway input.

Similarly to its biological counterparts, the ATIS pixel presents voltage spike trains at its outputs. The spikes are generated in autonomous and asynchronous fashion by the ATIS pixel, and they simultaneously encode local brightness (luminance) information and temporal contrast change information. The ATIS pixel implements a particular correlated double sampling (CDS) [18] technique for KTC noise<sup>3</sup> and FPN (fixed pattern noise) removal [19], which is called True CDS. The True CDS technique is explained in Sections 2.2.1 and 2.2.2. To simultaneously detect temporal contrast change and measure light intensity, the ATIS pixel uses two photodiodes separately. As the brightness measurement cycle only starts after an event was generated, the ATIS temporal contrast sensitivity depends on the DVS pixel anyway. The ATIS camera thus uses two AER systems. The first one, which

<sup>&</sup>lt;sup>3</sup>Thermal noise on circuit capacitors is kT/C, where k is the Boltzmann constant, T is temperature, and C is node capacitance.

Figure 2.3: ATIS pixel instance, which is composed by a DVS pixel (left) and an exposure measurement circuit (right).

| Object Name          | I/0 | Object Description                                                          |

|----------------------|-----|-----------------------------------------------------------------------------|

| $V_{high}$           | In  | Voltage reference to start the brightness encoding process                  |

| Vlow                 | In  | Voltage reference to complete the brightness encoding process               |

| V <sub>hyst</sub>    | In  | Voltage reference for hysteresis loop in comparator                         |

| V <sub>init</sub>    | In  | Global command to bring the logic to valid state, it is used just once      |

|                      |     | in all operation                                                            |

| Global Reset         | In  | Global command (active at low level) for resetting pixel value to $V_{ref}$ |

| V <sub>rst,row</sub> | In  | Row acknowledgment from DVS (Y-AER), which enables row data                 |

|                      |     | transmission                                                                |

| $V_{rst,col}$        | In  | Column acknowledgment from DVS (X-AER)                                      |

| $V_{ack,By}$         | In  | Row acknowledgment from ATIS (Y-AER), which enables row data                |

|                      |     | transmission                                                                |

| $V_{ack,B,Hy}$       | In  | Column acknowledgment from ATIS (X-AER)                                     |

| $V_{ack,B,Ly}$       | In  | Column acknowledgment from ATIS (X-AER)                                     |

| $V_{req,By}$         | Out | Data bus pixel request to transmit its pixel encoding status                |

| $V_{req,Hx}$         | Out | Indicates that the pixel started the brightness encoding process            |

| $V_{req,Lx}$         | Out | Indicates that the pixel finished the brightness encoding process           |

Table 2.2: ATIS pixel input and output signals.

is based on the DVS pixel, encodes temporal contrast change events, and the second one encodes local brightness (local light intensity).

As it was previously mentioned in Chapter 1, time-based vision sensors such as DVS, ATIS, and so on, have some advantages over frame-based imagers (e.g. APS camera): reduced transmission bandwidth, as less data are generated by the pixel array; lower buffer storage requirements, as information pre-processing leads to less raw information; and simpler post-processing for image decoding. ATIS presents two particular advantages in addition to those ones: it encodes light intensity through pulse-width modulation (PWM), which is a very simple data transmission method,

and it improves signal-to-noise ratio, by means of True CDS.

In Sections 2.2.1 and 2.2.2, we will briefly discuss CDS concepts, in order to explain how CDS leads to better image quality in conventional image sensors. We will also address True CDS as a technique for enhancing the output signal in timebased vision sensors.

#### 2.2.1 Correlated Double Sampling (CDS)

To obtain high signal-to-noise ratio, which translates into good image quality, the pixel *readout noise* shall be kept low. Pixel readout noise is a generic expression that includes several types of noise [20]: the intrinsic noise present in pixel devices (dark signal non-uniformity and pixel response non-uniformity), KTC noise, 1/f (flicker) noise, and fixed pattern noise.

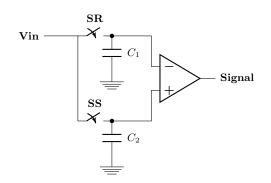

Correlated double sampling (CDS) is commonly used in CCD and APS cameras, in order to reduce readout noise. The pixel output is read (i.e. sampled) twice: one sampling operation captures the absolute signal value that is obtained by photocurrent integration in CCD and APS cameras, and another sampling operation captures the reset value. The output signal, which has less noise than the absolute signal value, is obtained by subtracting both samples, as shown in Figure 2.4. The reset switch (SR) is opened at the end of the reset phase, and the signal switch (SS) is opened at the end of the photocurrent integration. As any errors caused by pixel mismatch or process variations affect the absolute signal value and the reset value equally, those errors are cancelled at the differential amplifier output. For pixel read-out, the CDS approach in Figure 2.4 requires global control signals.

Figure 2.4: CDS schematic diagram.

#### 2.2.2 True Correlated Double Sampling

The true CDS technique was designed for time-based vision sensors, which is the ATIS case. This CDS method is referred to as *true* CDS because the double sampling is carried out in a single integration cycle, rather that within two subsequent

integration cycles, which corresponds to the basic CDS case. Keeping the two samples within the same integration cycle reduces reset noise (i.e. noise associated with the pixel reset voltage) by a factor approximately equal to 2 [18].

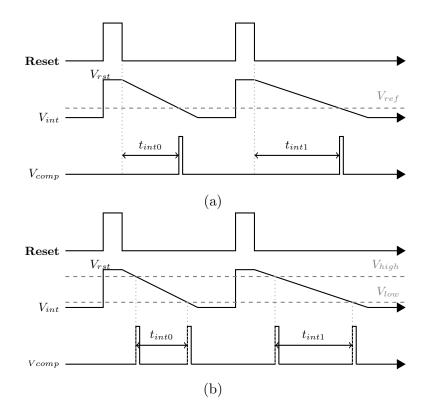

Figure 2.5 shows two possibilities (single threshold or two thresholds) for true CDS operation in a time-based vision sensor. In either case, an active (high level) reset pulse causes the photodiode cathode voltage ( $V_d$ , which is denoted by  $V_{int}$  in this figure) to be raised to the reset level that is denoted by  $V_{rst}$  in this figure. When the reset pulse is turned off, the photodiode depletion capacitance is discharged because of the photocurrent integration, which is illustrated by the oblique straight line segments in the figure. In the true CDS with a single threshold (Figure 2.5a), a voltage comparator generates an output  $(V_{comp})$  step, which is later shaped into a voltage pulse, when  $V_{int}$  reaches the threshold value  $V_{ref}$ . This indicates the end of the integration interval. The integration interval duration  $t_{int}$  is measured by the time difference between the comparator step rising edge and the reset pulse falling edge. It is inversely proportional to local light intensity. In the true CDS with two thresholds (Figure 2.5b),  $t_{int}$  does not depend on the photodiode reset level. In conventional photodiodes, the cathode voltage may fluctuate during the reset pulse, which is due to charge injection through the reset transistor among other uncertainty factors. Eliminating  $t_{int}$  dependence on the photodiode reset voltage thus improves signal accuracy by reducing reset noise, as mentioned in the previous paragraph. The upper threshold  $V_{high}$  is chosen according to the maximum expected photodiode reset error. The lower threshold  $V_{low}$  is chosen according to the maximum expected light intensity.

The true CDS implementation using a differential amplifier is shown in Figure 2.6. The exposure measurement logic controls the  $V_{low}$  and  $V_{high}$  threshold switches. It also requests AER encoding of the pixel event ( $V_{comp}$  pulse in Figure 2.5). The integrated light intensity signal is represented by the time difference between the pulses that are generated by threshold crossings at  $V_{high}$  and  $V_{low}$ . Figure 2.5b shows that, to obtain the time difference, only one integration cycle (between two reset pulses) is necessary. Comparator mismatch errors, as well as time delay differences between the threshold crossing events, tend to cancel out, which further reduces readout noise. The ratio between the sampling error  $\epsilon_{tint}$  (readout noise) and the readout signal  $t_{int}$  was evaluated for the single-threshold and two-threshold cases [18], and it was shown that the ratio is smaller if two thresholds are used. Furthermore, the analysis in [18] indicates that the ratio decreases as the supply voltage is reduced, which is convenient in modern CMOS technologies such as 180 nm, 110 nm, and so forth.

Figure 2.5: True CDS operation in time-based vision sensors: (a) single threshold, and (b) two thresholds [18].

Figure 2.6: True CDS implementation.

#### 2.2.3 ATIS Model

The ATIS temporal change detector is the DVS pixel itself. The exposure measurement logic is described in this section. When the reset signal is off, the photodiode cathode voltage is:

$$V_{int}(t) = \frac{1}{C} \int_0^t i_{pd}(\tau) d\tau + V_{int}(0) \qquad , t > 0,$$

(2.9)

where  $i_{pd}$  is the photocurrent, C is the photodiode cathode node capacitance, and  $V_{int}(0)$  is the initial condition. We assume  $V_{int}(0) = V_{DD}$ , which is the imager supply voltage. At first,  $V_{int}(t)$  is compared with  $V_{refh}$ . After  $V_{int}$  crossed the  $V_{high}$  and an

acknowledgement signal was received,  $V_{int}(t)$  is compared with  $V_{low}$ :

$$V_{out,EM} = \begin{cases} Req_{-}High, & \text{if } V_{int} \leq V_{high} \\ Req_{-}Low, & \text{if } V_{int} \leq V_{low} \end{cases}$$

(2.10)

The integration interval duration for a pixel is:

$$t_{int} = t(Req\_Low) - t(Req\_High).$$

(2.11)

If the temporal change detector detects another event before the light intensity measurement is completed, i.e. before  $V_{out,EM} = Req\_Low$ , then the off-chip AER system ignores the first request, which had happened when  $V_{int}$  crossed the  $V_{high}$  threshold, and it starts again.

To map  $t_{int}$  values into grayscale values, the  $t_{int}$  values are measured for different incoming light intensity values, say 256 different values, and the  $t_{int}$  measurements are stored in a look-up table. Using the look-up table, off-chip intensity value decoding is performed more accurately than through Equation (2.9).

#### 2.2.4 Additional ATIS Sensor Functionality

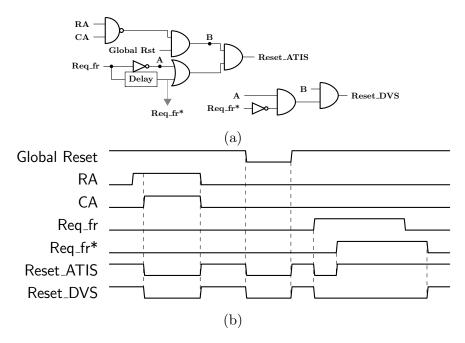

Besides reacting to temporal input changes and encoding light intensity values, the ATIS sensor may capture photographs [16], because the exposure measurement circuit does not remove the time-domain DC component of the input signal (which the DVS does remove). A logical circuit that enables asynchronous capture of static images in the ATIS sensor is proposed in Figure 2.7a. Using this logical circuit, each pixel decides its own integration time. To use the proposed circuit, minor modifications in the original ATIS pixel design are required Input and output signals are shown in Figure 2.7b.

If RA and CA (row and column acknowledgment) signals are received by the pixel, or if a global reset is active (at low level), then the pixel exposure measurement circuit and temporal change detector are reset (the Reset\_ATIS signal goes to the low level). To take a photo using ATIS, the temporal change detector must be blocked for time enough for reading out the information from all the pixels. For a short time, a reset signal is generated at the exposure measurement circuit Global\_-Rst input. The Req\_fr\* signal is a delayed version of Req\_fr, where the Req\_fr symbol stands for a *frame request* that is generated when the ATIS camera captures a photograph. The time delay is long enough for a stable reset voltage to be defined at the photodiode cathode. When both Req\_fr and Req\_fr\* are high, the exposure measurement circuit reset signal is turned off, and the integration interval starts. While Req\_fr or Req\_fr\* are high, the temporal change detector is blocked. Off-chip,

a frame-mode function would wait as the values from all pixels are read out. After light intensity information from all pixels has been received, this off-chip frame-mode function disables the Req\_fr signal.

Figure 2.7: Logical circuit enabling ATIS photograph capture: (a) schematic diagram, and (b) timing diagram.

In an ATIS camera that does not take pictures, the Reset\_DVS in Figure 2.7b is the same as the Reset\_ATIS signal. Otherwise, i.e. if the ATIS camera does take pictures, the Reset\_DVS signal is obtained from the logical circuit presented in Figure 2.7a.

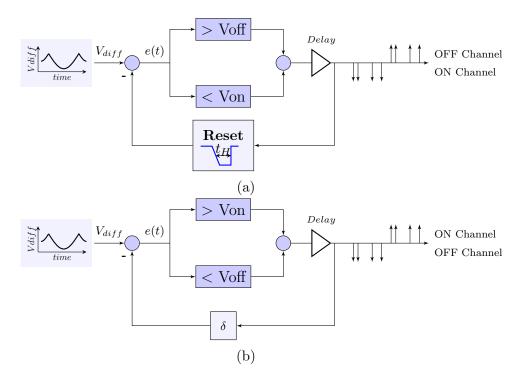

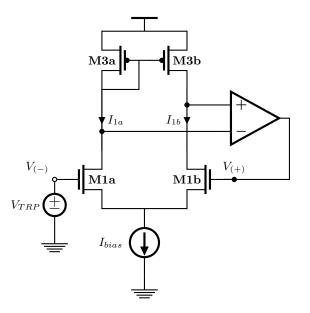

### 2.3 ADMDVS pixel

The ADMDVS pixel is an improved version of the DVS pixel. To reset the output signal to a starting voltage reference level after a temporal contrast change event, the ADMDVS pixel uses a modified version of asynchronous delta modulation (ADM) rather than the reset cycle that was used in the DVS pixel. The ADMDVS also uses a different information encoding method, which is denoted as feedback and subtract. The basic DVS encoding method is denoted as feedback and reset. Both encoding methods are shown in Figure 2.8. The feedback and reset method uses a reset switch to reset the operation point after a temporal contrast change event. The feedback and subtract method, instead of using a reset switch to reset the operation point after a temporal contrast change event. The feedback and subtract method, instead of using a reset switch to reset the operation point after a temporal contrast change event. The feedback and subtract method, instead of using a reset switch to reset the operation point after a temporal contrast change event. The feedback and subtract method, instead of using a reset switch to reset the operation point after a temporal contrast change event is fixed  $\delta$  value from the  $V_{diff}$  input. Whereas the feedback and reset method interrupts the input signal flow during the reset, in the feedback and subtract method the input signal flow is

never interrupted.

Figure 2.8: DVS information encoding methods: (a) feedback and reset and (b) feedback and subtract [21].

Figure 2.9 illustrates the ADMDVS pixel as a building block. It has the same input and output ports of the DVS pixel that was shown in Figure 2.2. The only difference at the instance symbol is that CA has been changed in order to be active at the low level, rather than high. The ADMDVS pixel uses the same AER system that is used by the DVS pixel.

Figure 2.9: ADMDVS pixel instance.

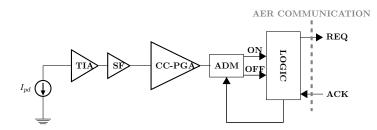

The ADMDVS pixel basic block diagram is shown in Figure 2.10. Differently from the conventional DVS sensor (Figure 2.2), which always produces *on* events even if temporal contrast change events do not occur [4], [15], [22], the ADMDVS pixel do not generate *on* events in the absence of input temporal change. The undesired *on* events are regarded as temporal noise, which is due to the reset transistor

charging (by means of source-to-bulk leakage current) the operational amplifier inverting input up to the supply voltage  $V_{DD}$ . The TIA block is the transimpedance amplifier. It is equal to the TIA in DVS and ATIS pixels. The SF (source follower) drives the large capacitive load that corresponds to the CC-PGA (capacitivelycoupled programmable gain amplifier) input. The CC-PGA replaces the differencing circuit in the DVS and ATIS pixels. The CC-PGA does not have a reset transistor, so that its input signal flow never gets interrupted. The ADM makes it possible to adjust the output level whenever an event occurs. Finally, logical circuits control all ADM switches and handle the communication links with AER systems.

Figure 2.10: ADMDVS basic block diagram [22].

In the original ADMDVS design [22], the authors propose using a programmable close loop gain, in order to make several TCS levels possible. We designed the differencing circuit with a fixed closed loop gain. In Section 2.3.1, we describe the implementation of the feedback and subtract encoding method in ADMDVS.

#### 2.3.1 ADM in DVS

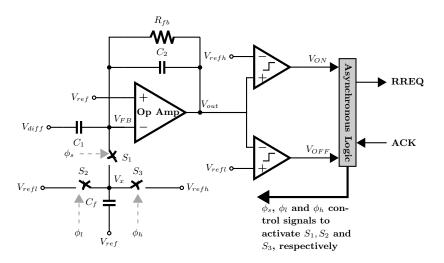

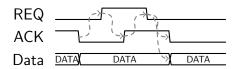

To understand how the ADM technique eliminates the DVS self-timed reset, we analyze the circuit in Figure 2.11. The operation of the circuit is as follows: initially, all switches are off. So, after some time we have  $V_{out} = V_{FB} = V_{ref}$ . Let us assume that, initially, there is a positive gradient (i.e. temporal variation) at the input  $V_{diff}$ , so that is starts, for example, to decrease. In that case,  $V_{out}$  would start to increase. If  $V_{out}$  increases enough, so that is crosses the  $V_{refh}$  threshold, then an *on* event is generated at  $V_{ON}$ . The *on* event is transmitted to an AER system external to the pixel array. The asynchronous logical circuit activates the  $S_3$  switch through  $\phi_h$  control signal, so that  $V_x$  reaches  $V_{refh}$ . The  $S_3$  switch remains active until an acknowledgment signal arrives from the AER system. After having received the acknowledgment signal, the asynchronous logical circuit actives the  $S_1$  switch through  $\phi_s$  control signal, which causes the  $V_{out}$  signal to be subtracted by a  $\delta$ value after some time. The  $\delta$  value is defined as  $|V_{refh} - V_{ref}|$ , which is equal to  $|V_{refl} - V_{ref}|$ .

Figure 2.11: Asynchronous delta modulation circuit [21].

Let us define  $t_1$  and  $t_2$  as the time instants at which  $S_3$  and  $S_1$  are activated. By taking into account the conservation of charge stored in  $C_1$ ,  $C_2$ , and  $C_f$ , we have [21]:

$$(V_{in}(t_1) - V_{FB}(t_1))C_1 + (V_{out}(t_1) - V_{FB}(t_1))C_2 + (V_{ref}(t_1) - V_x(t_1))C_f = (V_{in}(t_2) - V_{FB}(t_2))C_1 + (V_{out}(t_2) - V_{FB}(t_2))C_2 + (V_{ref}(t_2) - V_x(t_2))C_f \quad (2.12)$$

After  $V_{ref}$  was defined, it does not change during the entire exposure measurement interval. It is thus the same at  $t_1$  and at  $t_2$ . The same reasoning applies for  $V_{FB}$ . We also have  $V_{in}(t_1) \approx V_{in}(t_2)$ . We expect that at  $t_2$  the  $V_{out}$  signal reaches  $V_{ref}$ . Then,  $V_x(t_1) = V_x(t_2) + \delta$ . To simplify the analysis, we assume that  $C_f = C_2$ . Manipulating Equation (2.12) according to these assumptions yields:

$$V_{out}(t_2) = \begin{cases} V_{out}(t_1) - \delta, & \text{for an on event,} \\ V_{out}(t_1) + \delta, & \text{for an off event.} \end{cases}$$

(2.13)

This result is an approximation, because  $V_{in}$  is never interrupted (i.e. reset), so that  $V_{out}$  may be changing (i.e. increasing or decreasing) at any given time. The time delay that is created by the handshaking with the external AER system causes  $V_{out}$  not to reach  $V_{ref}$  exactly. The error in  $V_{out}$  accumulates across all measurement intervals, so that the number of spikes is somewhat higher (or lower) than the reference spike number that is obtained with zero time delay.

#### 2.3.2 ADMDVS Model

The ADMDVS pixel model is similar to the DVS pixel. The  $V_{diff}$  signal is the same, but the total closed loop gain is  $A = A_{diff}A_{ADM}$ , where  $A_{diff}$  is the differencing circuit closed loop gain, and  $A_{ADM}$  is the ADM circuit closed loop gain. Each request type is generated according to Equation (2.14), and the operating point after each event is computed according to Equation (2.15):

Request Type =

$$\begin{cases} on, & V_{out} > V_{refh}, \\ off, & V_{out} < V_{refl}, \\ no \ event, & otherwise. \end{cases}$$

(2.14)

The operating point for each event is calculated as:

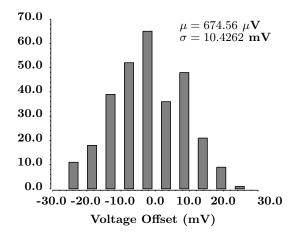

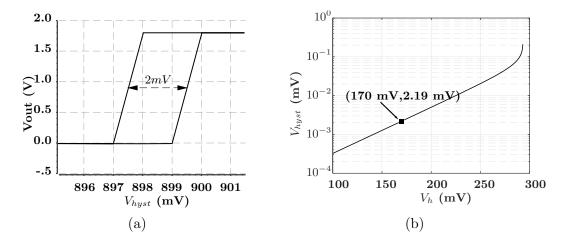

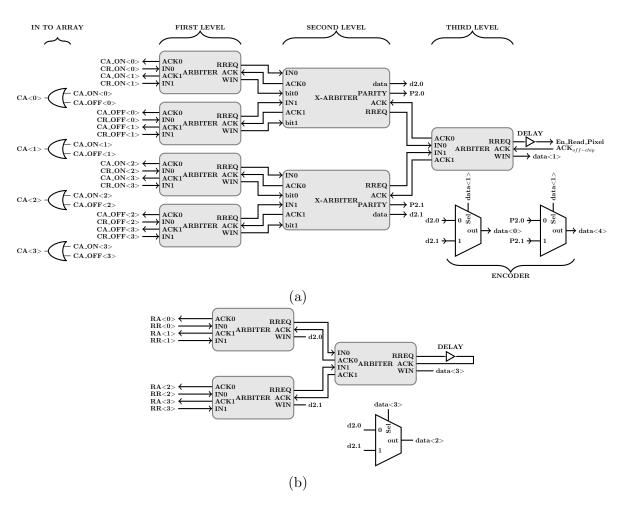

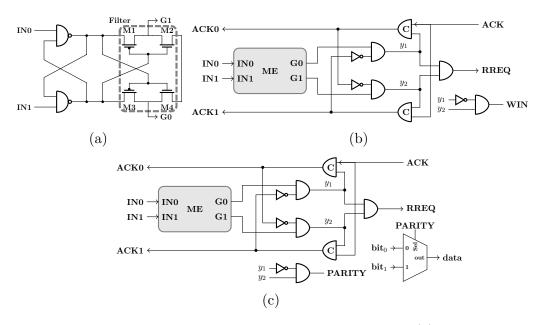

$$Operating Point = \begin{cases}