# **DESENVOLVIMENTO E APLICAÇÃO DE UM AMPLIFICADOR LOCK-IN BASEADO EM DSP**

Rafael Astuto Arouche Nunes

PROJETO SUBMETIDO AO CORPO DOCENTE DO DEPARTAMENTO DE ENGENHARIA ELÉTRICA DA ESCOLA POLITÉCNICA DA UNIVERSIDADE FEDERAL DO RIO DE JANEIRO COMO PARTE DOS REQUISITOS NECESSÁRIOS PARA A OBTENÇÃO DO GRAU DE ENGENHEIRO ELETRICISTA.

Aprovada por:

---

Prof. José Luiz da Silva Neto, Ph.D.

(Orientador)

---

Prof. Marcelo Portes de Albuquerque, Ph.D.

(Co-Orientador)

---

Prof. Sergio Sami Hazan, Ph.D.

RIO DE JANEIRO, RJ - BRASIL

AGOSTO DE 2009

# **Dedicatória**

Quando pensei em para quem dedicar esta obra, não tive dúvidas, seria para meu irmão! Bruno Astuto Arouche Nunes, ou melhor, apenas Bruno! Sempre comigo, sempre me ajudando, me apoiando, ao meu lado em todos os momentos importantes da minha vida. E durante meu projeto final não poderia ser diferente.

Quero dedicar todo este feito à você Bruno, que mais do que um irmão mais velho é meu melhor amigo, um companheiro e tanto!

Obrigado por tudo que você é na minha vida, te amo!

# Agradecimentos

Primeiramente agradeço à Deus.

Agradeço de forma extremamente especial aos meus pais Marcos Arouche Nunes e Miriam Cristina Astuto por todo apoio fornecido durante minha jornada acadêmica. Sem eles nada do que sou e nenhuma conquista em minha vida seria possível. Sempre estiveram ao meu lado me apoiando e me incentivando, mas ao mesmo tempo me guiando e me mostrando o melhor caminho em todas minhas decisões. Esta obra só foi possível graças à existência de pais maravilhosos como estes, que com toda certeza do mundo posso afirmar e glorificar: melhores não há!

É com imenso orgulho que reforço de maneira carinhosa e especial um agradecimento ao meu pai, que nunca me disse o que fazer, mas sempre me mostrou o melhor caminho a seguir. Obrigado pai, essa obra é para você!

Com grande amor, agradeço e dedico este projeto também à minha namorada Daniela que durante estes quase sete anos juntos, sempre me apoiou e esteve ao meu lado em todas as situações, nos momentos bons e ruins, nas horas de alegria e de tristeza. Amor, que esta seja apenas a primeira vitória juntos, pois ao lado de Deus tenho certeza de que muitas conquistas ainda iremos alcançar! Você também faz parte deste projeto! Sem sua ajuda incondicional nada disso teria se realizado! Te amo!

Agradeço ao meu orientador de iniciação tecnológica, Marcelo Portes de Albuquerque, que esteve comigo durante quase quatro anos me apoiando e muito me ensinando. De fato um mestre, ou melhor, um doutor, com sabedoria ímpar e carisma incomum na área. Espero ainda poder realizar muitas conquistas ao lado deste, que mais do que meu professor, tornou-se um grande amigo.

Agradeço ao professor Zé Luiz que acreditou no potencial do projeto do Lock-In e me deu um voto de confiança a aceitá-lo como tema do meu projeto final.

Obrigado Shigeko pela ajuda durante o projeto final na fabricação dos sensores ultra-som.

Obrigado ao CNPq pela ajuda financeira fornecida durante quase quatro anos de bolsa de iniciação tecnológica no CBPF.

Obrigado a UFRJ pelos seis anos de ensino de extrema qualidade.

# Índice

|                                                  |           |

|--------------------------------------------------|-----------|

| <b>LISTA DE FIGURAS</b>                          | <b>7</b>  |

| <b>LISTA DE TABELAS</b>                          | <b>11</b> |

| <b>INTRODUÇÃO</b>                                | <b>12</b> |

| Tema                                             | 12        |

| Justificativa                                    | 12        |

| Objetivos                                        | 13        |

| Metodologia                                      | 14        |

| Descrição                                        | 14        |

| <b>CAPÍTULO 1</b>                                | <b>16</b> |

| <b>O AMPLIFICADOR LOCK-IN</b>                    | <b>16</b> |

| 1.1 – Introdução                                 | 16        |

| 1.2 – Lock-In Digital                            | 18        |

| 1.3 – Detecção Sensível à Fase                   | 19        |

| <b>CAPÍTULO 2</b>                                | <b>23</b> |

| <b>SIMULANDO UM <i>LOCK-IN</i></b>               | <b>23</b> |

| 2.1 –Algoritmo Base                              | 23        |

| 2.2 –Definição da Experiência                    | 24        |

| 2.3 – Desenvolvimento de um Simulador            | 29        |

| 2.4 – Análise de Resultados                      | 30        |

| 2.5 – Comportamento do Desvio Padrão das Medidas | 36        |

| 2.6 – Conclusões                                 | 37        |

| <b>CAPÍTULO 3</b>                                | <b>38</b> |

|                                                                                  |           |

|----------------------------------------------------------------------------------|-----------|

| <b>DSP ALTERA STRATIX II EP2S60</b>                                              | <b>38</b> |

| <b>3.1 – Altera Stratix® II EP2S60 DSP</b>                                       | <b>38</b> |

| <b>3.1.1 – Descrições gerais do kit</b>                                          | <b>40</b> |

| <b>3.2 – USB Blaster</b>                                                         | <b>41</b> |

| <b>3.3 – DSP Builder</b>                                                         | <b>42</b> |

| <b>3.4 – Utilizando o kit Stratix II EP2S60</b>                                  | <b>43</b> |

| <b>3.4.1 – Conversores A/D</b>                                                   | <b>45</b> |

| <b>3.4.2 – Conversor D/A</b>                                                     | <b>45</b> |

| <b>CAPÍTULO 4</b>                                                                | <b>46</b> |

| <b>RESULTADOS</b>                                                                | <b>46</b> |

| <b>4.1 – Interface com Matlab</b>                                                | <b>46</b> |

| <b>4.2 – Resultados</b>                                                          | <b>46</b> |

| <b>4.2.1 – Medições de Magnitude</b>                                             | <b>46</b> |

| <b>4.2.2 – Medições de Fase</b>                                                  | <b>50</b> |

| <b>CAPÍTULO 5</b>                                                                | <b>53</b> |

| <b>UTILIZAÇÃO DE ULTRA-SOM PARA MEDIÇÃO DE ESPESSURA DE AMOSTRAS DE ALUMÍNIO</b> | <b>53</b> |

| <b>5.1 – O Experimento</b>                                                       | <b>53</b> |

| <b>5.2 – Resultados das Medições</b>                                             | <b>58</b> |

| <b>5.3 – Conclusões</b>                                                          | <b>62</b> |

| <b>APÊNDICE A</b>                                                                | <b>63</b> |

| <b>ALGORITMO BASE PARA O <i>LOCK-IN</i></b>                                      | <b>63</b> |

| <b>APÊNDICE B</b>                                                                | <b>65</b> |

| <b>CÓDIGO FONTE PARA O SIMULADOR DE <i>LOCK-IN</i></b>                           | <b>65</b> |

| <b>APÊNDICE C</b>                                                                | <b>68</b> |

| <b>O DSP</b>                                                                     | <b>68</b> |

| <b>C.1 – Introdução</b>                                                          | <b>68</b> |

| <b>C.2 – O Começo</b>                                                            | <b>69</b> |

|                                             |           |

|---------------------------------------------|-----------|

| <b>C.3 – Aplicações</b>                     | <b>70</b> |

| C.3.1 – Freios Anti-Travamento (ABS)        | 70        |

| C.3.1 – Compressão e Descompressão de Sinal | 71        |

| C.3.2 – Filtros Digitais                    | 72        |

| <b>C.4 – Desenvolvimentos de Projetos</b>   | <b>74</b> |

| <b>C.5 – A Estrutura de um DSP</b>          | <b>77</b> |

| <b>C.6 – Exemplos</b>                       | <b>78</b> |

| <b>REFERÊNCIAS BIBLIOGRÁFICAS</b>           | <b>82</b> |

# Listas de Figuras

|            |                                                                                                                                                                                                                                                                                                                                                      |    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 1   | Princípio da detecção síncrona (ou demodulação) para medir o atraso de um sinal de referência em relação a um sinal de um sistema físico.                                                                                                                                                                                                            | 13 |

| Figura 1.1 | Esquemático simplificado de um Amplificador <i>Lock-In</i> .                                                                                                                                                                                                                                                                                         | 17 |

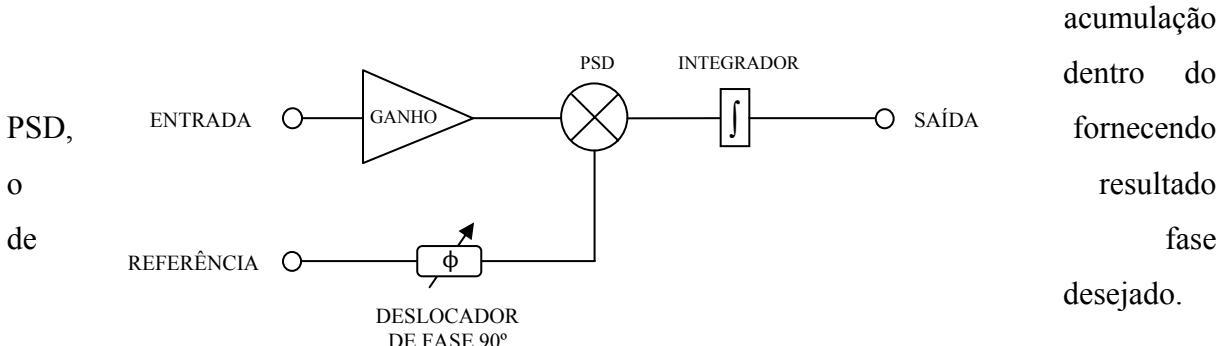

| Figura 1.2 | Diagrama completo de construção de um <i>Lock-In</i> digital comercial.                                                                                                                                                                                                                                                                              | 18 |

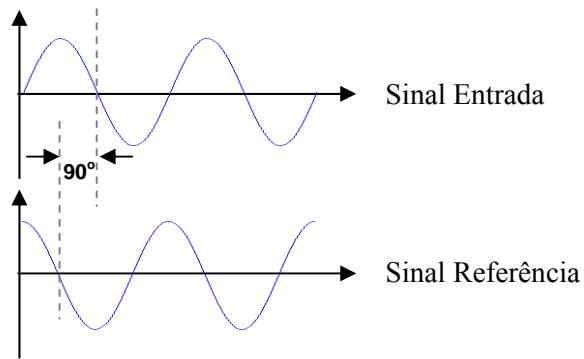

| Figura 1.3 | Sinal de entrada defasado de 90 graus do sinal de referência, resultando em $U_1 = 0$ e $U_2 = \frac{AB}{2}$ . O sinal de saída do PSD fica com freqüência igual ao dobro da do sinal de entrada, todavia com um valor médio nulo.                                                                                                                   | 21 |

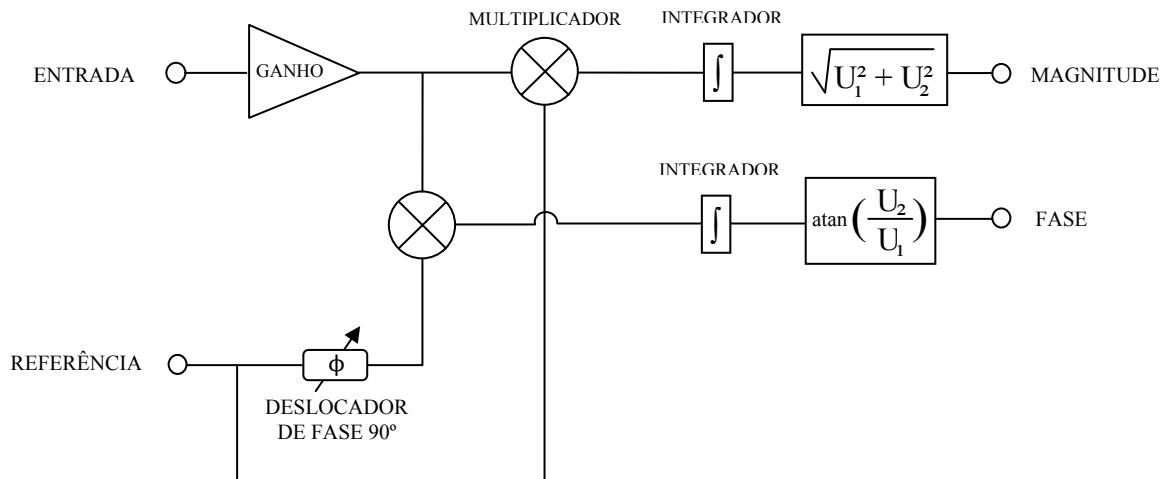

| Figura 1.4 | Esquemático completo de um Amplificador <i>Lock-In</i> . O sinal de referência é multiplicado duas vezes para geração das componentes $U_1$ e $U_2$ , cada uma destas multiplicações feitas com sinais defasados de 90 graus entre si. Após isso ocorre o cálculo de magnitude e fase, sendo as duas saídas do equipamento.                          | 22 |

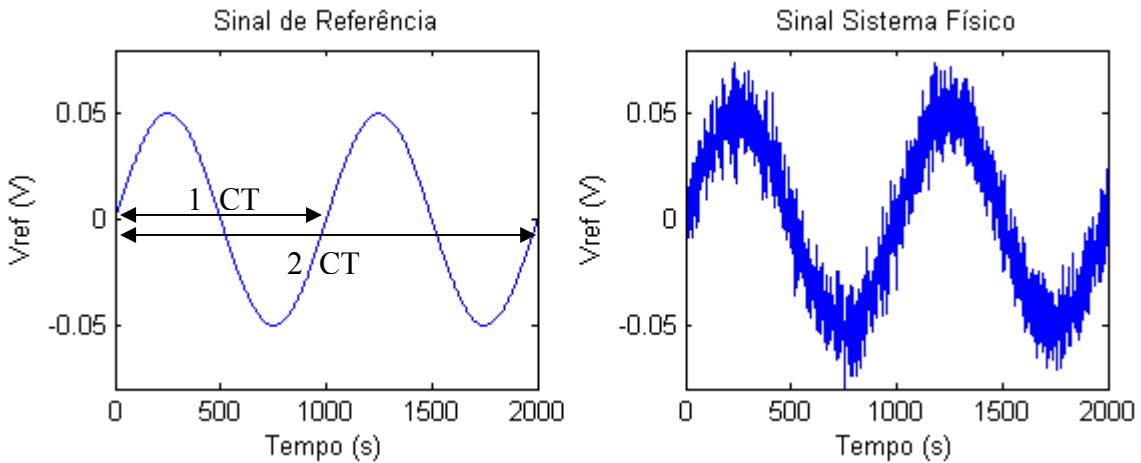

| Figura 2.1 | Demonstração do sinal de referência e do sinal do sistema físico.                                                                                                                                                                                                                                                                                    | 24 |

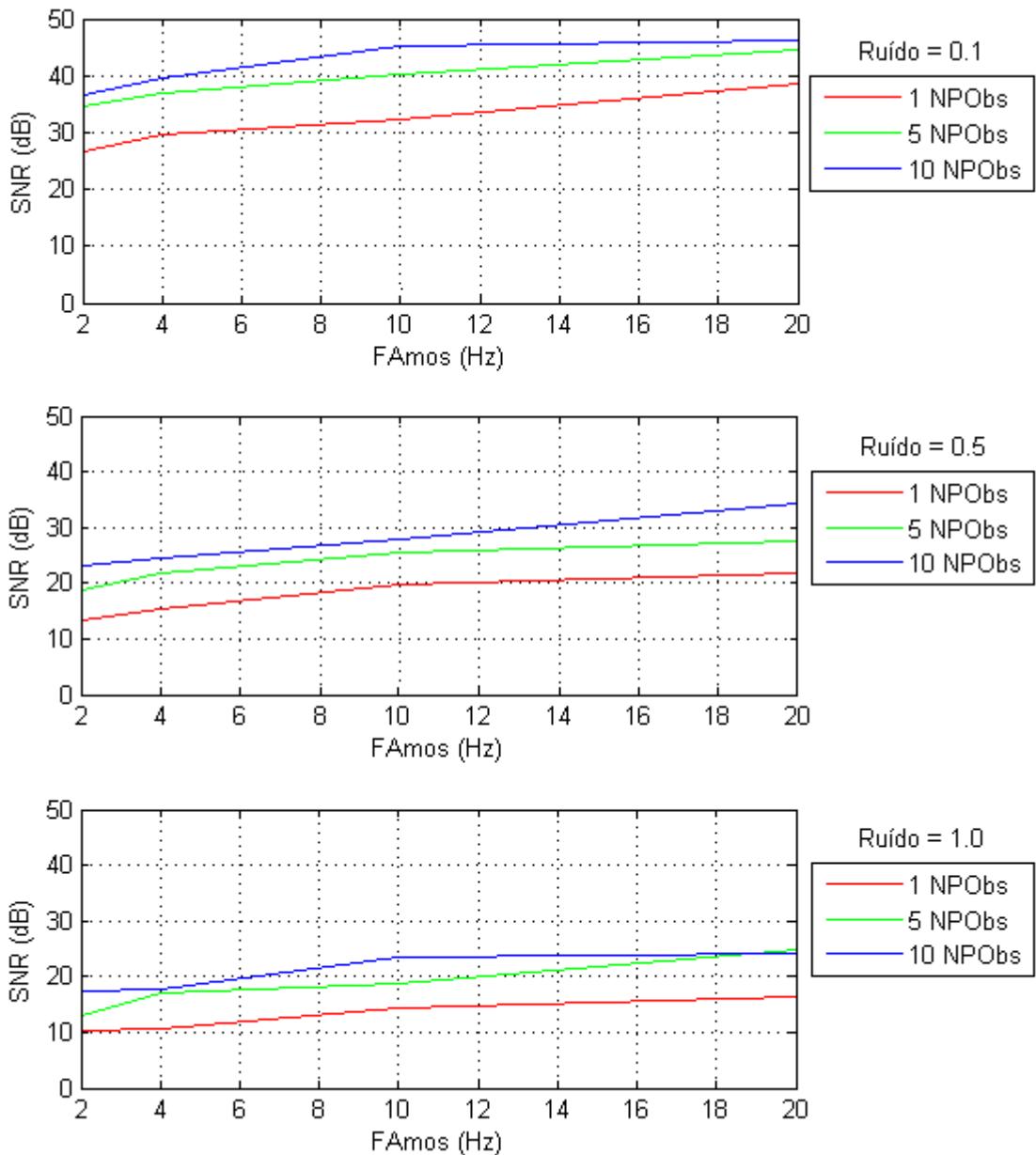

| Figura 2.2 | Gráfico comparativo da Relação Sinal-Ruído entre vários tipos de sinais de entrada, com ruídos variando entre $0.1 \text{ mV}_{\text{pp}}$ e $1.0 \text{ mV}_{\text{pp}}$ . Quanto maior a relação entre a freqüência de amostragem e o numero de períodos observados, melhor a SNR, ou seja, menos o ruído interfere no cálculo do <i>Lock-In</i> . | 27 |

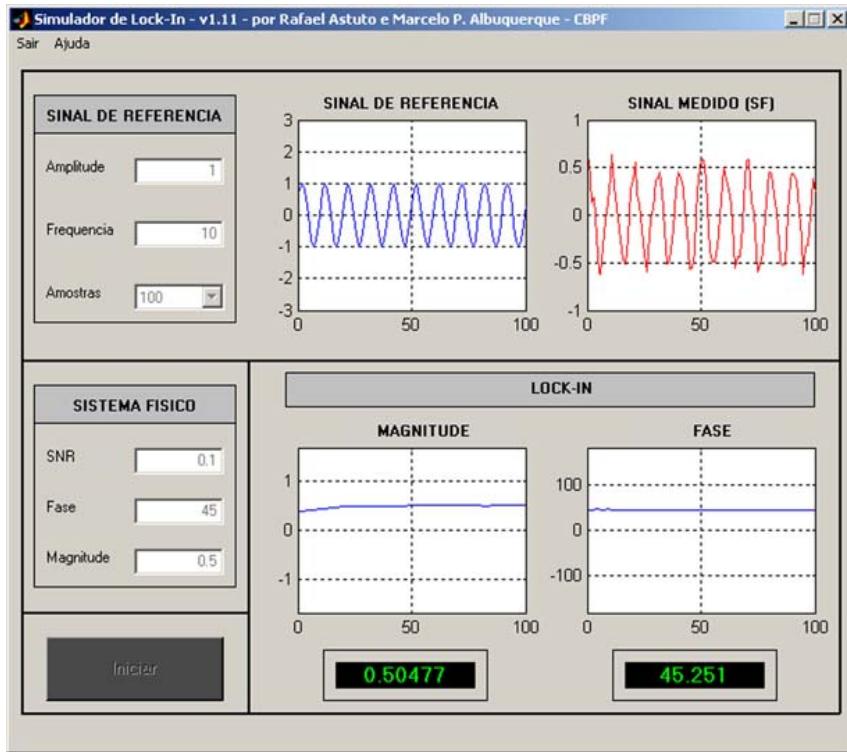

| Figura 2.3 | Imagen de tela do simulador de <i>Lock-In</i> . Como entrada o usuário pode definir o valor da amplitude, freqüência e o número de amostras do sinal de referência, além de poder configurar o nível de ruído através do valor da Relação Sinal-Ruído (SNR), da fase e da magnitude do sinal provindo do sistema físico.                             | 29 |

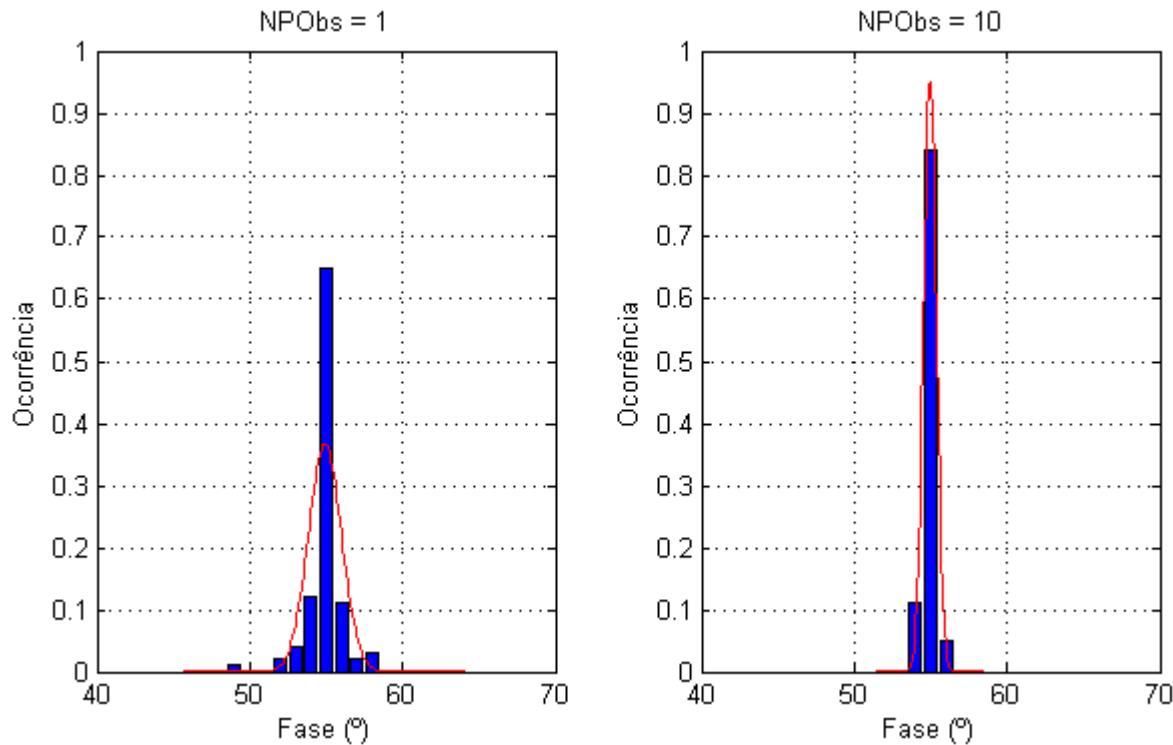

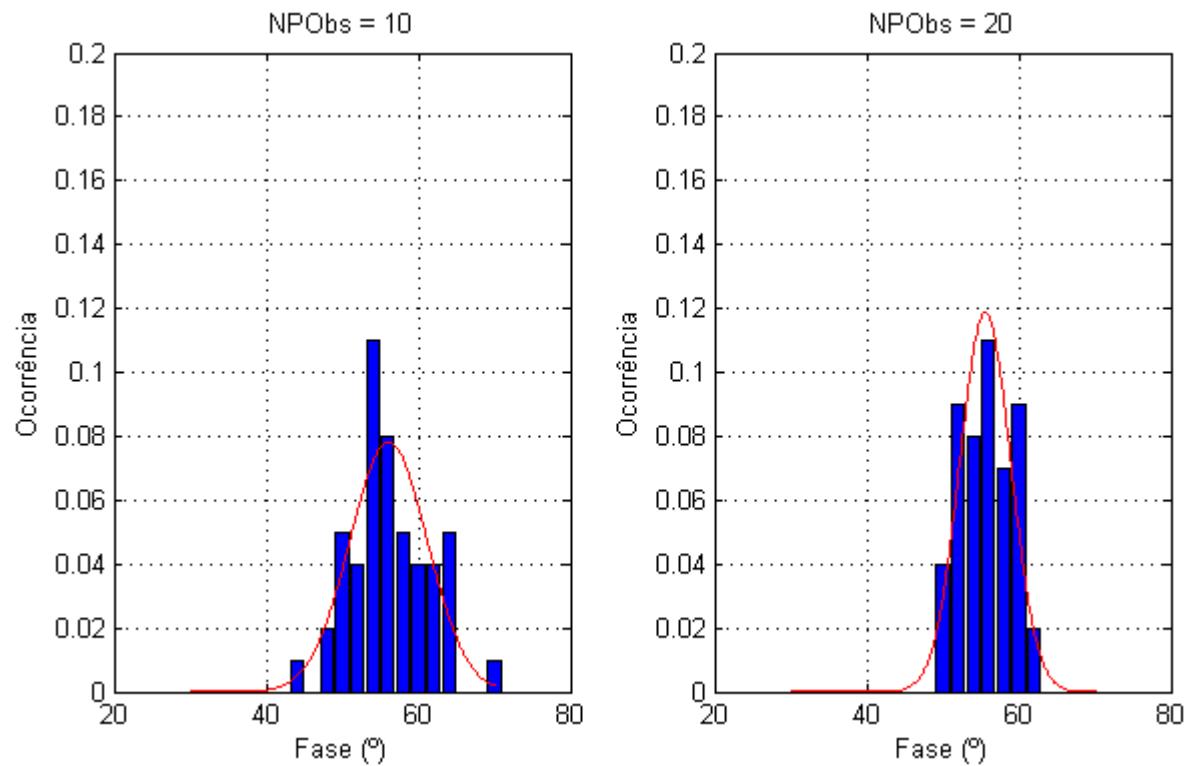

| Figura 2.4 | Distribuição dos resultados do cálculo de fase com nível de ruído de $0.1 \text{ mV}_{\text{pp}}$ , com 1 e 10 períodos observados para uma fase de $55^\circ$ .                                                                                                                                                                                     | 30 |

| Figura 2.5 | Distribuição dos resultados do cálculo de magnitude com nível de ruído de $0.1 \text{ mV}_{\text{pp}}$ , com 1 e 10 períodos observados para uma amplitude de $0.5V$ .                                                                                                                                                                               | 31 |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

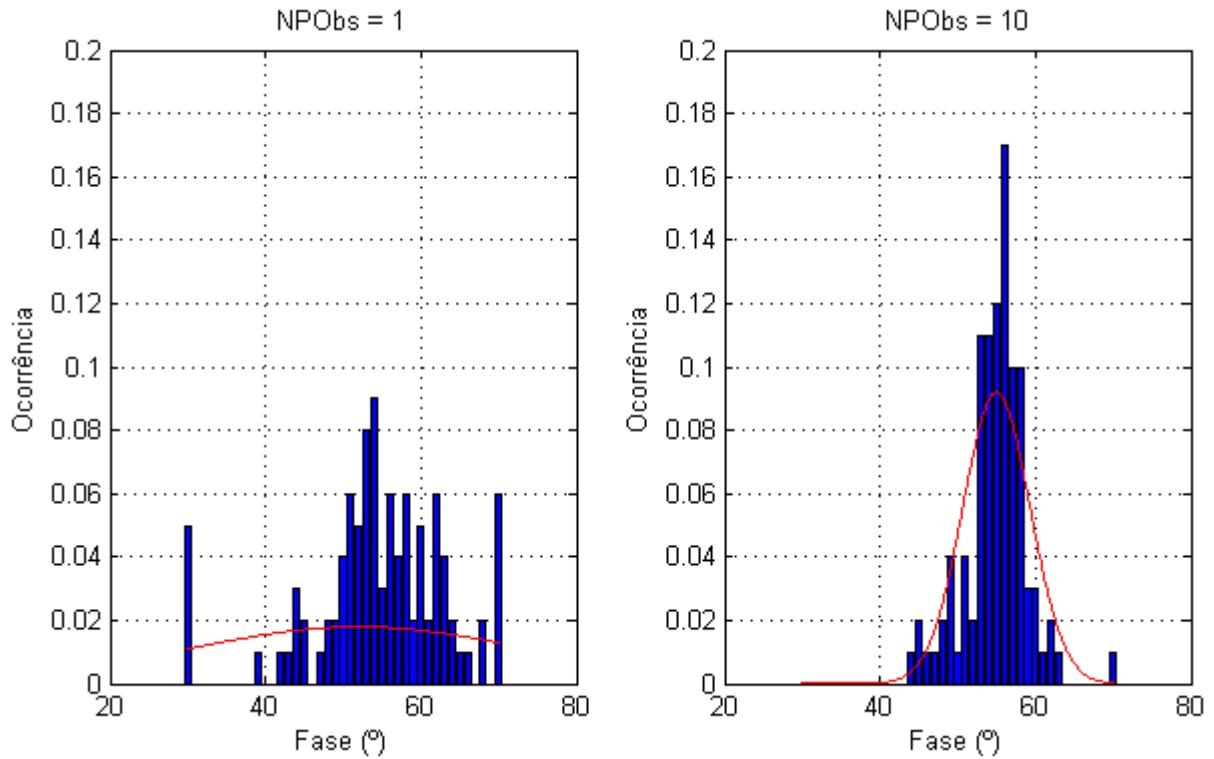

| Figura 2.6  | Distribuição dos resultados do cálculo de fase com nível de ruído 1 mV <sub>pp</sub> , com 1 e 10 períodos observados para fase de 55º. O alto nível de perturbação aliado com uma baixa amostragem do sinal, fez com que a resolução para 1 período de observação fosse muito ruim. Neste caso apenas 10% das amostras se aproximaram do valor desejado, o que não aconteceu quando aumentamos para 10 períodos, onde a gaussiana retrata a maior precisão no cálculo, com aproximadamente 30% das amostras próximas do centro. | 32 |

| Figura 2.7  | Distribuição dos resultados do cálculo de magnitude com nível de ruído 1 mV <sub>pp</sub> . O alto nível de perturbação não foi suficiente para desviar o padrão de resultado do algoritmo.                                                                                                                                                                                                                                                                                                                                      | 32 |

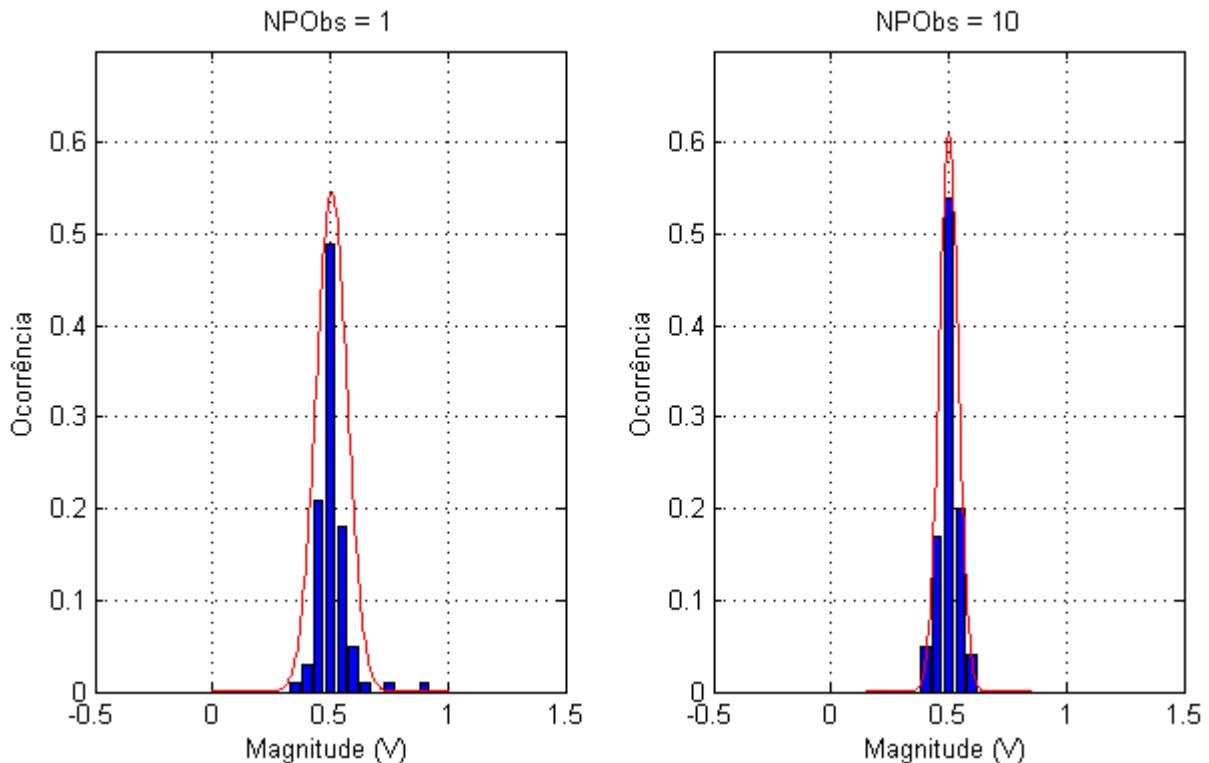

| Figura 2.8  | Histograma dos resultados de fase com nível de ruído 2 mV <sub>pp</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 33 |

| Figura 2.9  | Histograma dos resultados de magnitude com ruído de 2 mV <sub>pp</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 34 |

| Figura 2.10 | Desvio padrão das medições de magnitude e fase com simulação de ruído de 0.5 mV <sub>pp</sub> e F <sub>ref</sub> = 0.5 MHz. Os gráficos mostram que o comportamento exponencial varia inversamente com a raiz quadrada da constante de tempo de integração.                                                                                                                                                                                                                                                                      | 34 |

| Figura 3.1  | Esquemático da arquitetura do DSP EP2S60.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38 |

| Figura 3.2  | Foto do cabo de dados JTAG USB Blaster, utilizado para comunicação entre o computador e o DSP EP2S60. Este cabo ainda pode ser utilizado para outras famílias de DSP da Altera.                                                                                                                                                                                                                                                                                                                                                  | 40 |

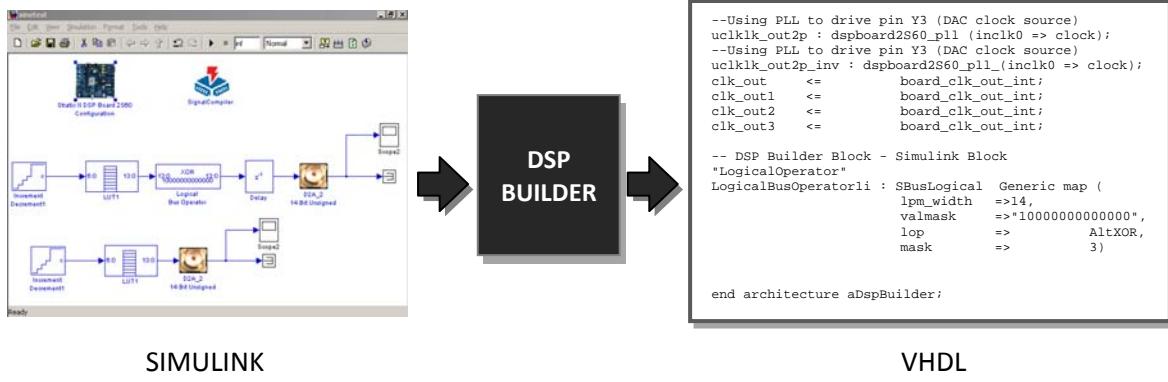

| Figura 3.3  | Esquema de conversão do DSP Builder. Ao elaborar um código no Simulink (.mdl) o programa converte os blocos em linguagem VHDL, que pode ser entendida pelo DSP, que realizará a rotina desejada.                                                                                                                                                                                                                                                                                                                                 | 42 |

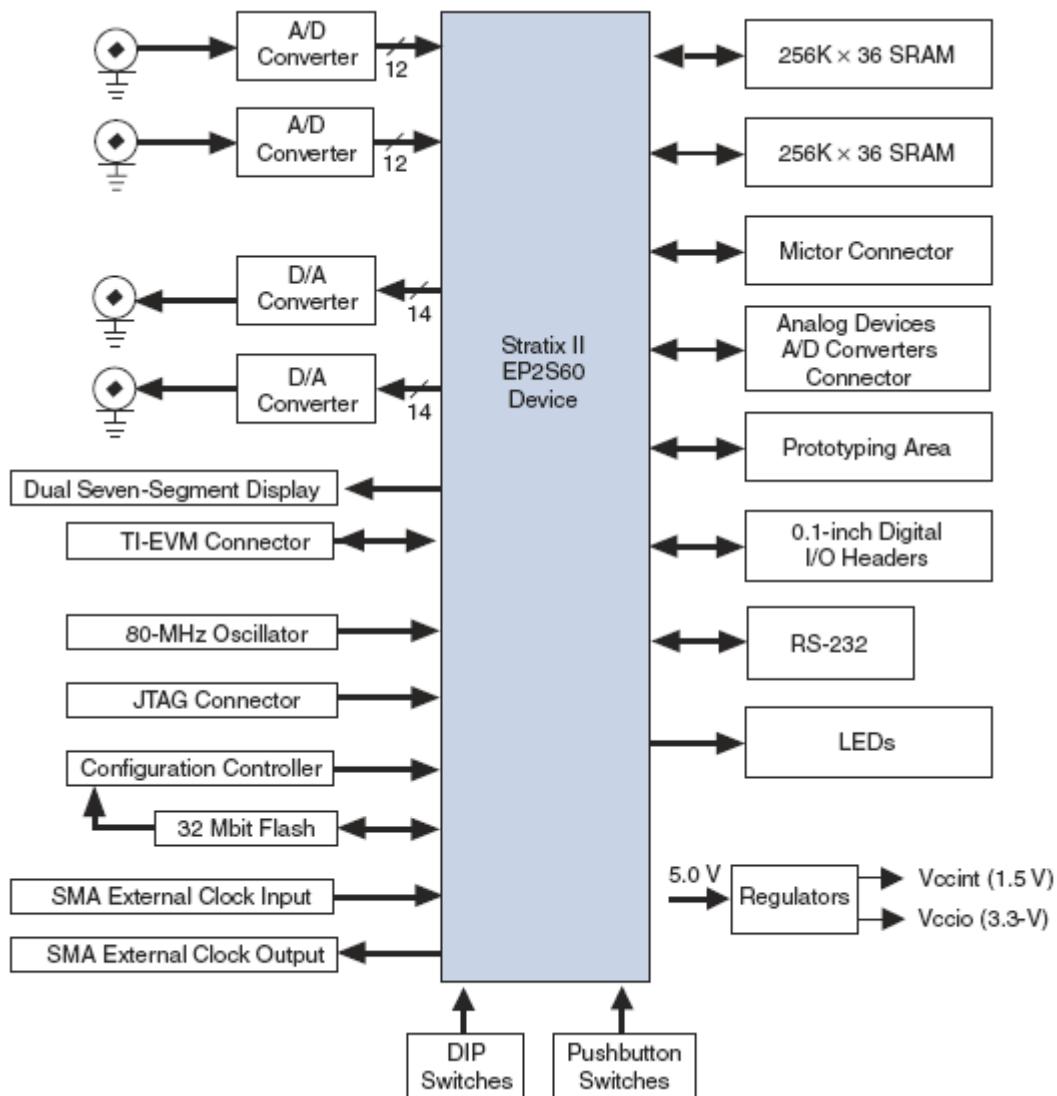

| Figura 3.4  | Diagrama de blocos funcional do kit DSP EP2S60.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43 |

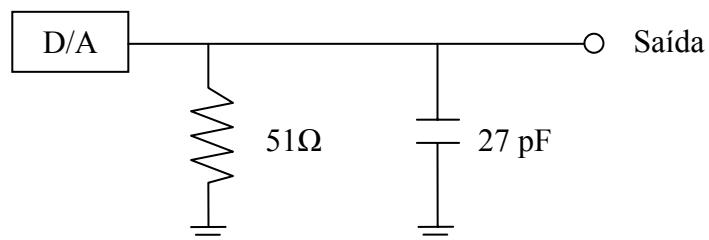

| Figura 3.5  | Filtro passa-baixa após conversor D/A do kit EP2S60.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44 |

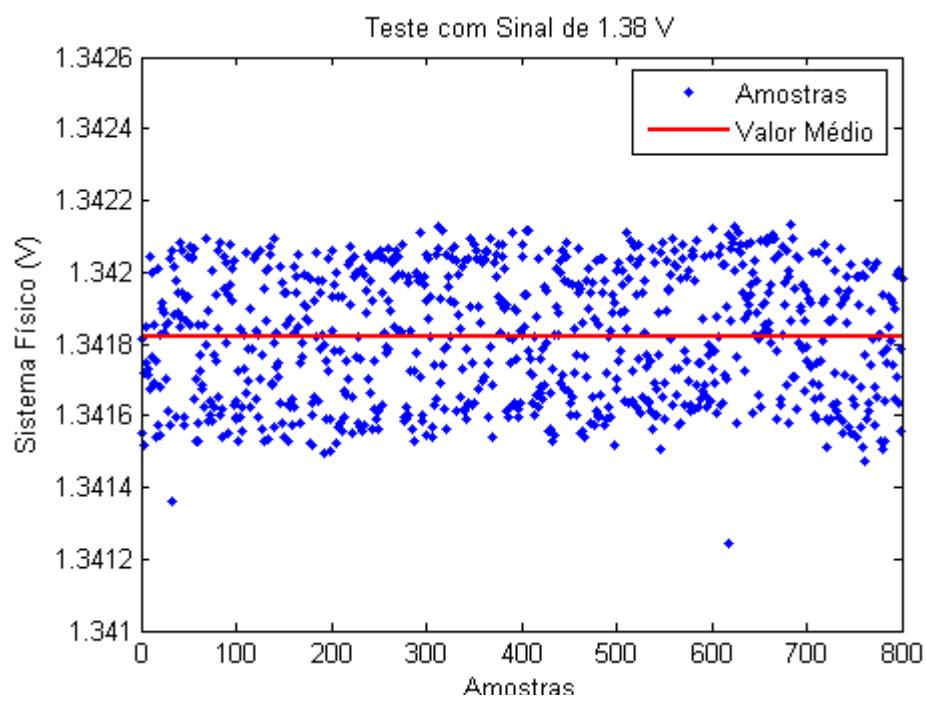

| Figura 4.1  | Distribuição das medições de 800 amostras. Em vermelho o valor médio obtido, em torno de 1,3418V, o que representa um erro de menos de 3% em relação ao sinal original.                                                                                                                                                                                                                                                                                                                                                          | 46 |

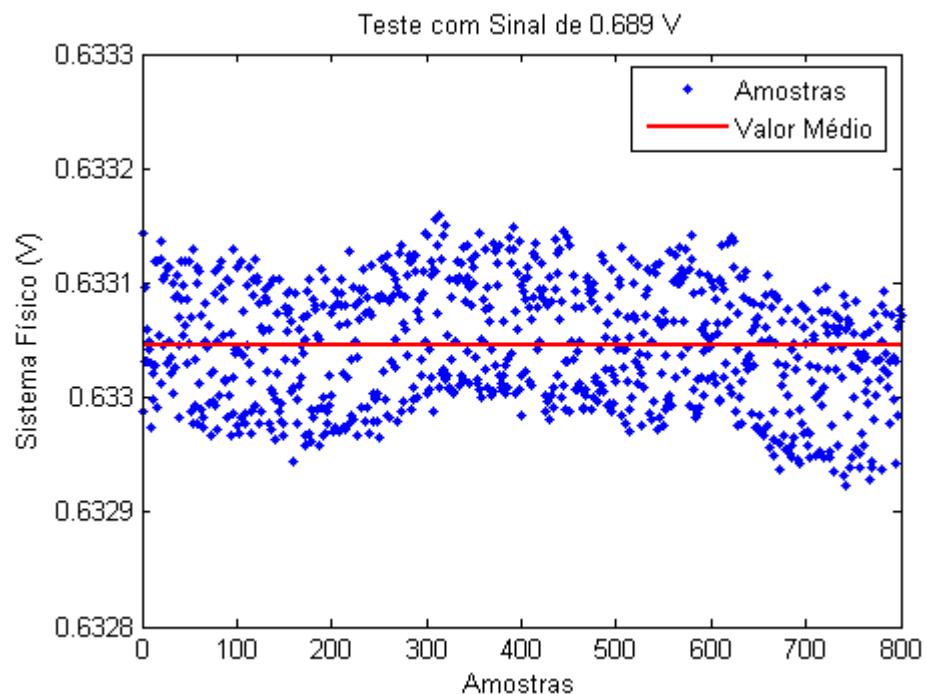

| Figura 4.2  | Distribuição das medições de 800 amostras com entrada de 0.689V com erro na faixa de 8%.                                                                                                                                                                                                                                                                                                                                                                                                                                         | 46 |

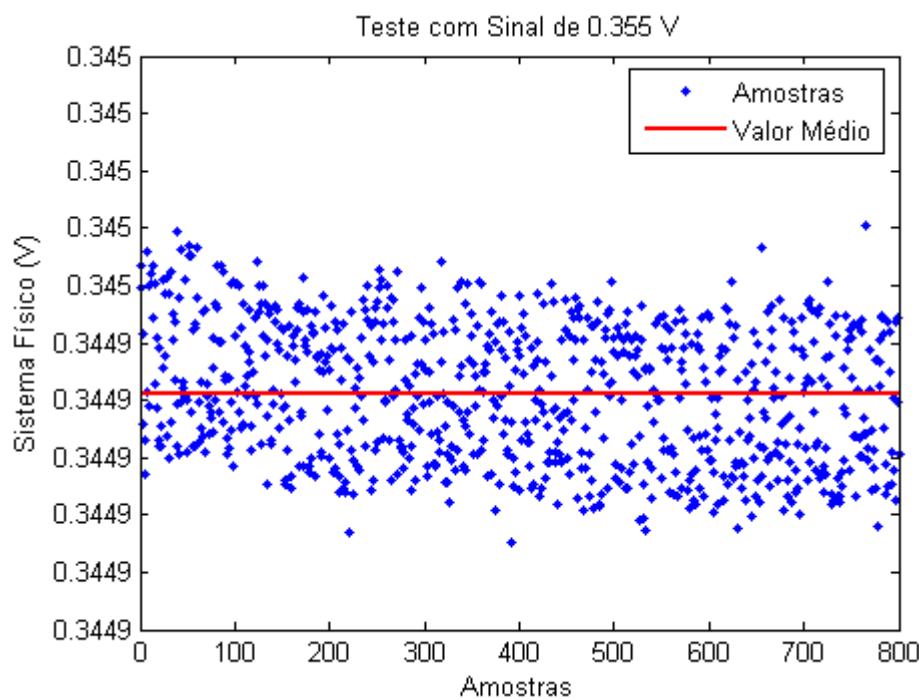

| Figura 4.3  | Distribuição de 800 amostras com entrada de 355 mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 47 |

|            |                                                                                                                                                                                                                                                                                                            |    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

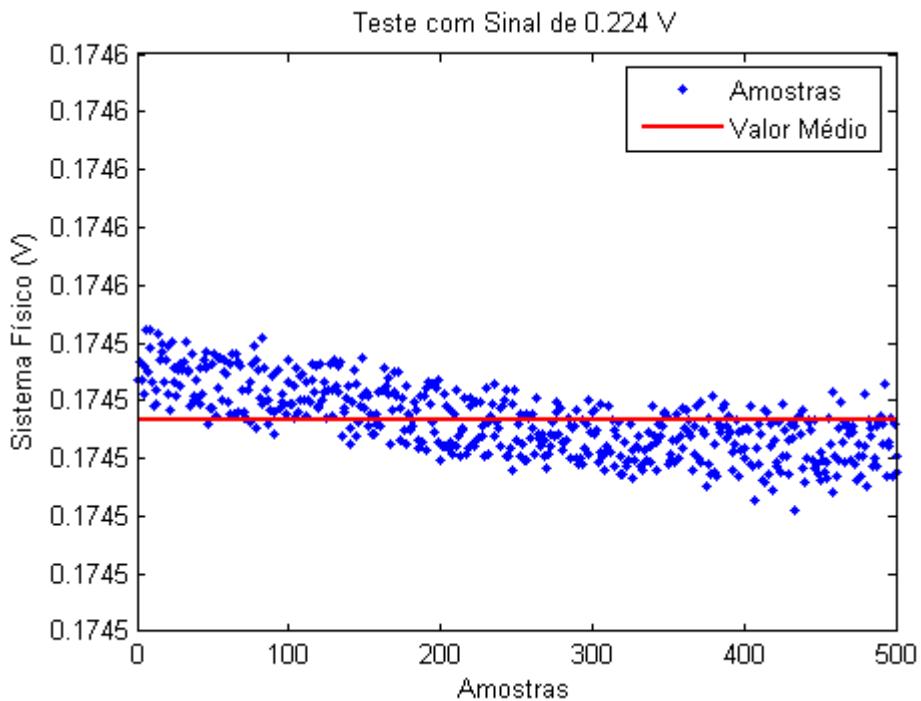

| Figura 4.4 | Distribuição de 500 amostras com entrada de 224 mV. A presença de ruídos ou a imprecisão da fonte para baixos sinais foram fatores que resultaram em um erro de 28%.                                                                                                                                       | 48 |

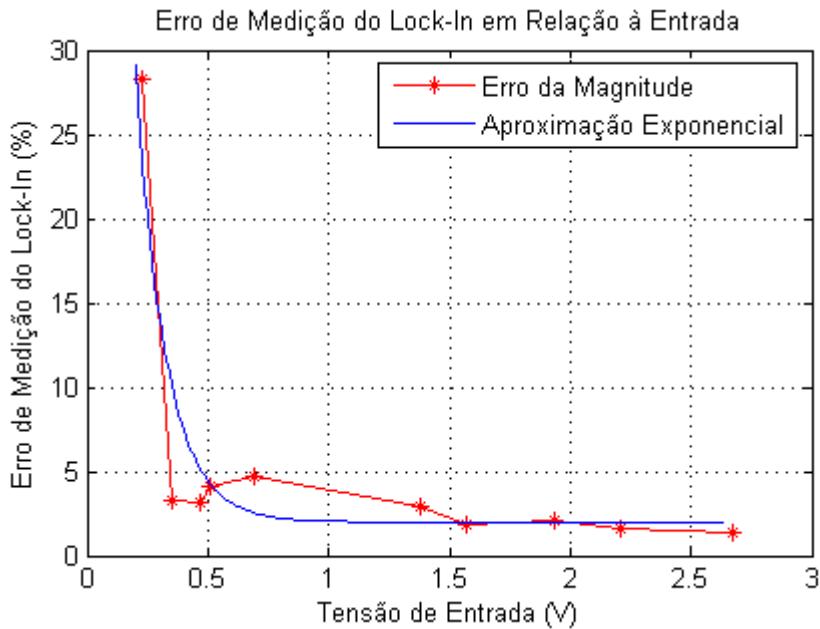

| Figura 4.5 | Em vermelho a relação entre a tensão de entrada do sistema físico experimental e o erro na medição do <i>Lock-In</i> . Em azul uma aproximação exponencial do erro.                                                                                                                                        | 49 |

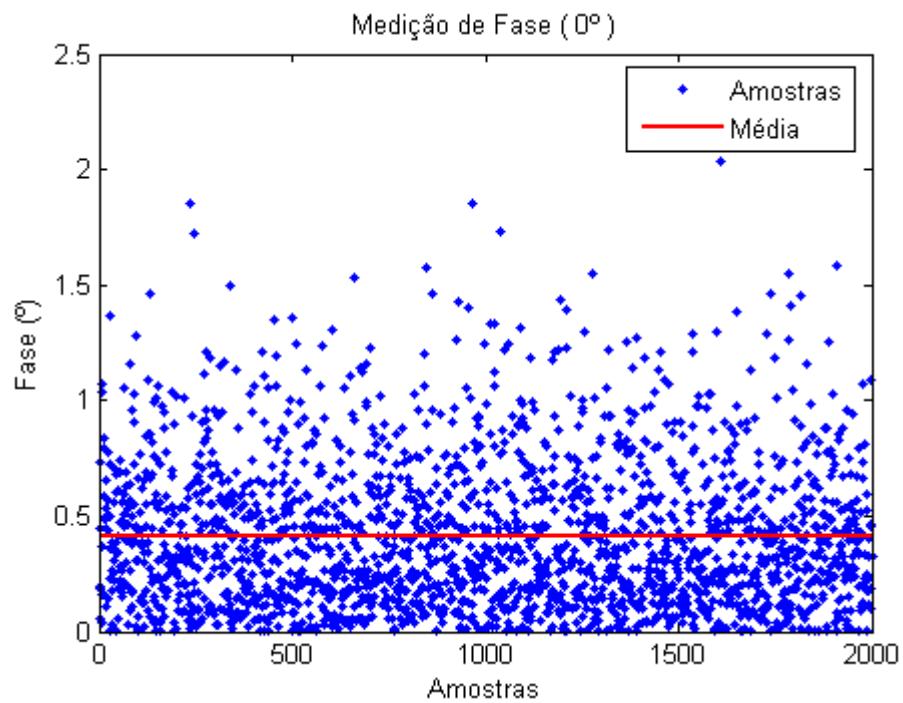

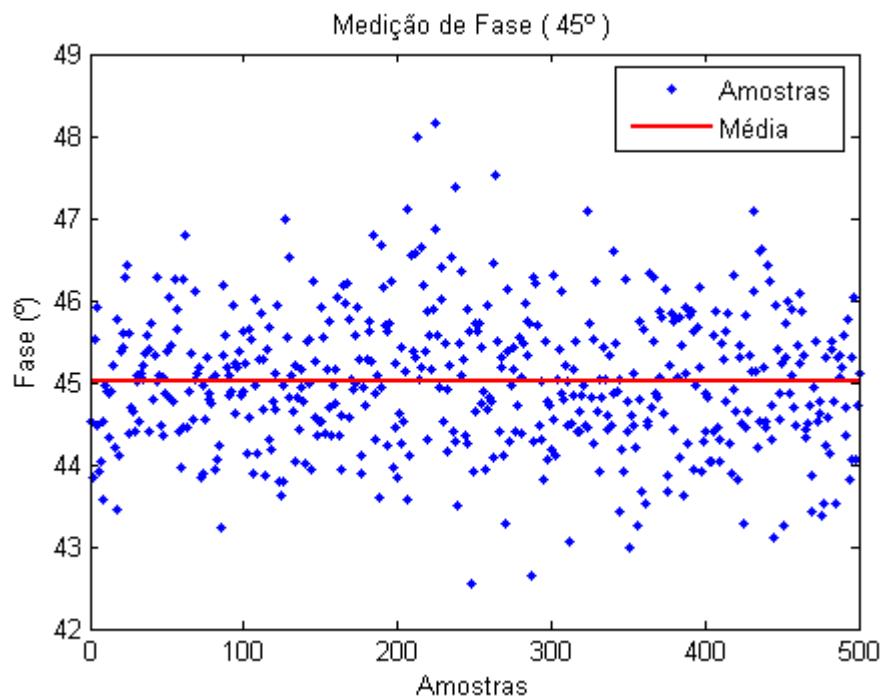

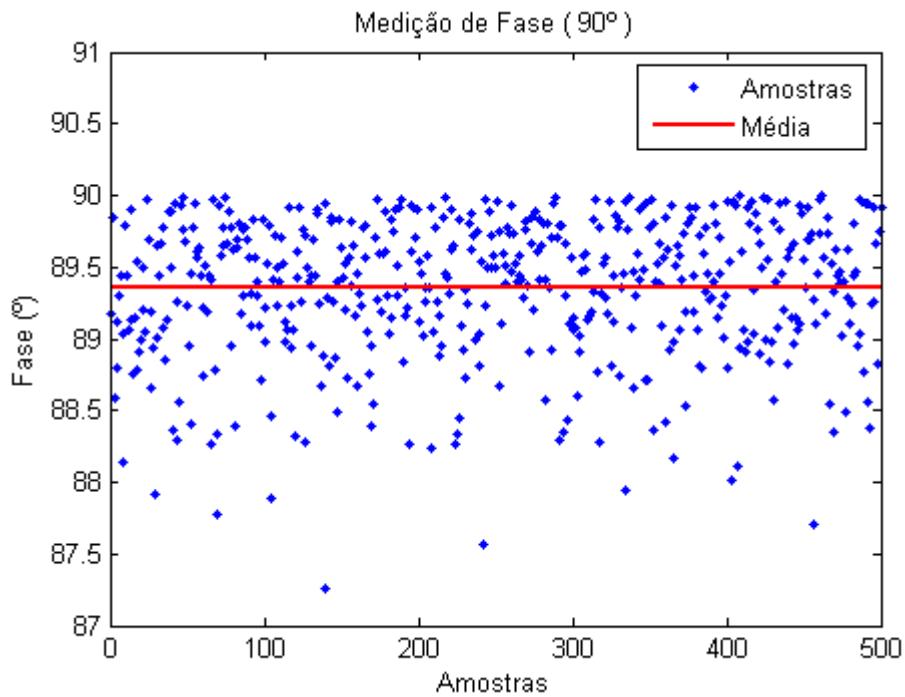

| Figura 4.6 | Dispersão das amostras calculadas pelo <i>Lock-In</i> para sinais em fase. O valor médio das amostras foi de 0,48º com um desvio padrão de 0,32 graus. A precisão foi em torno de 3% do valor inicial.                                                                                                     | 50 |

| Figura 4.7 | Dispersão das amostras para uma defasagem de 45 graus. A precisão deste cálculo foi de 4,49% com um desvio padrão de 0,83 graus.                                                                                                                                                                           | 50 |

| Figura 4.8 | Dispersão das amostras para uma defasagem de 90 graus. A precisão deste cálculo foi de 8,92% com um desvio padrão de 0,49 graus.                                                                                                                                                                           | 51 |

| Figura 5.1 | Esquema de montagem para estimação da freqüência de ressonância. Foram soldados aos terminais dos sensores cabos coaxiais, a fim de conectar o emissor a uma fonte AC e o receptor em um osciloscópio. A distância entre ambos pode ser considerada desprezível.                                           | 52 |

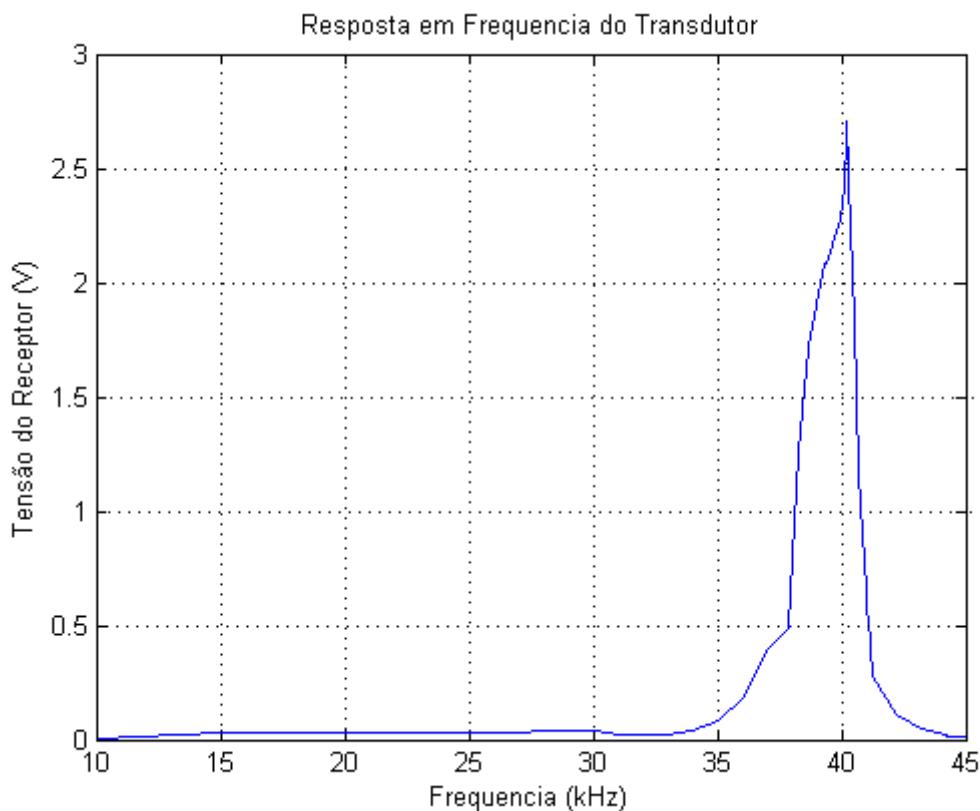

| Figura 5.2 | Gráfico de resposta em freqüência do transdutor. A leitura do receptor obteve a máxima tensão com um sinal de 40 kHz.                                                                                                                                                                                      | 53 |

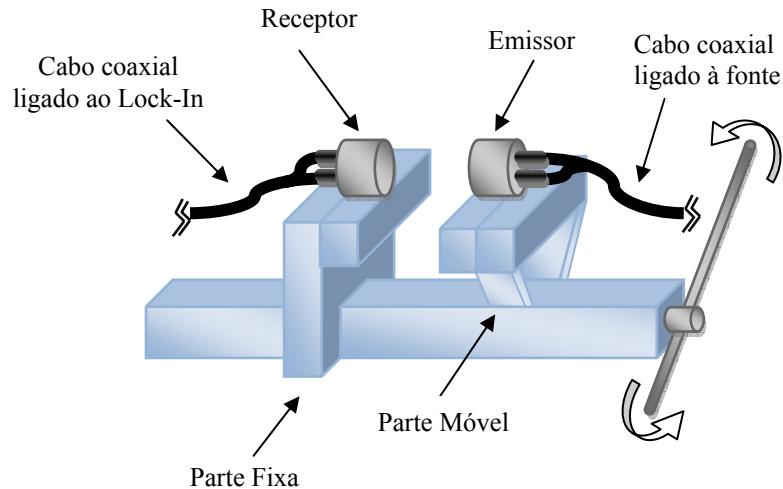

| Figura 5.3 | Esquema de montagem dos sensores. Utilizando-se um torno manual, colocou-se o receptor na parte fixa e o emissor, conectado à fonte, na parte móvel. Variando-se a distância através da manivela, consegue-se com o <i>Lock-In</i> , medir a diferença de fase entre os dois sinais.                       | 54 |

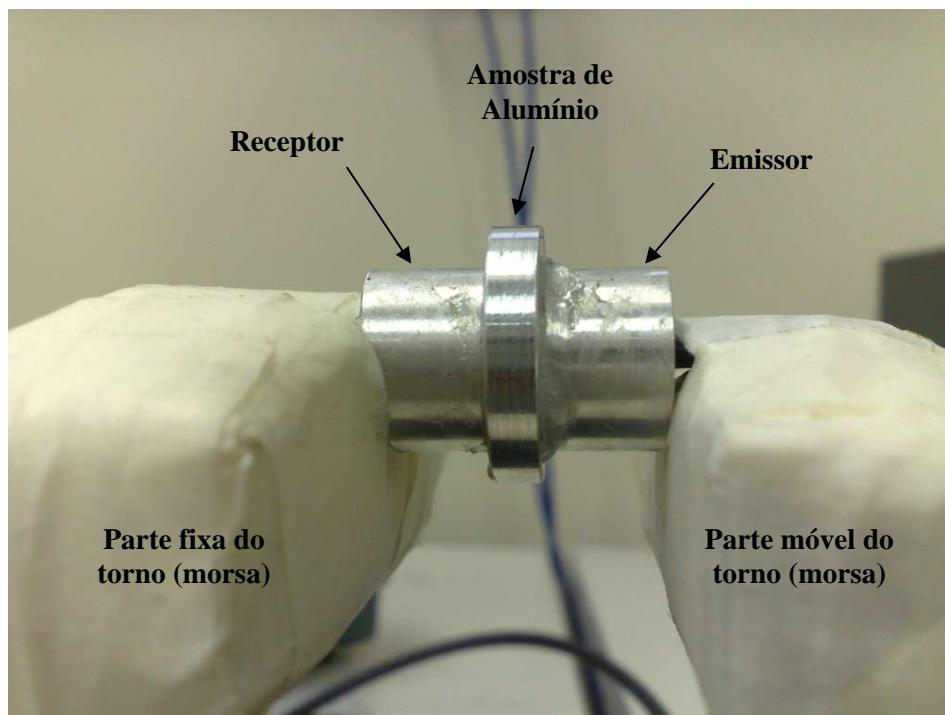

| Figura 5.4 | Foto do esquema de montagem dos sensores.                                                                                                                                                                                                                                                                  | 56 |

| Figura 5.5 | Foto dos sensores soldados na ponta de um cabo coaxial.                                                                                                                                                                                                                                                    | 56 |

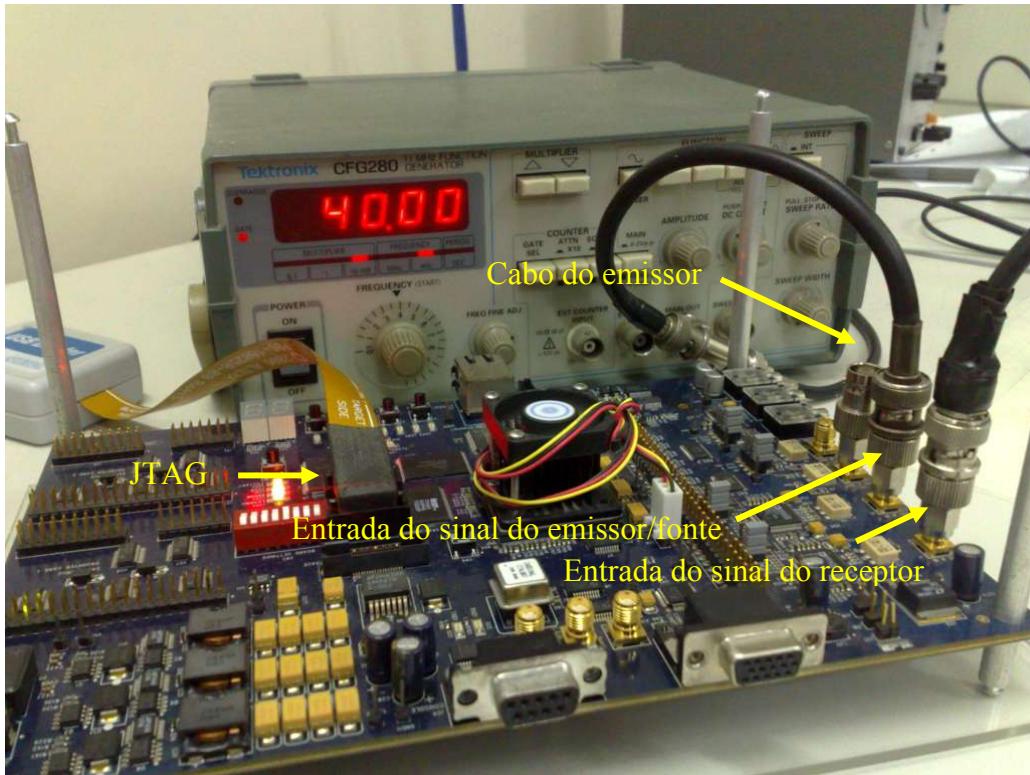

| Figura 5.6 | Esquema de montagem no DSP. Entrada dos sinais vindos dos sensores e conexão da placa através de interface JTAG com o computador.                                                                                                                                                                          | 57 |

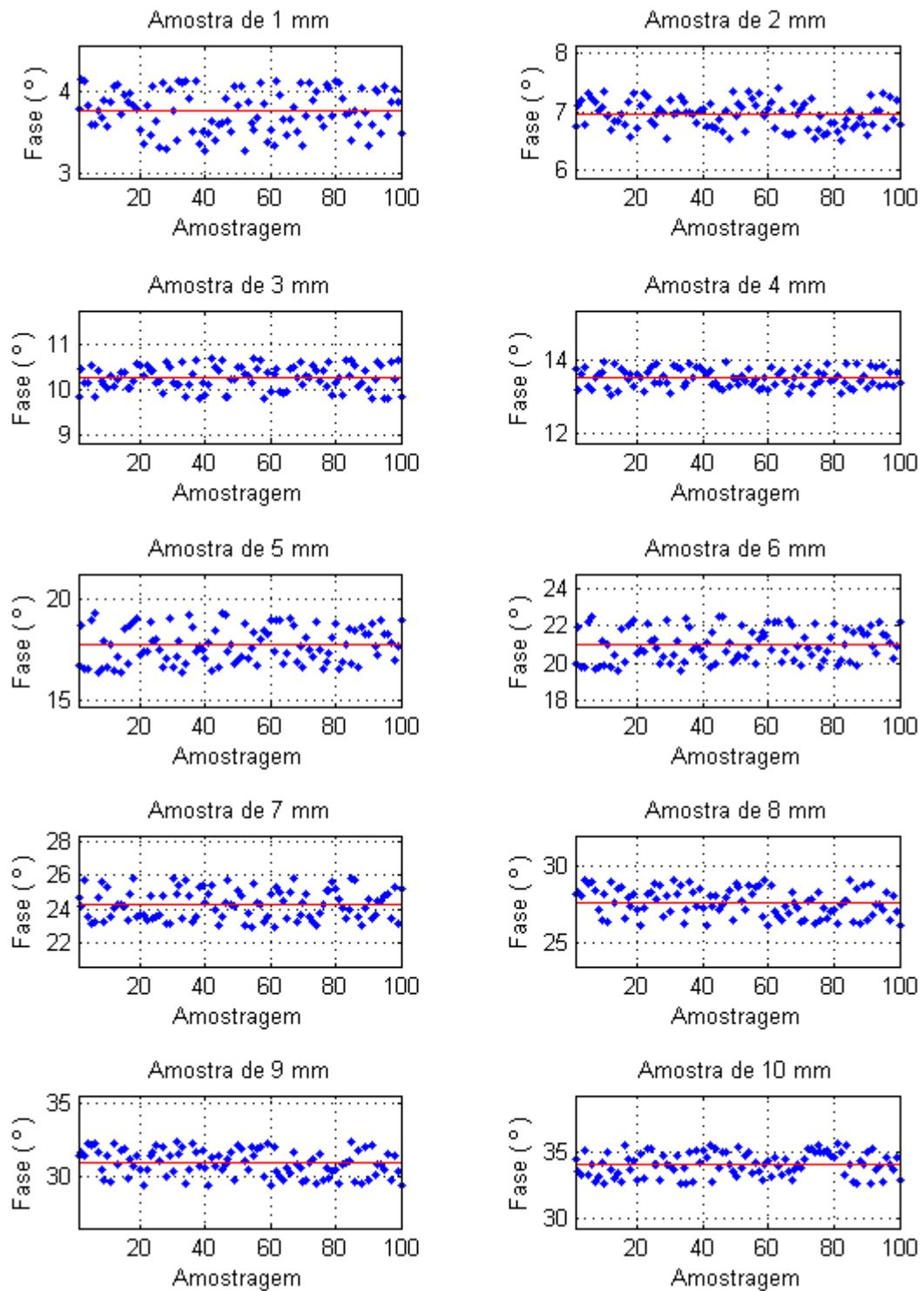

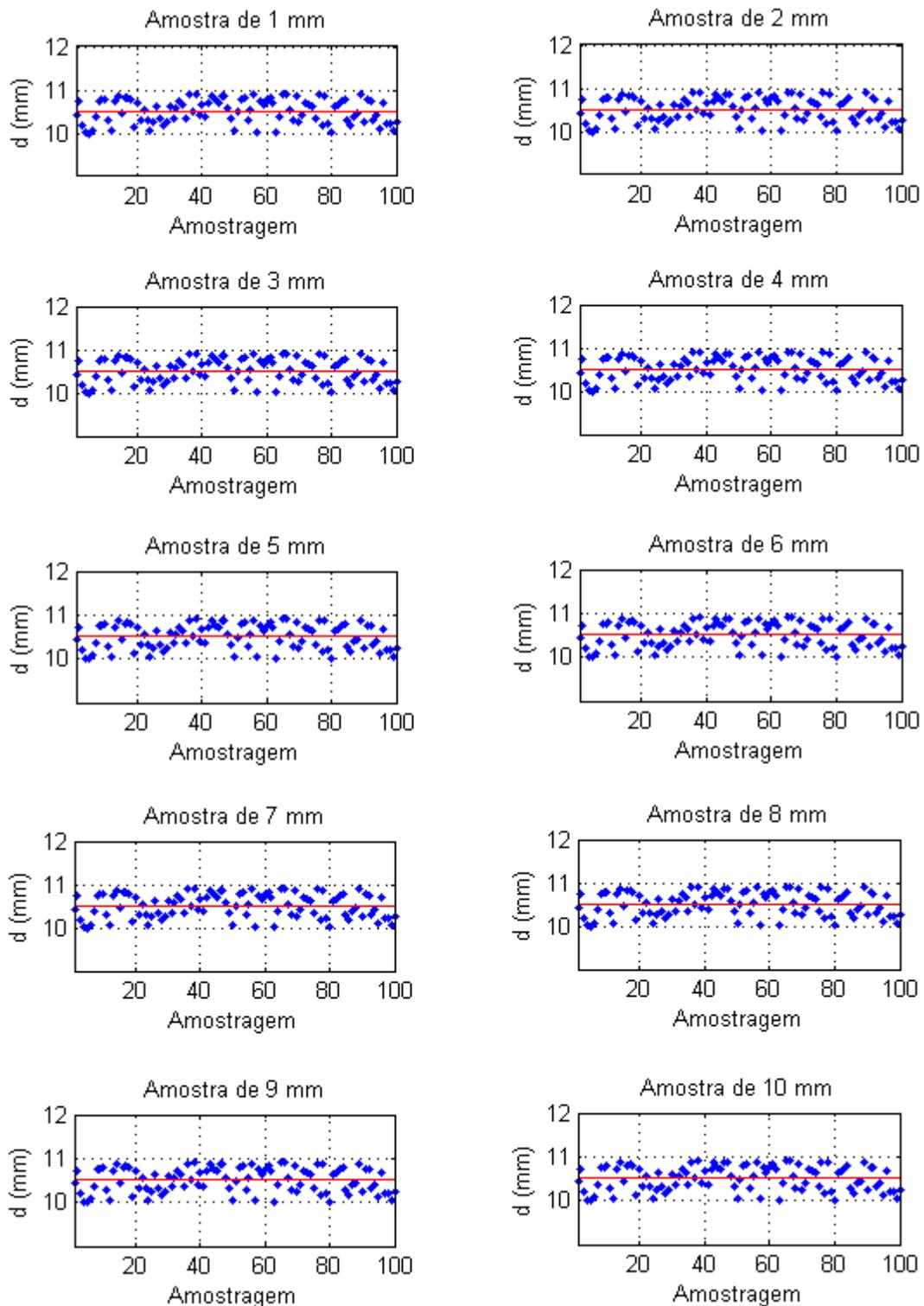

| Figura 5.7 | Gráfico com as medições das amostras de alumínio de 1 a 10mm. Foram realizadas 100 medições para cada amostra, sendo assim, ser possível calcular o desvio padrão e o erro de cada medição.                                                                                                                | 59 |

| Figura 5.8 | Gráfico com os valores da espessura (d) de cada amostra. Valores calculados a partir das medições de fase, onde $d = \beta \cdot 0,30694$ , sendo $\beta$ é o valor de fase calculado pelo <i>Lock-In</i> e 0,30694 é o valor correspondente a espessura de uma amostra causaria para ter defasagem de 1º. | 60 |

|             |                                                                                                                                                                                                                                                                                                                        |    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

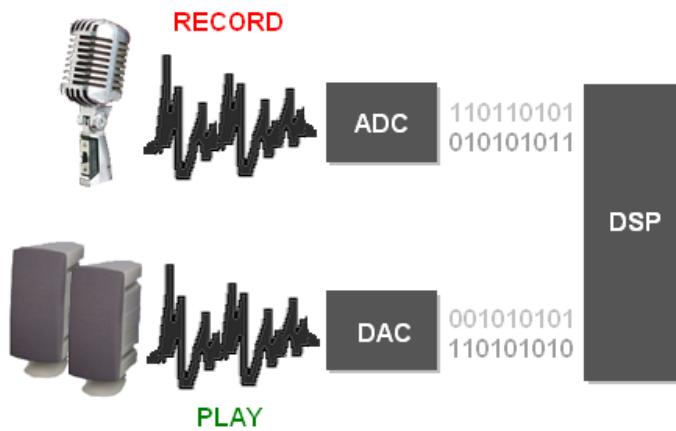

| Figura C.1  | Exemplo de como ocorre a conversão dos sinais tanto na forma analógico-digital quanto na forma digital-analógica, em um processo de gravação e reprodução de voz.                                                                                                                                                      | 68 |

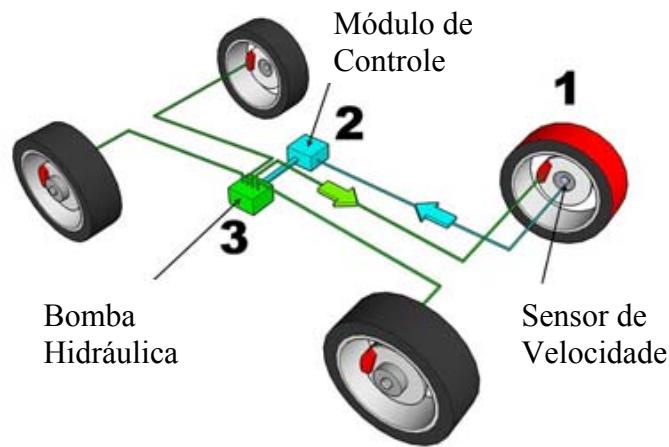

| Figura C.2  | Esquemático de representação do funcionamento de um ABS.                                                                                                                                                                                                                                                               | 70 |

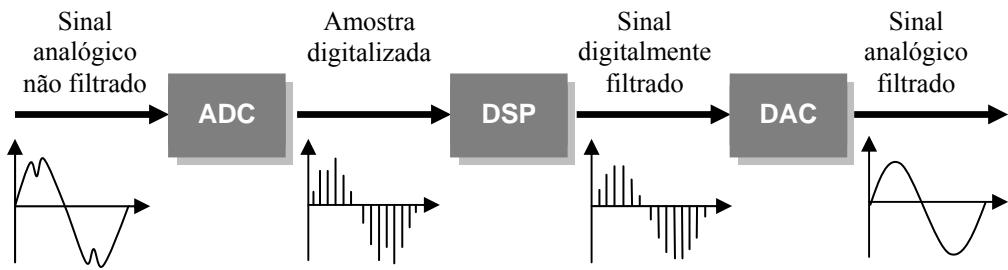

| Figura C.3  | O sinal original, contendo ruídos ou harmônicos, passa pelo filtro, que faz a seleção de qual parte será processada, enviando o sinal filtrado para o DSP.                                                                                                                                                             | 71 |

| Figura C.4  | Representação esquemática do caminho do sinal desde a entrada no conversor AD, passando pelo DSP, que realiza da manipulação deste, passando pelo conversor DA na saída.                                                                                                                                               | 72 |

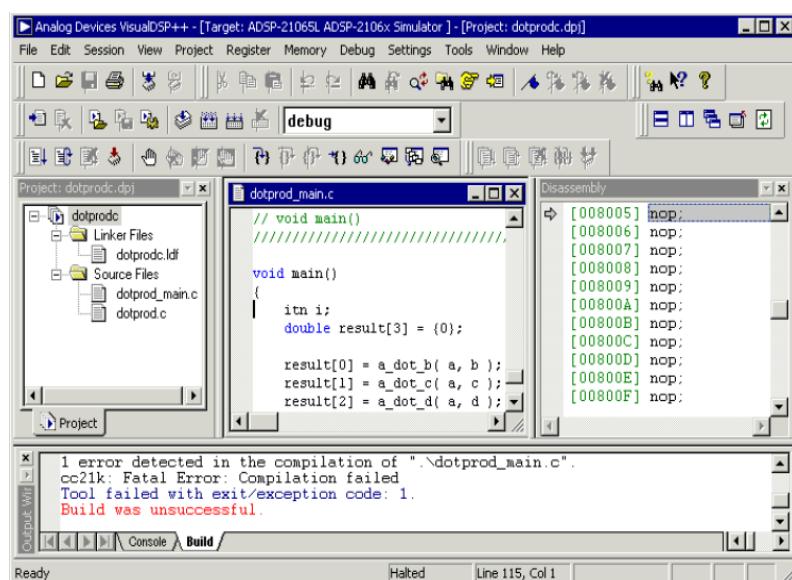

| Figura C.5  | IDE VisualDSP++ da <i>Analog Devices</i> . Aceita as principais linguagens de programação como <i>Assembly</i> , <i>C</i> e <i>C++</i> .                                                                                                                                                                               | 73 |

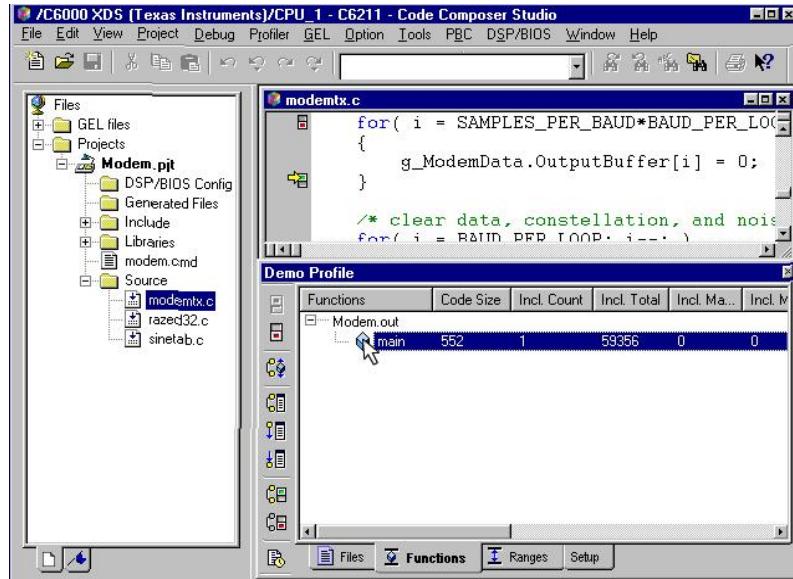

| Figura C.6  | IDE <i>Code Composer Studio</i> da <i>Texas Instruments</i> . Tem como principal base de programação <i>C</i> e <i>C++</i> , possuindo interface com o software matemático <i>Matlab</i> e <i>Matlab Simulink</i> , garantindo a esta IDE ótima versatilidade e facilidade na hora de montar projetos com DSP.         | 74 |

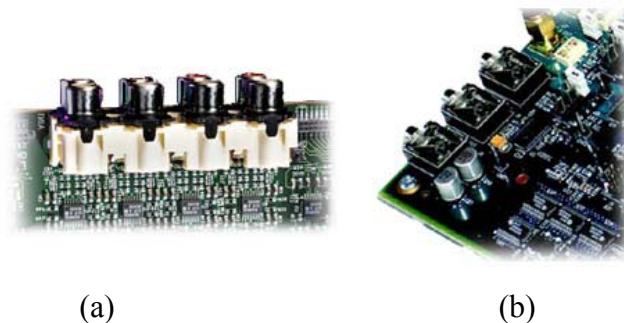

| Figura C.7  | (a) JTAG da <i>Texas Instruments</i> C2000™ Series XDS510LC. (b) JTAG da <i>Analog Devices</i> USB-Blaster™, compatível com as famílias de FPGA Stratix, Cyclone, MAX e FLEX 10K. Este modelo de JTAG foi utilizado no <i>kit</i> EP2S60 durante o projeto de construção do protótipo do Amplificador <i>Lock-In</i> . | 75 |

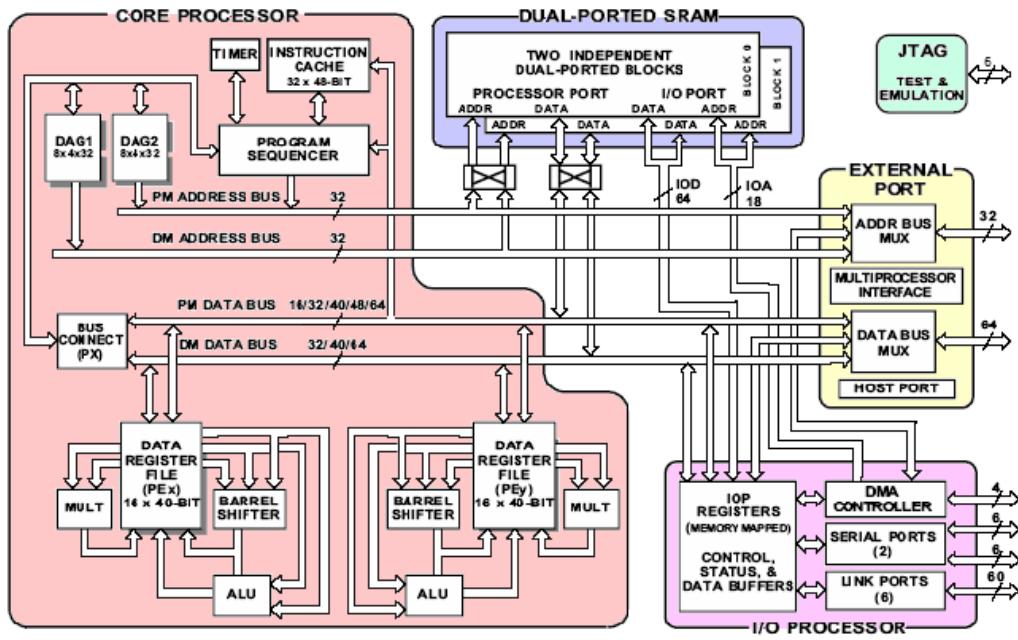

| Figura C.8  | Diagrama de blocos da estrutura básica do processador digital de sinais ADSP-21160M da <i>Analog Devices</i> . Em destaque os principais grupos do DSP.                                                                                                                                                                | 77 |

| Figura C.9  | (a) Conversor de vídeo do <i>kit</i> de DSP ADSP-BF533 da <i>Analog Devices</i> . (b) Conversor de áudio do DSP EP2S60 da <i>Altera Devices</i> .                                                                                                                                                                      | 77 |

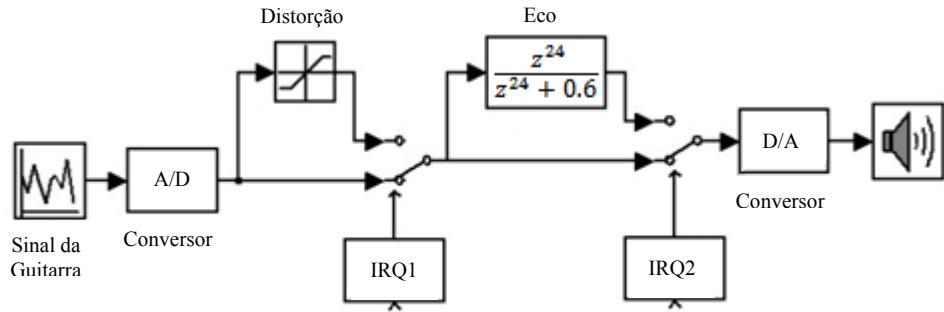

| Figura C.10 | Esquemático do sintetizador de guitarra implementado no DSP ADSP-21160M. O chaveamento ilustrado não ocorre fisicamente, mas sim digitalmente dentro do código. Cada vez que uma interrupção é ativada, esta chama uma função, executando-a, no caso ou de distorção ou de eco.                                        | 79 |

# Listas de Tabelas

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tabela 2.1 | Significado das variáveis de entrada do programa.                                                                                                                                                                                                                                                                                                                                                                                        | 23 |

| Tabela 2.2 | Valores de entrada para simulação do amplificador <i>Lock-In</i> , a fim de validar a teoria de redução de ruídos. Inicialmente utilizou-se ruído com 0.1 mV <sub>pp</sub> finalizando a experiência com ruído de 1 mV <sub>pp</sub> .                                                                                                                                                                                                   | 24 |

| Tabela 2.3 | Resultados obtidos com nível de ruído de 0.1 mV <sub>pp</sub> .                                                                                                                                                                                                                                                                                                                                                                          | 25 |

| Tabela 2.4 | Resultados obtidos com nível de ruído de 0.5 mV <sub>pp</sub> .                                                                                                                                                                                                                                                                                                                                                                          | 26 |

| Tabela 2.5 | Resultados obtidos com nível de ruído de 1 mV <sub>pp</sub> .                                                                                                                                                                                                                                                                                                                                                                            | 26 |

| Tabela 3.1 | Descrição geral dos componentes do kit Stratix II EP2S60 DSP.                                                                                                                                                                                                                                                                                                                                                                            | 39 |

| Tabela 3.2 | Descrição geral das interfaces de debug e de expansão do kit Altera Stratix II EP2S60 DSP.                                                                                                                                                                                                                                                                                                                                               | 40 |

| Tabela 4.1 | Resultados obtidos de medições de magnitude pelo <i>Lock-In</i> .                                                                                                                                                                                                                                                                                                                                                                        | 48 |

| Tabela 4.2 | Resultado dos três testes feitos para medição de fase.                                                                                                                                                                                                                                                                                                                                                                                   | 51 |

| Tabela 5.1 | Com o valor inicial de $1^\circ = 0,30694$ mm, tabelou-se os valores teóricos de diferença de fase de todas as amostras, a fim de saber com antecedência se o valor medido pelo <i>Lock-In</i> está ou não de acordo com valores pré estabelecidos de precisão e margens de erro.                                                                                                                                                        | 55 |

| Tabela 5.2 | Tabela com os resultados das medições com as amostras de alumínio. Os resultados mostram uma boa precisão, dadas às condições do ambiente de medição, sujeito a grande quantidade de ruídos. O erro percentual tanto de fase quanto de espessura ficou dentro de uma faixa média de 9 a 11%. A indicação de valores médios da tabela dá-se à média das 100 medições por amostra feitas, a fim de realizar-se o cálculo de desvio padrão. | 58 |

| Tabela C.1 | Rotina de cálculo de convolução implementada no DSP ADSP-21160M através da IDE VisualDSP++ da <i>Analog Devices</i> . Todo o código foi feito em linguagem C.                                                                                                                                                                                                                                                                            | 78 |

| Tabela C.2 | Código do sintetizador de guitarra implementado no DSP ADSP-21160M. A rotina foi desenvolvida e compilada usando-se a IDE VisualDSP++ da <i>Analog Devices</i> .                                                                                                                                                                                                                                                                         | 80 |

# Introdução

## Tema

Este trabalho trata sobre o estudo de Processadores Digitais de Sinais (DSP), visando aprofundar-se em suas aplicações, a fim de realizar experiências científicas e construção de instrumentos eletrônicos de medição, com o intuito de por em prática teorias matemáticas e físicas previamente estudadas.

Para realização deste trabalho foi de suma importância a utilização de conhecimentos teóricos provindos das áreas de Instrumentação, Eletrônica, Física e Matemática, os quais contribuíram para elaboração dos algoritmos utilizados no trabalho.

A primeira etapa do trabalho se deu na escolha do DSP mais adequado para realização do projeto. O protótipo elaborado foi feito baseado na plataforma do *kit* de desenvolvimento EP2S60 da *Altera Devices*, descrito com mais detalhes no Capítulo 2.

No segundo estágio foi elaborado um algoritmo para simular o funcionamento de um *Lock-In*. O intuito deste algoritmo foi de mostrar como o *Lock-In* consegue observar sinais imersos em ruídos e extrair com precisão sua fase e magnitude. Com o intuito de ilustrar seu funcionamento também foram elaborados simuladores gráficos em MATLAB.

No terceiro estágio do trabalho foi implementado no DSP EP2S60 um protótipo de *Lock-In* baseado nos algoritmos anteriormente desenvolvidos. Este protótipo será detalhadamente descrito no capítulo 2.

## Justificativa

Tem sido crescente a demanda por equipamentos portáteis (como GPS, celulares e instrumentos de medição), de fácil manuseio e que tenham uma interface simples com o usuário. A utilização de DSP procura unir todos esses preceitos de forma a se tornar uma ferramenta de trabalho das mais completas atualmente.

Com suas mais diversas possibilidades de uso, nas mais abrangentes áreas, os processadores digitais de sinais são muito versáteis, podendo se enquadrar em quaisquer tipos de projetos. Vários ramos da indústria civil e militar utilizam DSP em seus equipamentos. Realizar projetos de pesquisa e aprendizado utilizando estes processadores é fundamental para se desenvolver tecnologia, o que torna o DSP uma ferramenta estratégica nos laboratórios das universidades de todo o mundo.

## Objetivos

Este trabalho tem por objetivo a construção de um protótipo de um Amplificador *Lock-in* (descrito com detalhes no Capítulo 1), e sua validação através de experiências físicas. A elaboração do projeto é baseada na teoria de sinais, que define com precisão todo o processo de transformação e detecção do sinal realizado por um *Lock-in*. Essa detecção consiste na técnica de medida de um sinal de baixa amplitude corrompido por ruído (aleatório e periódico), baseado na detecção síncrona, que corresponde ao processo de demodulação síncrona (Figura 1), explicado no Capítulo 1.

Figura 1: Princípio da detecção síncrona (ou demodulação) para medir o atraso de um sinal de referência em relação a um sinal de um sistema físico.

A construção de um *Lock-in* pode ser feita utilizando-se princípios e técnicas da eletrônica clássica (análogica ou digital) em conjunto com DSPs e softwares específicos, que irão controlar e manipular os conversores analógico-digitais (ADC) e digital-analógicos (DAC).

Neste trabalho, foi desenvolvimento um protótipo de um Amplificador *Lock-in* baseado em *kits* DSP de empresas comerciais. O processo abrange desde a pesquisa pelo equipamento adequado, até o desenvolvimento de algoritmos de testes e simuladores.

## Metodologia

O início da elaboração do protótipo do Amplificador *Lock-in* se deu desenvolvendo a teoria matemática e física necessária à aplicação. Baseado nisso, foram criados diversos algoritmos, implementados no *software* matemático MATLAB, a fim de realizar sua validação.

A comprovação teórica foi importante para a criação de simuladores, que proporcionaram uma interface gráfica para melhor visualização e entendimento do processo físico envolvido. Com isto, foi possível desenvolver um protótipo, com o intuito de validar os resultados obtidos nas simulações.

## Descrição

O Capítulo 1 traz à luz as teorias que sustentam todo funcionamento de um *Lock-In*, bem como seus fundamentos matemáticos e físicos. São apresentadas diferenças entre um *Lock-In* digital e um analógico, focando-se em retratar as características do detector sensível de fase, o PSD.

No segundo capítulo deste trabalho são mostradas as etapas de elaboração de um simulador *Lock-In* feito em Matlab, inclusive com interface gráfica. Neste capítulo o usuário consegue, manipulando o simulador, analisar de que forma um ruído interfere na detecção de fase e magnitude, bem como saber qual a quantidade mínima de pontos por período seriam necessários obter do sinal de entrada, a fim de se conseguir uma boa precisão nos cálculos, para uma eventual experiência.

O capítulo 3 apresenta a implementação de um protótipo de *Lock-In* feito em interface DSP através do kit de desenvolvimento Altera Stratix® II EP2S60. Todo processo foi estruturado através da comunicação da placa com o software Matlab, que trabalhando em conjunto com sua IDE Quartus II, possibilitou a construção do protótipo.

No quarto capítulo são apresentados resultados de medições reais feitas com o DSP programado com o algoritmo do *Lock-In*. Os testes foram feitos de forma a comprovar a robustez do código, que trabalhando com sinais de alta freqüência forneceu medidas muito precisas, com baixo desvio padrão.

O quinto capítulo apresenta uma aplicação prática para o *Lock-In* implementado no kit da Altera. Através da utilização de sensores de ultra-som de 40 kHz de freqüência de ressonância, montou-se um esquema para medição de espessura de amostras de alumínio.

No Apêndice A é apresentado o algoritmo base do *Lock-In* e no Apêndice B o código fonte do simulador feito no Matlab. No Apêndice C serão abordados os princípios e teorias a respeito dos Processadores Digitais de Sinal (DSP), seu histórico, princípio de funcionamento, aplicações industriais e científicas e como pode ser utilizado para desenvolvimento de projetos. É mostrada também a estrutura interna de um DSP e alguns exemplos de programas que foram implementados nos ambientes de desenvolvimento de projetos.

# Capítulo 1

## O Amplificador Lock-In

### 1.1 – Introdução

O Processamento de Sinais, de uma forma geral, consiste na análise de sinais, extraíndo informações que possam torná-los úteis para alguma aplicação específica. Esta é uma área que trabalha essencialmente com a modelagem matemática destes sinais, tornando-se a base para toda teoria desenvolvida na realização de seu processamento, seja apenas para sua compreensão, seja para construção de equipamentos ou instrumentos, que são de grande valia para verificação, validação ou detecção de fenômenos físicos.

Dentre as inúmeras possibilidades de trabalho, podemos citar o processamento de sinais de baixa amplitude. Isso se torna especialmente interessante quando se deseja realizar análises das propriedades elétricas ou magnéticas de algum material. Para isso é imprescindível a utilização de um Amplificador *Lock-In* para realização de medidas do sinal através da amostra

O Amplificador *Lock-In*, ou somente *Lock-In*, é um instrumento de grande importância em qualquer laboratório onde se realizam medidas físicas, isso por que este instrumento tem grande facilidade de detectar sinais imersos em ruídos, conseguindo com precisão detectar sua magnitude e fase.

A detecção de fase feita pelo *Lock-In* é feita através da técnica de Detecção Sensível de Fase (PSD)<sup>1</sup>. Esta técnica corresponde à principal função do amplificador, captando apenas o sinal de interesse para a medida, suprimindo o efeito de ruídos ou interferência de componentes ativos.

---

<sup>1</sup> PSD, do inglês *Phase Sensitive Detector*.

Para funcionar corretamente o PSD deve estar programado para funcionar em uma determinada banda de freqüência, ou seja, reconhecer apenas o sinal de interesse para a medida, eliminando freqüências indesejadas. Isto é feito fornecendo-se ao detector uma tensão de referência de mesma freqüência e com uma fase fixa relacionada ao sinal de entrada. O uso deste sinal de referência assegura que o instrumento irá rastrear qualquer mudança na freqüência do sinal que está sendo analisado. Desta característica que se deriva o nome do aparelho. Mais detalhes sobre o PSD serão tratados na seção 1.4 deste Capítulo.

Podemos entender melhor o funcionamento do *Lock-In* através da Figura 1.1 abaixo, onde percebemos como o sinal de entrada provindo de um sistema físico é analisado dentro do equipamento, fornecendo como saída sua medida de fase ou magnitude. O sinal do sistema físico passa primeiro por um ganho, pois geralmente o equipamento é utilizado para medição de sinais de baixíssima amplitude. Após isso se realiza a operação de multiplicação e

Figura 1.1 – Esquemático simplificado de um Amplificador *Lock-In*.

Através do esquema descrito acima percebemos que um *Lock-In* é essencialmente composto por três partes principais: o deslocamento do sinal de referência em  $90^\circ$ , o PSD que realizará os cálculos matemáticos e o integrador. A fundamentação matemática detalhada das

etapas de cada uma destas partes será descrita com maior precisão na seção 1.3 deste Capítulo.

## 1.2 – Lock-In Digital

A criação de um *Lock-In* digital a partir do uso de DSP's fez com que a tarefa de implementar a teoria para criação do equipamento se tornasse muito mais fácil e rápida. Utilizar um DSP visa aumentar a precisão do equipamento, tendo em vista que por ser digital, se torna menos susceptível à interferências externas, principalmente em seus componentes ativos e passivos, como resistores, capacitores e indutores.

Na Figura 1.2 é apresentado um esquema completo de construção de um *Lock-In* digital comercial e analisá-lo a fim de compreender melhor sua estrutura física principal. Percebe-se da figura os principais componentes encontrados no desenvolvimento deste trabalho, como as duas entradas de sinal (“reference input” e “signal input”), o ganho do amplificador da entrada (“input amplifier”), o deslocador de fase (“phase shifter”), a geração da tabela com os valores de seno e cosseno do sinal de referência (“look-up table”), os multiplicadores em fase e em quadratura, correspondentes ao PSD e por fim as saídas de magnitude e fase.

Figura 1.2 – Diagrama completo de construção de um *Lock-In* digital comercial.

Fonte: Signal Recovery [6]

### 1.3 – Detecção Sensível à Fase

Para que haja o entendimento do funcionamento do *Lock-In* é necessário uma compreensão das operações realizadas internamente. O amplificador possui duas entradas, uma de referência e outra para o sinal a ser analisado. Desta forma ocorre uma multiplicação de ambos os sinais, cujo resultado fornece as componentes para o cálculo da fase e magnitude do sinal do sistema físico.

Supõe-se inicialmente um sinal senoidal de referência  $V_{ref} = A \cdot \cos(\omega t)$ , que pode ser gerado internamente pelo *Lock-In* ou fornecido externamente por outro equipamento, e um sinal de entrada  $V_{in} = B \cdot \cos(\omega t + \theta)$ , de mesma freqüência, porém com uma defasagem em relação à referência de  $\theta$ . O processo de detecção consiste em multiplicar os dois sinais, em um processo de multiplicação e acumulação, gerando dois valores numéricos distintos, que serão usados nos cálculos de magnitude e fase, mostrados a seguir:

$$V_{PSD} = A \cdot \cos(\omega_o t) \cdot B \cdot \cos(\omega_o t + \theta)$$

$$\begin{aligned}

&= AB \cdot \cos(\omega_o t) \cdot [\cos(\omega_o t) \cdot \cos(\theta) - \sin(\omega_o t) \cdot \sin(\theta)] \\

&= AB \cdot [\cos^2(\omega_o t) \cdot \cos(\theta) - \cos(\omega_o t) \cdot \sin(\omega_o t) \cdot \sin(\theta)] \\

&= AB \cdot \{[1/2 + 1/2 \cos(2\omega_o t)] \cdot \cos(\theta) - 1/2 \sin(2\omega_o t) \cdot \sin(\theta)\} \\

&= 1/2 AB \cdot \cos(\theta) + 1/2 AB \cdot [\cos(2\omega_o t) \cdot \cos(\theta) - \sin(2\omega_o t) \cdot \sin(\theta)] \\

V_{PSD} &= 1/2 AB \cdot \cos(\theta) + 1/2 AB \cdot \cos(2\omega_o t + \theta) \quad \text{Eq. 1}

\end{aligned}$$

Seja  $U_1$  o valor médio de  $V_{PSD}$  para  $T = 2\pi/\omega_o$ :

$$\begin{aligned}

U_1 &= \frac{1}{T} \int_0^T V_{PSD} dt \\

&= \frac{1}{T} \int_0^T \frac{AB}{2} \cos(\theta) dt + \frac{1}{T} \int_0^T \frac{AB}{2} \cos(2\omega_o t + \theta) dt \\

U_1 &= \frac{AB}{2} \cos(\theta) \quad \text{Eq. 2}

\end{aligned}$$

Analogamente podemos multiplicar o sinal de entrada  $V_{in}$  por  $V_{ref_{90}}$ , que corresponde ao sinal de referência defasado de 90 graus<sup>2</sup>. Sendo assim obtemos o seguinte valor para a saída do PSD:

$$\begin{aligned}

V_{PSD} &= A \cdot \sin(\omega t) \cdot B \cdot \cos(\omega t + \theta) \\

&= AB \cdot \sin(\omega t) \cdot [\cos(\omega t) \cdot \cos(\theta) - \sin(\omega t) \cdot \sin(\theta)] \\

&= AB \cdot [\cos(\omega t) \cdot \sin(\omega t) \cdot \cos(\theta) - \sin^2(\omega t) \cdot \sin(\theta)] \quad \text{Eq. 3}

\end{aligned}$$

Sabendo-se que:  $\sin^2(\omega t) = \frac{[\cos(2\omega t) - 1]}{2}$  Eq. 4

$$\cos(\omega t) \cdot \sin(\omega t) = \frac{\sin(2\omega t)}{2} \quad \text{Eq. 5}$$

---

<sup>2</sup> Correspondente à “look-up table” indicada na Figura 3.2.1.

Substituindo Eq. 4 e Eq. 5 em Eq. 3, obtém-se:

$$V_{PSD} = 1/2 AB \cdot \sin(\theta) + 1/2 AB \cdot \sin(2\omega t + \theta) \quad \text{Eq. 6}$$

Seja  $U_2$  o valor médio de  $V_{PSD}$ :

$$\begin{aligned} U_2 &= \frac{1}{T} \int_0^T V_{PSD} dt \\ &= \frac{1}{T} \int_0^T \frac{AB}{2} \sin(\theta) dt + \frac{1}{T} \int_0^T \frac{AB}{2} \sin(2\omega t + \theta) dt \\ U_2 &= \frac{AB}{2} \sin(\theta) \end{aligned} \quad \text{Eq. 7}$$

Desta forma obtemos os dois valores,  $U_1$  e  $U_2$  que são a chave para o cálculo da fase e da magnitude, no *Lock-In*. É interessante ainda destacar dois pontos importantes com relação à diferença de fase entre o sinal de entrada e a referência. Caso a defasagem entre os dois sinais seja de zero grau ( $\theta = 0^\circ$ ) teremos então que  $U_1 = \frac{AB}{2}$  e  $U_2 = 0$ .

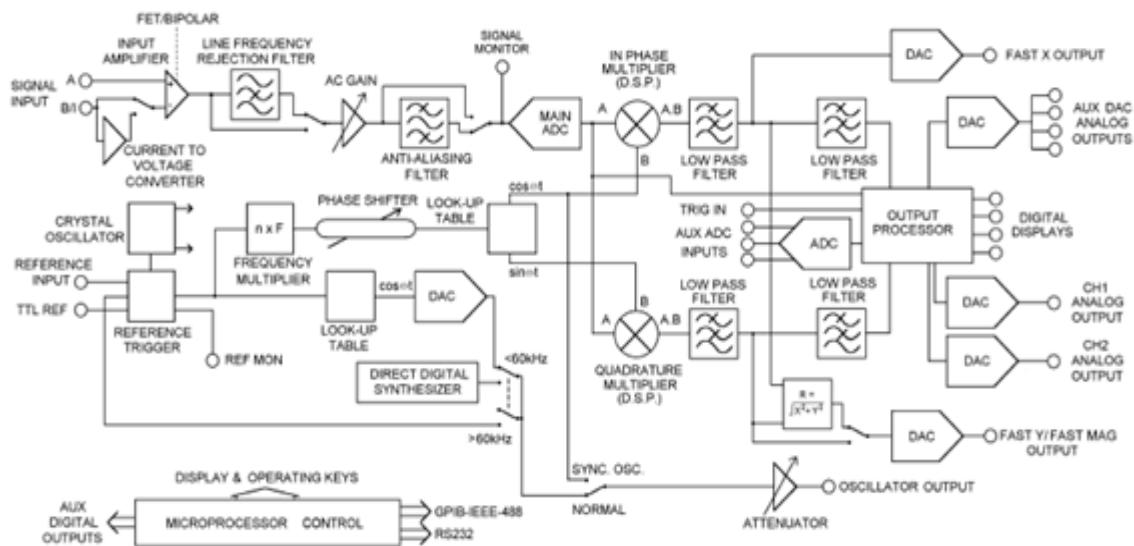

De forma similar podemos destacar o comportamento do PSD quando a defasagem entre os dois sinais é de 90 graus ( $\theta = 90^\circ$ ). Teremos então que  $U_1 = 0$  e  $U_2 = \frac{AB}{2}$ . Neste caso em especial o resultado da multiplicação no PSD, com o sinal defasado, é um sinal de saída com freqüência igual ao dobro da do sinal de entrada, porém com valor médio igual a zero. Esta situação fica mais bem ilustrada na Figura 1.3 abaixo.

Figura 1.3 – Sinal de entrada defasado de 90 graus do sinal de referência, resultando em  $U_1 = 0$  e  $U_2 = \frac{AB}{2}$ . O sinal de saída do PSD fica com freqüência igual ao dobro da do sinal de entrada, todavia com um valor médio nulo.

Desta forma podemos perceber que o nível médio de saída do sinal do PSD depende não somente das amplitudes do sinal de entrada e da referência, mas também da defasagem entre os dois sinais. Para determinar a amplitude do sinal de entrada podemos obter o nível médio do sinal demodulado, correspondente ao sinal multiplicado, fixando o valor da amplitude do sinal de referência, para que este tenha um deslocamento de fase igual a zero em relação ao sinal de entrada.

Toda esta análise feita anteriormente é plausível quando tratamos de sinais livres de ruído, o que não se aplica quando o objetivo é a construção de um protótipo real de um Amplificador *Lock-In*. Os ruídos provenientes do sinal de entrada podem não conter uma freqüência fixa, muito menos um deslocamento de fase fixo em relação à referência.

A presença de ruídos não causa diferença na variação do nível DC do sinal de saída do PSD. As componentes das perturbações do sinal de entrada que são próximas à sua freqüência

irão resultar em sinais com freqüências muito mais baixas na saída do demodulador. Para eliminá-las pode ajustar um filtro passa-baixa para trabalhar com uma freqüência de corte inferior à do sinal de entrada, trabalhando em conjunto com o PSD.

Com todos os cálculos previamente definidos, podemos reordenar o diagrama de funcionamento do *Lock-In*, incluindo desta vez as componentes  $U_1$  e  $U_2$ , que resultarão nas saídas de fase e magnitude do sinal do sistema físico. Tal representação pode ser vista na Figura 1.4.

Figura 1.4 – Esquemático completo de um Amplificador *Lock-In*. O sinal de referência é multiplicado duas vezes para geração das componentes  $U_1$  e  $U_2$ , cada uma destas multiplicações feitas com sinais defasados de 90 graus entre si. Após isso ocorre o cálculo de magnitude e fase, sendo as duas saídas do equipamento.

## Capítulo 2

### Simulando um *Lock-In*

#### 2.1–Algoritmo Base

Todo o desenvolvimento deste trabalho se iniciou a partir da criação de um algoritmo, pelo qual foi possível analisar e entender melhor o funcionamento do *Lock-In*. A partir da teoria definida no Capítulo 1 criou-se uma rotina matemática para modelar a estrutura interna de um *Lock-In*, composto pelo sinal de referência e por um sinal de entrada simulando um sistema físico ruidoso.

Como demonstrado anteriormente, o *Lock-In* tem um forte potencial de detectar o sinal de entrada imerso em ruído, inclusive onde a Relação Sinal-Ruído (SNR) aproxima-se de zero dB. Isso ocorre devido ao uso de um integrador que atua como um filtro eliminando freqüências indesejadas. Tendo em mente essas características, desenvolveu-se uma rotina de cálculos que incluía um sinal proveniente de um sistema físico fictício extremamente ruidoso e um sinal de referência de mesma faixa de freqüência.

A seguir são mostradas as variáveis de entrada do algoritmo desenvolvido para o simulador, com o intuito de comprovar a capacidade do *Lock-In* em medir sinais mesmo em um ambiente altamente ruidoso. Nesta simulação o usuário pode definir a freqüência de amostragem do sinal, ou seja, a quantidade de amostras lidas por segundo, através da definição de variáveis de entrada. O algoritmo completo encontra-se em anexo no final deste documento, no Apêndice A.

| Variáveis de Entrada do Algoritmo |                                                |      |

|-----------------------------------|------------------------------------------------|------|

| FAmos                             | - Freqüência de amostragem do sinal de entrada | [Hz] |

| NPObs                             | - Número de períodos observados                |      |

| NPts                              | - Quantidade de pontos por período             |      |

| SNR                               | - Relação Sinal-Ruído                          | [dB] |

| Fase                              | - Fase do sinal do Sistema-Físico              | [º]  |

| Mag                               | - Magnitude do sinal do Sistema-Físico         | [V]  |

Tabela 2.1 – Significado das variáveis de entrada do programa.

## 2.2–Definição da Experiência

O *Lock-In* foi simulado para realizar medições com freqüência de referência de 1 MHz e amplitude de referência de 1 V<sub>pp</sub>. O sistema físico simulado teve amplitude fixada no valor de 50 mV<sub>pp</sub>, fase de 55º e níveis de ruído com intensidades variando de 0.1 mV<sub>pp</sub> até 1 mV<sub>pp</sub> com freqüência de 200 kHz. As constantes de tempo de simulação (número de períodos observados do sinal) variaram entre 1, 5 e 10 períodos. Na Figura 2.1 podemos encontrar uma

demonstração gráfica do sinal de referência e do sinal do sistema físico. Na Tabela 2.2 a seguir encontram-se resumidos os valores de simulação do Lock-In.

Figura 2.1 – Demonstração do sinal de referência e do sinal do sistema físico.

| Sinal de Referência |              |     |

|---------------------|--------------|-----|

| <b>Magnitude</b>    | ( $V_{pp}$ ) | 1.0 |

| <b>Freqüência</b>   | (kHz)        | 200 |

| Sistema Físico   |               |         |

|------------------|---------------|---------|

| <b>Magnitude</b> | ( $mV_{pp}$ ) | 50      |

| <b>Fase</b>      | ( $^\circ$ )  | 55      |

| <b>Ruído</b>     | ( $mV_{pp}$ ) | 0.1 - 1 |

Tabela 2.2 – Valores de entrada para simulação do amplificador *Lock-In*, a fim de validar a teoria de redução de ruídos. Inicialmente utilizou-se ruído com 0.1  $mV_{pp}$  finalizando a experiência com ruído de 1  $mV_{pp}$ .

A partir desta simulação, obteve-se uma seqüência de resultados interessante. Na Tabela 2.3 podemos observar de que forma o *Lock-In* se comporta de acordo com a quantidade amostras observadas para a integração do sinal. Podemos perceber que quanto maior a freqüência de amostragem, maior a resolução do sinal, prova disso é a Relação Sinal-Ruído, que aumenta de acordo com a precisão do cálculo da magnitude. Vale lembrar que a freqüência de amostragem, definida por FAmos, é igual ao produto entre o número de pontos do sinal e sua freqüência.

$$N_{pontos} = \frac{FAmos}{f_{entrada}}$$

| CT | FAmos ( $\times 10^6$ ) | SNR (dB) | Fase (º) | Mag (V) |

|----|-------------------------|----------|----------|---------|

| 1  | 10                      | 26.465   | 61.19    | 0.44    |

| 1  | 20                      | 29.759   | 64.38    | 0.46    |

| 1  | 50                      | 32.235   | 57.72    | 0.51    |

| 1  | 100                     | 38.546   | 55.99    | 0.52    |

| 5  | 10                      | 34.447   | 57.15    | 0.50    |

| 5  | 20                      | 36.876   | 54.42    | 0.49    |

| 5  | 50                      | 40.076   | 53.86    | 0.49    |

| 5  | 100                     | 44.431   | 55.78    | 0.50    |

| 10 | 10                      | 36.493   | 55.61    | 0.50    |

| 10 | 20                      | 39.722   | 55.51    | 0.50    |

| 10 | 50                      | 45.076   | 54.16    | 0.50    |

| 10 | 100                     | 46.153   | 54.51    | 0.49    |

Tabela 2.3 – Resultados obtidos com nível de ruído de 0.1 mV<sub>pp</sub>.

Outro ponto interessante a se observar é a variação do resultado com relação ao aumento da constante de tempo, ou seja, a quantidade de períodos que entram na janela de integração do PSD. Quanto maior a quantidade de períodos, maior a quantidade de amostras observadas e consequentemente uma maior precisão no cálculo de magnitude e fase.

Para fins de visualização, vamos agora mostrar resultados obtidos quando variamos o nível de ruído para dois valores distintos. Primeiramente um teste com ruído em 0.5 mV<sub>pp</sub>, numa faixa mediana de perturbação e depois uma simulação com um sinal de entrada altamente ruidoso, de 1 mV<sub>pp</sub>.

| CT | FAmos ( $\times 10^6$ ) | SNR (dB) | Fase (º) | Mag (V) |

|----|-------------------------|----------|----------|---------|

| 1  | 10                      | 13.176   | 51.74    | 0.37    |

| 1  | 20                      | 15.411   | 49.98    | 0.62    |

| 1  | 50                      | 19.719   | 64.27    | 0.52    |

| 1  | 100                     | 21.872   | 46.36    | 0.44    |

| 5  | 10                      | 18.840   | 62.80    | 0.55    |

| 5  | 20                      | 21.633   | 69.63    | 0.40    |

| 5  | 50                      | 25.551   | 50.94    | 0.56    |

|    |     |        |       |      |

|----|-----|--------|-------|------|

| 5  | 100 | 27.559 | 46.83 | 0.48 |

| 10 | 10  | 23.275 | 44.27 | 0.47 |

| 10 | 20  | 24.649 | 65.37 | 0.56 |

| 10 | 50  | 27.902 | 51.48 | 0.53 |

| 10 | 100 | 34.202 | 53.92 | 0.51 |

Tabela 2.4 – Resultados obtidos com nível de ruído de 0.5 mV<sub>pp</sub>.

| CT | FAmos ( $\times 10^6$ ) | SNR (dB) | Fase (º) | Mag (V) |

|----|-------------------------|----------|----------|---------|

| 1  | 10                      | 10.191   | 66.55    | 0.72    |

| 1  | 20                      | 10.719   | 55.16    | 0.37    |

| 1  | 50                      | 14.417   | 30.26    | 1.10    |

| 1  | 100                     | 16.271   | 63.23    | 0.66    |

| 5  | 10                      | 12.826   | 66.48    | 0.79    |

| 5  | 20                      | 16.981   | 81.49    | 0.77    |

| 5  | 50                      | 18.914   | 55.34    | 0.56    |

| 5  | 100                     | 25.000   | 53.43    | 0.59    |

| 10 | 10                      | 17.269   | 29.73    | 0.56    |

| 10 | 20                      | 17.833   | 65.76    | 0.42    |

| 10 | 50                      | 23.631   | 59.21    | 0.48    |

| 10 | 100                     | 24.183   | 51.13    | 0.50    |

Tabela 2.5 – Resultados obtidos com nível de ruído de 1 mV<sub>pp</sub>.

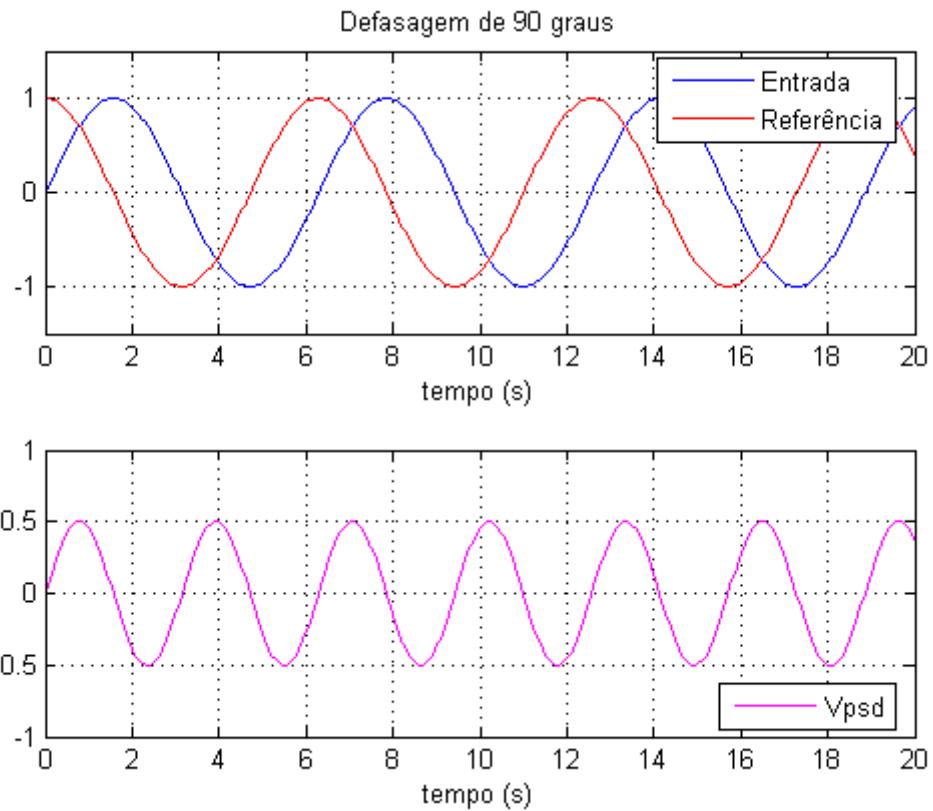

Percebemos na Figura 2.2 que quanto maior a Freqüência de Amostragem do sinal de entrada, ou seja, quanto mais pontos são utilizados para o cálculo, maior a precisão do resultado, pois se consegue minimizar os efeitos do ruído. Aliado a uma maior quantidade de períodos integrados, esta precisão aumenta ainda mais.

Figura 2.2 – Gráfico comparativo da Relação Sinal-Ruído entre vários tipos de sinal de entrada, com ruídos variando entre  $0.1 \text{ mV}_{\text{pp}}$  e  $1.0 \text{ mV}_{\text{pp}}$ . Quanto maior a relação entre a freqüência de amostragem e o numero de períodos observados, melhor a SNR, ou seja, menos o ruído interfere no cálculo do *Lock-In*.

Os resultados apresentados na Tabela 2.5 mostram um nível de ruído de  $0.5 \text{ mV}_{\text{pp}}$ . Para obtenção do valor da magnitude não houve muita discrepância, mas no valor de fase houve relativa diferença entre o valor desejado e o calculado. A fase só conseguiu estabilizar perto do valor de entrada com um numero maior de períodos observados.

Na Tabela 2.6 vemos um caso crítico, onde o sinal de entrada está completamente imerso em ruídos. Neste caso para conseguir fazer a leitura eficiente da fase e magnitude é necessário uma maior quantidade de períodos integrados no cálculo de  $U_1$  e  $U_2$ . Podemos perceber também que se mantendo um numero fixo de períodos observados e variando apenas o numero de pontos do sinal de entrada, a diferença de valores é grande. Por exemplo: com 5 períodos integrados e 50 amostras observadas obteve-se um valor bem diferença do esperado. Apenas com uma quantidade de amostras cinco vezes maior, de 250, é que se conseguiu um valor significativo em relação ao original.

Esta experiência é importante para mostrar que o *Lock-In* é um dispositivo adaptativo, ou seja, se o sinal de entrada do sistema físico é um sinal com baixa taxa de ruído, pode-se diminuir a quantidade de pontos analisados, o que aumenta a rapidez do equipamento. Porém se faz necessário uma maior precisão ou se o sinal de entrada é extremamente ruidoso, podemos aumentar a quantidade de pontos integrados, o que diminui os efeitos das perturbações.

## 2.3 – Desenvolvimento de um Simulador

Com o intuito de demonstrar graficamente o funcionamento do algoritmo, foi desenvolvido em *Matlab* um simulador iterativo, onde o usuário pode definir todas as características do sistema envolvido, definindo as variáveis de entrada de uma amostra, bem como o nível de ruído no qual esta amostra se encontra.

O interessante neste simulador é verificar como o *Lock-In* se comporta entre o momento transiente, antes da janela de integração estar completa com o sinal e o instante em que entra em regime permanente, conseguindo manter praticamente constantes os valores de magnitude e fase.

Na Figura 2.3 podemos encontrar uma imagem da janela do simulador, feito através da ferramenta gráfica *Guide*, presente do *Matlab*, versão 7.0 R14. O código fonte deste programa encontra-se em anexo no Apêndice B, no final deste documento.

Figura 2.3 – Imagem de tela do simulador de *Lock-In*. Como entrada o usuário pode definir o valor da amplitude, freqüência e o número de amostras do sinal de referência, além de poder configurar o nível de ruído através do valor da Relação Sinal-Ruído (SNR), da fase e da magnitude do sinal provindo do sistema físico.

De acordo com a Figura 2.3 podemos perceber o desempenho do simulador em calcular o valor de magnitude e fase com extrema precisão. No cálculo da amplitude do sinal do sistema físico o simulador forneceu o resultado com um erro de aproximadamente 0,9% e para a fase com um erro de aproximadamente 0,5%, se enquadramento perfeitamente nos padrões matemáticos toleráveis.

## 2.4 – Análise de Resultados

A partir dos gráficos abaixo podemos perceber como o Algoritmo Base do *Lock-In* se aproxima fielmente ao resultado esperado. Foram feitas uma série de simulações, onde se variou o nível de ruído do sinal de entrada, o número de períodos observados e a quantidade de pontos observados em cada período.

Esta simulação foi feita com o intuito de mostrar o quanto o algoritmo é preciso em relação ao cálculo de magnitude e fase. Mesmo com níveis de ruído altos o *Lock-In* conseguiu achar o resultado muito próximo do esperado. Todos os testes simularam um sistema com um sinal de um sistema físico de amplitude 0.5V e fase de 55°.

$$f(t) = 0.5 \sin(\omega t + 55^\circ)$$

Na Figura 2.4 podemos analisar dois testes feitos com ruído de 0.1 mV<sub>pp</sub>. O primeiro resultado mostra o histograma dos resultados obtidos com apenas 1 período observado, variando-se de 10 a 1000 pontos por período. Neste caso a distribuição mostrou-se bem concentrada, próxima de 55°, com o centro coincidindo à curva gaussiana, onde 65% das amostras convergiram para o resultado esperado.

Figura 2.4 – Distribuição dos resultados do cálculo de fase com nível de ruído de 0.1 mV<sub>pp</sub>, com 1 e 10 períodos observados para uma fase de 55°.

No segundo teste observamos que o maior número de períodos observados fez com que houvesse uma maior concentração ao redor do valor correto da fase, de 55°. Apesar da maior precisão, o fato do nível de ruído ser muito baixo, executar o algoritmo com menos períodos observados e menos pontos torna a rotina mais rápida, melhorando assim a resposta do DSP na hora de realizar os cálculos, caso fosse implementado.

Na Figura 2.5 percebemos que praticamente 100% dos resultados obtidos aproximaram-se do valor indicado de 0.5V tanto para 1 período observado, quanto para 10. Este resultado era esperado, tendo em vista o baixo nível de ruído, facilitando o cálculo da magnitude, que fica menos sujeita à variações de resultado, devido às perturbações.

Figura 2.5 – Distribuição dos resultados do cálculo de magnitude com nível de ruído de  $0.1 \text{ mV}_{\text{pp}}$ , com 1 e 10 períodos observados para uma amplitude de 0.5V.

Na Figura 2.4.3 simulamos uma situação onde o nível de ruído corrompe por completo o sinal de entrada. Neste caso o valor da fase fica bastante comprometido, fazendo-se necessário uma maior quantidade de períodos observados para compensar a baixa precisão do sinal do sistema físico. A execução da rotina com 10 períodos integrados fez com que fosse diminuído o efeito alto nível de perturbação.

Figura 2.6 – Distribuição dos resultados do cálculo de fase com nível de ruído  $1 \text{ mV}_{\text{pp}}$ , com 1 e 10 períodos observados para fase de  $55^\circ$ . O alto nível de perturbação aliado com uma baixa amostragem do sinal, fez com que a resolução para 1 período de observação fosse muito ruim. Neste caso apenas 10% das amostras se aproximaram do valor desejado, o que não aconteceu quando aumentamos para 10 períodos, onde a gaussiana retrata a maior precisão no cálculo, com aproximadamente 30% das amostras próximas do centro.

Na Figura 2.7 retratamos o comportamento do *Lock-In* para o cálculo de magnitude com um nível de ruído  $1 \text{ mV}_{\text{pp}}$ . Nesta ambiente altamente ruidoso a simulação mostrou que mesmo assim o algoritmo foi robusto, sofrendo pouca variação no resultado. Com 1 período de observação, encontramos mais de 70% das amostras com o valor próximo a 0.5V, e com 10 períodos de observação em torno de 80% das amostras ficaram próximas ao valor desejado.

Para um ambiente muito ruidoso, representado por um nível de  $1 \text{ mV}_{\text{pp}}$  de ruído, o sistema se comportou de forma pouco precisa com apenas 1 período observado, obtendo maior sucesso nos cálculos quando integrados 10 períodos do sinal de entrada. Podemos observar também a maior sensibilidade do *Lock-In* para obter os resultados de fase, onde a variância foi muito maior.

Figura 2.8 – Distribuição dos resultados do cálculo de magnitude com nível de ruído  $1 \text{ mV}_{\text{pp}}$ . O alto nível de perturbação não foi suficiente para desviar o padrão de resultado do algoritmo.

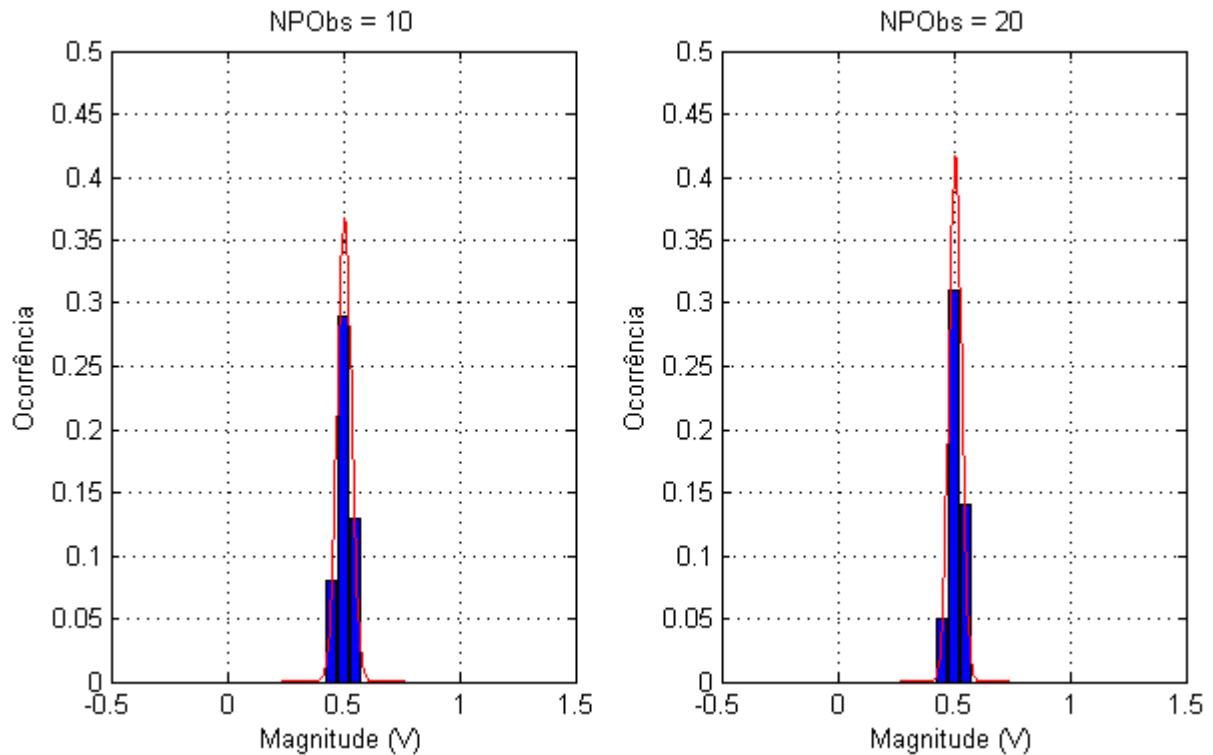

A fim de validar ainda mais o processo estatístico confrontamos o algoritmo a um ambiente ainda mais hostil, com nível de ruído  $2 \text{ mV}_{\text{pp}}$ , extremamente alto, porém submetido a uma análise mais criteriosa, com 10 e 20 períodos de observação, contendo cada período entre 500 e 1000 pontos.

Os resultados obtidos para o cálculo de fase, na Figura 2.9 abaixo, reforçam a alta sensibilidade do *Lock-In* para obtenção da fase do sistema físico. Mesmo com as amostras tendendo a uma distribuição normal próxima do valor de  $55^\circ$ , não houve grande acúmulo de resultados próximos deste valor, que variaram entre  $50^\circ$  e  $65^\circ$ .

Figura 2.9 – Histograma dos resultados de fase com nível de ruído 2 mV<sub>pp</sub>.

Figura 2.10 – Histograma dos resultados de magnitude com ruído de 2 mV<sub>pp</sub>.

A Figura 2.10 mostra os resultados obtidos para o cálculo de magnitude do sinal do mesmo sistema com nível de ruído  $2 \text{ mV}_{\text{pp}}$ . Percebemos que o *Lock-In* se comportou de forma bastante homogênea, conseguindo obter valores próximos da amplitude original em quase todas as amostras.

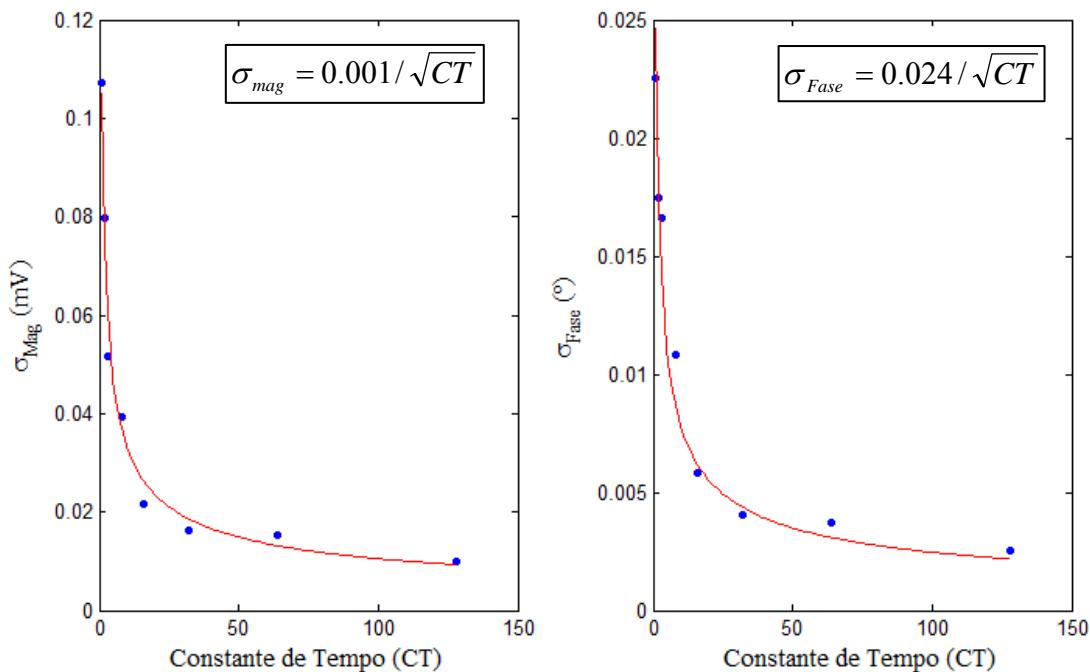

## 2.5 – Comportamento do Desvio Padrão das Medidas

Com os dados de magnitude e fase são traçados gráficos que relacionam o desvio padrão das amostras com a constante de tempo (CT). Neste gráfico, mostrado na Figura 2.11 abaixo, podemos perceber que o *Lock-In* varia exponencialmente com relação com CT, ou seja, quanto maior o número de períodos observados, maior a precisão.

Figura 2.11 – Desvio padrão das medições de magnitude e fase com simulação de ruído de  $0.5 \text{ mV}_{\text{pp}}$  e  $F_{\text{ref}} = 0.5 \text{ MHz}$ . Os gráficos mostram que o comportamento exponencial varia inversamente com a raiz quadrada da constante de tempo de integração.

## 2.6 – Conclusões

Os resultados das simulações mostram como o *Lock-In* se comporta em ambientes altamente ruidosos. Para níveis de ruído baixos, com sinal praticamente limpo, conseguiu-se obter os valores de magnitude e fase com poucas amostras, observando-se apenas 1 período do sinal de entrada. Porém isso não se repetiu ao aumentarmos o nível de perturbação do sinal. Ao elevarmos os níveis de ruído para  $1 \text{ mV}_{\text{pp}}$  e  $2 \text{ mV}_{\text{pp}}$ , representando situações altamente distorcidas, o *Lock-In* precisou de um número maior de amostras e de períodos observados para conseguir analisar a amplitude e o deslocamento de fase.

Outro ponto interessante a ser destacado foi o fato do *Lock-In* ser muito mais sensível no cálculo de fase do que em magnitude. Podemos perceber pelos histogramas anteriores que para o cálculo de fase foram necessários mais pontos, ao passo que para o valor de magnitude, com poucas amostras o resultado já se estabelecia, mostrando o quanto o *Lock-In* é capaz de fazer redução de ruídos, eliminando-os, a fim de fornecer um resultado bastante preciso.

# Capítulo 3

## DSP Altera Stratix II EP2S60

### 3.1 – Altera Stratix® II EP2S60 DSP

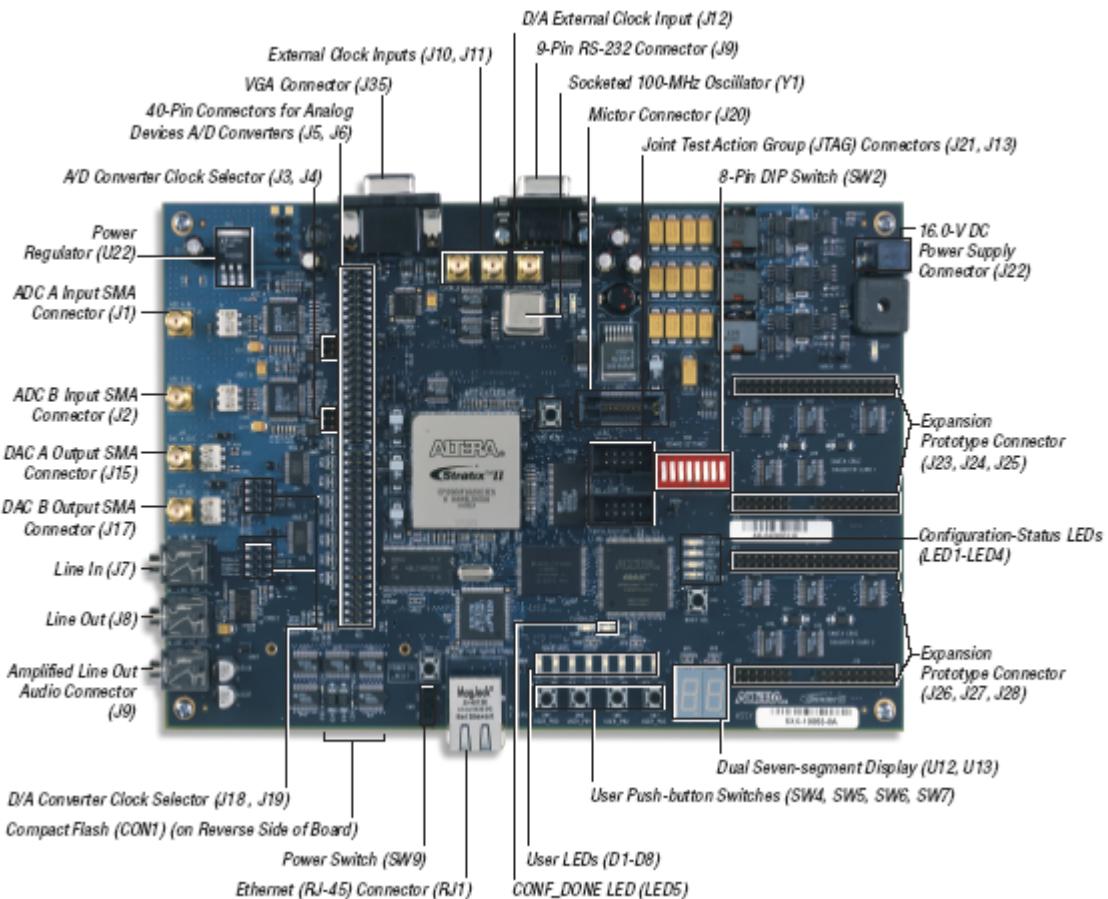

A família Stratix II é a segunda geração de DSP's da Altera, atualmente em sua quarta geração. Este modelo é uma plataforma programável de alto desempenho que possui interface inclusive com outros DSP's de outros fabricantes, como da *Texas Instruments* e *Analog Devices*. Possui conversores A/D e D/A de alta velocidade, bem como interruptores programáveis e displays de sete segmentos. Abaixo segue uma lista detalhada de todos os componentes e características físicas do kit de desenvolvimento EP2S60:

- Conversores:

- Dois conversores A/D 12-bits 125 MHz

- Dois conversores D/A 14-bits 165 MHz

- Três conversores D/A 8-bits para saída VGA (180 mpx/s)

- Um codec de 96 kHz stéreo para saída de áudio

- Memória:

- 1 MB de SRAM (10 ns) assíncrona com barramento de 32-bit

- 16 MB de memória flash com barramento de 8-bit

- 32 MB de memória SDRAM com barramento de a 64-bit

- Conector CompactFlash suportando modos de acesso ATA e IDE

- Configurações

- Configuração on-board de 16 MB de memória flash (EPM7256 MAX)

- Configuração por download dos dados usando USB

- Sistema de Expansão

- Dois conectores para placa filha com Conversores A/D

- Dois conectores de expansão e prototipagem.

- Outros itens:

- Display duplo de sete segmentos

- Quatro interruptores programáveis

- Uma entrada RS-232 (conector fêmea de 9-pin)

- Interface Ethernet 10/100 Mbps

- Oito LED's programáveis

- Oscilador 100-MHz (em soquete)

- Sistema de ventilação ativo (*cooler*)

Na Figura 3.1 abaixo podemos identificar estes componentes individualmente e ter uma visão geral da arquitetura da placa.

Figura 3.1 – Esquemático da arquitetura do DSP EP2S60.

Fonte: Data Sheet DS-S29804

### 3.1.1 – Descrições gerais do kit

O kit de desenvolvimento Altera Stratix II EP2S60 DSP possui uma série de interfaces e de componentes adaptados ao desenvolvimento de aplicações para Processamento Digital de Sinais. Nesta seção, na Tabela 3.1, serão mostrados os principais componentes da placa, detalhando-os e descrevendo-os, para melhor entendimento de seu funcionamento. Na Tabela 3.1.2 são mostradas as interfaces de debug e de expansão da placa.

| Interface                           | Tipo    | Designação           | Descrição                                                                                                                                                                                                      |

|-------------------------------------|---------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Stratix II                          | FPGA    | U18                  | EP2S60 StratixII.                                                                                                                                                                                              |

| Dispositivo MAX                     | PLD     | U10                  | EPM7256ETC144.                                                                                                                                                                                                 |

| Conversores A/D                     | E/S     | U1 e U2              | Conversores 12bits 125 MHz.                                                                                                                                                                                    |

| Conversores D/A                     | E/S     | U14 e U15            | Conversores 14bits 165 MHz.                                                                                                                                                                                    |

| 01 MB SRAM                          | Memória | U43 e U44            | 1 MB, 10ns, SRAM assíncrona (32-bit).                                                                                                                                                                          |

| 16 MB Memória Flash                 | Memória | U17                  | 16 MB de memória flash (8-bit).                                                                                                                                                                                |

| 32 MB SDRAM                         | Memória | U39 e U40            | 32 MB de memória SDRAM (64-bit).                                                                                                                                                                               |

| Conectores SMA (clock)              | Entrada | J10, J11 e 12        | Conectores SMA para entrada de clock externo com terminadores de 50 W.                                                                                                                                         |

| Display de 7 segmentos              | Display | U12 e U13            | Display duplo de sete segmentos.                                                                                                                                                                               |

| Interruptores                       | E/S     | SW4, SW5, SW6 e SW7. | Quatro interruptores que podem ser definidos como lógica de entrada pelo usuário.                                                                                                                              |

| LEDs                                | Display | D1 – D8              | Oito LEDs que podem ter suas funções definidas pelo usuário.                                                                                                                                                   |

| Power On-LED                        | Display | LED7                 | Acesso quando o kit está alimentado.                                                                                                                                                                           |

| LED de configuração                 | Display | LED5                 | Acesso quando a configuração foi carregada com sucesso no dispositivo Stratix II.                                                                                                                              |