UNIVERSIDADE FEDERAL DO RIO DE JANEIRO

ESCOLA POLITÉCNICA

DEPARTAMENTO DE ELETRÔNICA E DE COMPUTAÇÃO

PROPOSTA DE ARQUITETURA DO DEMODULADOR DIGITAL PARA O TERMINAL

DE CONSULTA AO CONSUMO INDIVIDUAL DO SISTEMA DE MEDIÇÃO

CENTRALIZADA

Autor:

---

Suzana Cândida Gomes de Oliveira

Orientador:

---

Prof. José Eduardo da Rocha Alves Jr., D.Sc

Co-Orientadora:

---

Profa. Mariane Rembold Petraglia, Ph.D

Examinador:

---

Prof. Joarez Bastos Monteiro, D.Sc

DEL

SETEMBRO DE 2008

# **Dedicatória**

Aos meus pais, pelo apoio, dedicação e amor infinitos.

# Agradecimentos

Ao pesquisador José Eduardo da Rocha Alves Jr., pelos ensinamentos, orientação, apoio, paciência, pelo enorme coração que possui e por acreditar em mim mesmo quando eu duvidava.

À professora Mariane Rembold Petraglia, pela orientação neste projeto e por ensinar tudo que sei sobre Processamento de Sinais.

Ao professor Joarez Bastos Monteiro, pela participação na banca de avaliação de defesa do projeto final e por uma das melhores aulas do curso da graduação da Engenharia Eletrônica da UFRJ.

Aos pesquisadores César Jorge Bandim e Fábio Cavaliere de Souza, pelo apoio, incentivo e pelas proveitosas discussões técnicas.

Ao meu melhor amigo e namorado Roberto Ilidio Lopes Correia, por todo apoio e dedicação mesmo à distância.

Aos meus amigos Luiz Henrique, Felipe, Diogo (Profeta), Gustavo (Guti), Gustavo Bergter, Reginaldo, Thiago (Japa), Rafael Rosa e Aquino, pela amizade e por compartilhar esses cinco anos de inspiração e muita transpiração.

A todos os profissionais da equipe de medição de energia elétrica do CEPEL, pelo apoio constante.

# Resumo

Este projeto apresenta a proposta e o estudo de uma solução digital para implementar o demodulador do Terminal de Consulta ao Consumo Individual (TCCI) do Sistema Eletrônico de Monitoração Individualizada de Consumo (SEMIC).

O trabalho está baseado em simulações utilizando a ferramenta Simulink do software matemático MATLAB. Através dele, foram feitos testes para a avaliação do desempenho do demodulador em relação a dois principais problemas que na prática poderiam afetar o bom funcionamento do sistema. São eles: harmônicos e transitórios ambos inerentes à rede elétrica.

Como se vislumbra uma futura implementação em dispositivos do tipo DSP (Digital Signal Processor) ou dsPIC, o algoritmo proposto para a detecção da onda portadora PLC (Power Line Carrier), embora esteja sendo realizado em MATLAB, teve como base operações facilmente implementáveis nesses processadores.

Além disso, já que o TCCI será instalado em cada residência, sua produção será em larga escala o que acarreta grande preocupação quanto ao custo do projeto. Então, a arquitetura do demodulador apresentada neste trabalho foi desenvolvida em ponto fixo uma vez que processadores já preparados para aritmética de ponto flutuante são presumidamente mais caros.

# **Palavras-Chave**

Processamento de Sinais

PLC unidirecional

Simulação em MATLAB

Demodulador Digital

Ponto Fixo

# Índice

|                                                          |             |

|----------------------------------------------------------|-------------|

| <i>Dedicatória</i> .....                                 | <i>ii</i>   |

| <i>Agradecimentos</i> .....                              | <i>iii</i>  |

| <i>Resumo</i> .....                                      | <i>iv</i>   |

| <i>Palavras-Chave</i> .....                              | <i>v</i>    |

| <i>Índice</i> .....                                      | <i>vi</i>   |

| <i>Lista de Figuras</i> .....                            | <i>viii</i> |

| <i>Glossário, Abreviaturas, Siglas e Símbolos</i> .....  | <i>xi</i>   |

| Capítulo 1: Introdução.....                              | 13          |

| 1.1 Objetivo.....                                        | 17          |

| 1.2 Organização do Trabalho.....                         | 18          |

| Capítulo 2: O Demodulador Digital do TCCI.....           | 19          |

| 2.1 Características e Especificações do Projeto .....    | 19          |

| 2.1.1 Modulação do Sinal Injetado.....                   | 19          |

| 2.1.2 Sinal Injetado.....                                | 20          |

| 2.2 Modelo Proposto.....                                 | 22          |

| 2.2.1 Atenuador de Entrada.....                          | 23          |

| 2.2.2 Filtro Anti-Aliasing.....                          | 24          |

| 2.2.3 Amostrador e Conversor AD (Analógico/Digital)..... | 26          |

| 2.2.4 Filtro Passa-Banda Digital.....                    | 33          |

| 2.2.5 Aritmética em Ponto Fixo.....                      | 41          |

| 2.2.6 Detector de Amplitude.....                         | 53          |

| 2.2.7 Interpretador.....                                 | 55          |

| Capítulo 3: Ensaios e Resultados.....                    | 61          |

| 3.1 Ensaios com Harmônicos.....                          | 61          |

| 3.1.1 Caso Padrão.....                                   | 61          |

| 3.1.2 Casos com Atenuação da Portadora.....              | 64          |

| 3.1.3 Caso com Aumento dos Harmônicos.....               | 66          |

| 3.2 Ensaio em Transitório .....                          | 68          |

| 3.2.1 Modelo da Rede de Distribuição.....                | 68          |

| 3.2.2 Resultado.....                                     | 70          |

| Capítulo 4: Conclusão.....                               | 75          |

|                                                                |    |

|----------------------------------------------------------------|----|

| <i>Referências Bibliográficas.....</i>                         | 78 |

| <i>Apêndice A: Cálculo da Taxa de Transmissão Mínima .....</i> | 80 |

| <i>Apêndice B: Script do MATLAB usado nas simulações.....</i>  | 81 |

# **Lista de Figuras**

|                                                                               |    |

|-------------------------------------------------------------------------------|----|

| <i>Figura 1: Canal de Comunicação entre Concessionária e Consumidor.....</i>  | 15 |

| <i>Figura 2: Terminal de Consulta ao Consumo Individual (TCCI).....</i>       | 16 |

| <i>Figura 3: Modulação “Ripple Control”.....</i>                              | 20 |

| <i>Figura 4: Espectro de Freqüência de acordo com a Norma da IEC.....</i>     | 21 |

| <i>Figura 5: Diagrama de Blocos do Receptor de Onda Portadora do STC.....</i> | 22 |

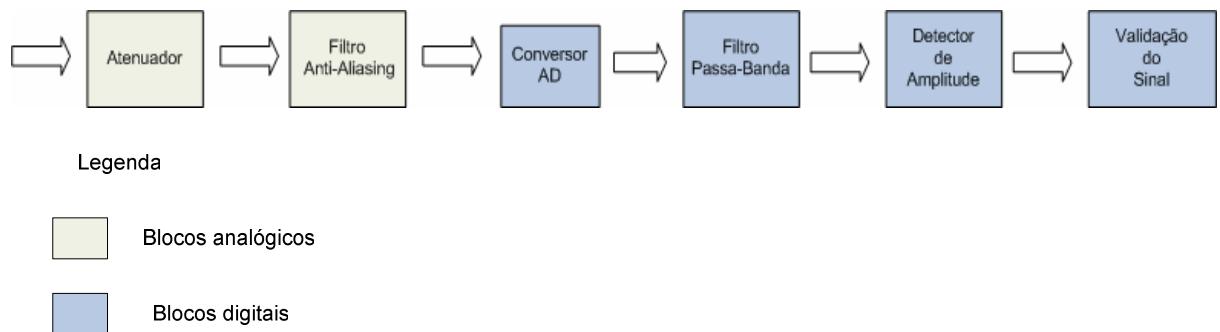

| <i>Figura 6: Diagrama de Blocos do Demodulador do TCCI.....</i>               | 23 |

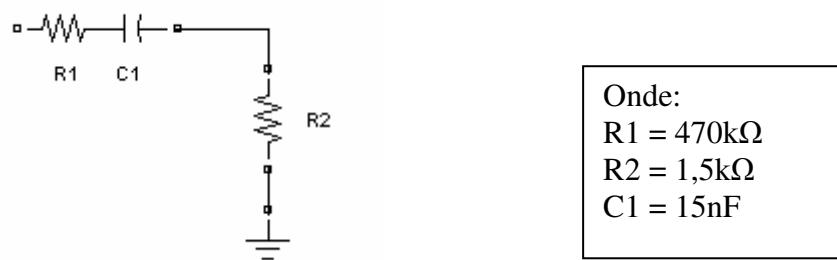

| <i>Figura 7: Circuito Atenuador.....</i>                                      | 23 |

| <i>Figura 8: Resposta em Freqüência do Circuito Atenuador.....</i>            | 24 |

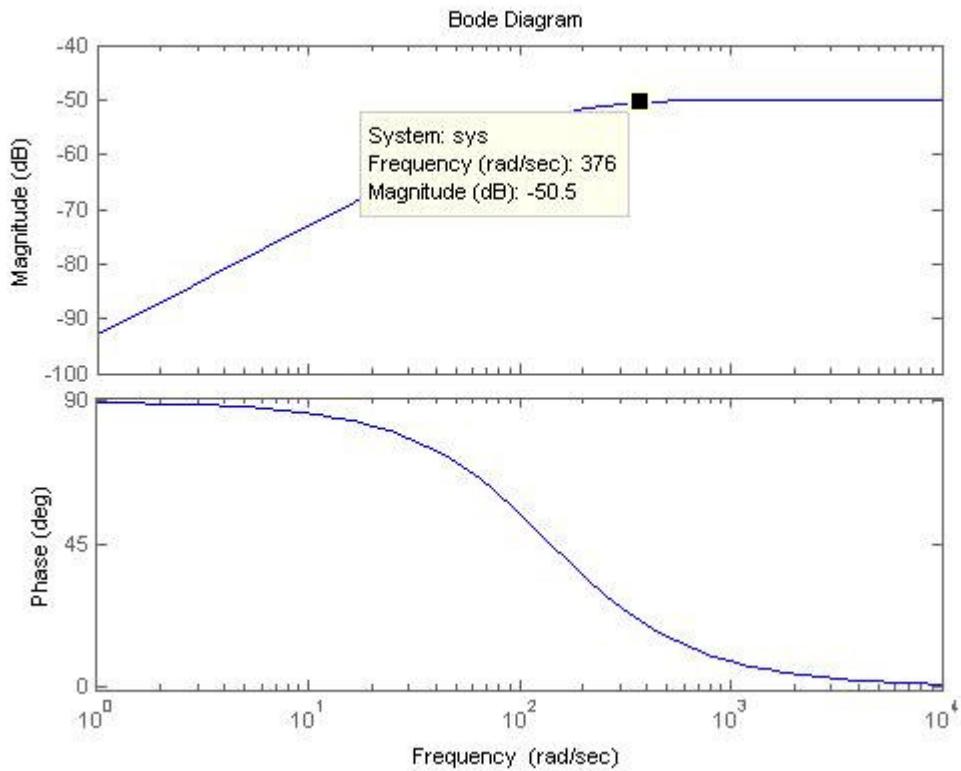

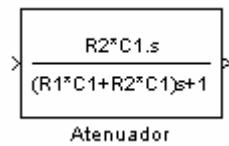

| <i>Figura 9: Representação do Circuito Atenuador no Simulink.....</i>         | 24 |

| <i>Figura 10: Circuito do Filtro Anti-Aliasing.....</i>                       | 25 |

| <i>Figura 11: Resposta em Freqüência do Filtro Anti-Aliasing.....</i>         | 26 |

| <i>Figura 12: Representação do Filtro Anti-Aliasing no Simulink.....</i>      | 26 |

| <i>Figura 13: Representação do Conversor AD no Simulink.....</i>              | 27 |

| <i>Figura 14: Exemplo de funcionamento do “Zero-Order Hold”.....</i>          | 27 |

| <i>Figura 15: Função de Transferência do Conversor AD.....</i>                | 29 |

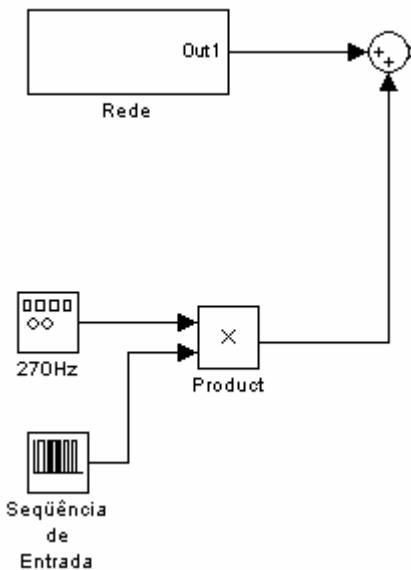

| <i>Figura 16: Esquemático da Simulação em “Simulink”.....</i>                 | 30 |

| <i>Figura 17: Sinal de Entrada Composto pela Superposição.....</i>            | 30 |

| <i>Figura 18: Sinal na Saída do Atenuador.....</i>                            | 31 |

| <i>Figura 19: Sinal Amostrado e Quantizado.....</i>                           | 32 |

| <i>Figura 20: “Zoom” do Sinal Amostrado e Quantizado.....</i>                 | 32 |

| <i>Figura 21: Resposta em Freqüência do Filtro Passa-Banda Analógico.....</i> | 34 |

|                                                                                                  |    |

|--------------------------------------------------------------------------------------------------|----|

| <i>Figura 22: “Zoom” da Resposta em Freqüência do Filtro Passa-Banda Analógico.....</i>          | 34 |

| <i>Figura 23: Resposta em Freqüência do Filtro Passa-Banda Digital.....</i>                      | 36 |

| <i>Figura 24: ”Zoom” da Resposta em Freqüência do Filtro Passa-Banda Digital.....</i>            | 37 |

| <i>Figura 25: Respostas em Freqüência dos Filtros Passa-Banda Analógico e Digital.....</i>       | 37 |

| <i>Figura 26: Implementação do Filtro Passa-Banda Digital no Simulink.....</i>                   | 38 |

| <i>Figura 27: Método de Injeção da Onda Portadora.....</i>                                       | 39 |

| <i>Figura 28: Comparação entre os Filtros Passa-Banda Analógico e Digital no Simulink.....</i>   | 40 |

| <i>Figura 29: Sinais nas Saídas dos Filtros Passa-Banda Analógico e Digital.....</i>             | 40 |

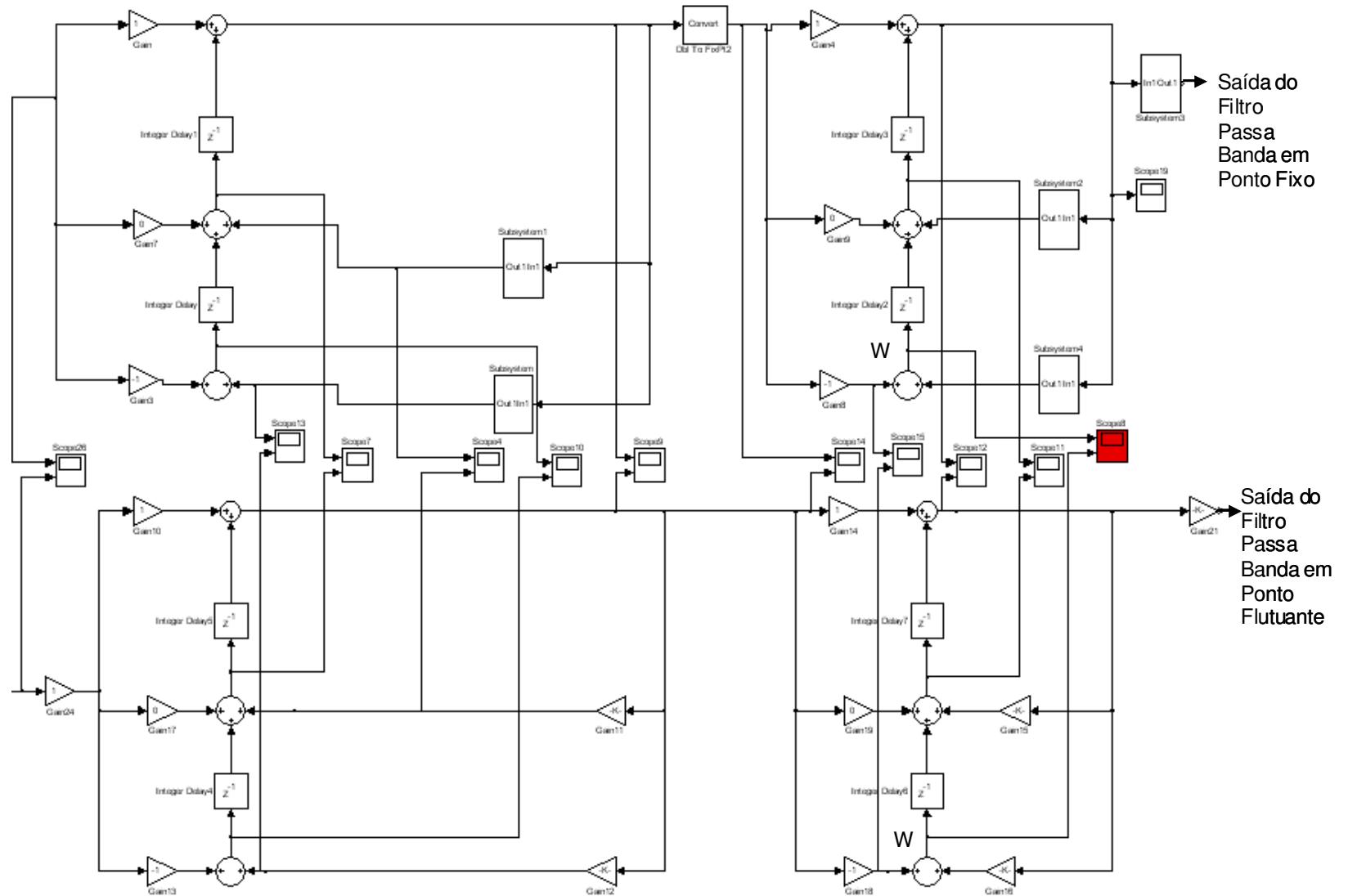

| <i>Figura 30: Implementação do Filtro Passa-Banda Digital em Ponto Fixo no Simulink.....</i>     | 42 |

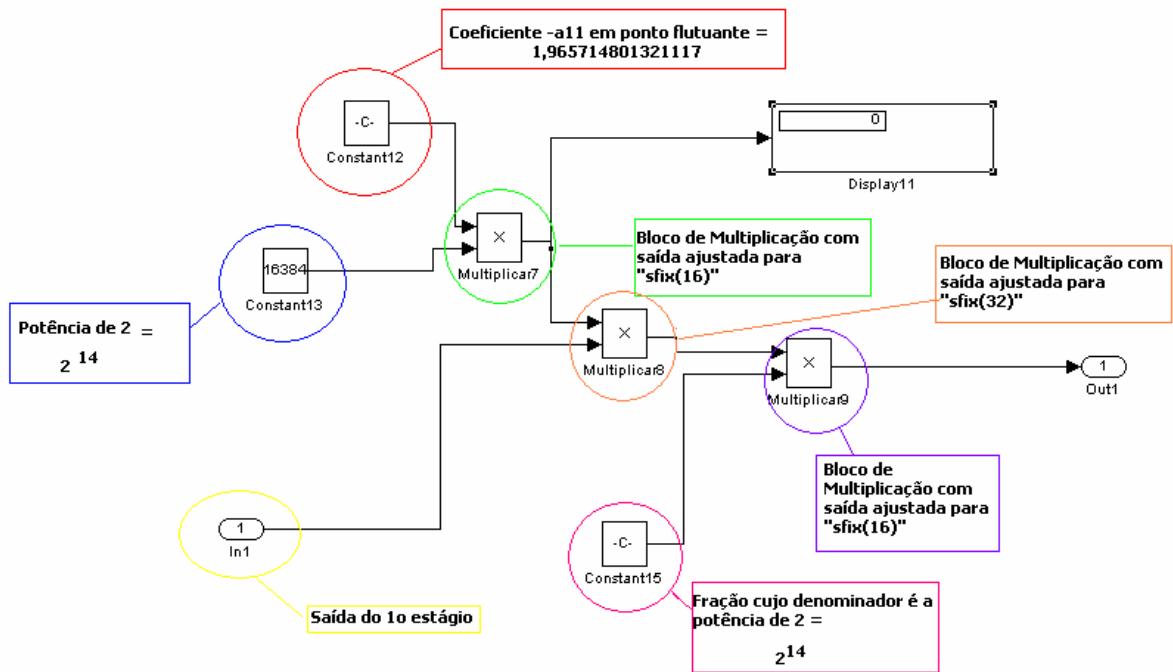

| <i>Figura 31: Interior do Subsistema correspondente ao coeficiente <math>-a_{11}</math>.....</i> | 44 |

| <i>Figura 32: Interior do Subsistema correspondente ao coeficiente <math>-a_{21}</math>.....</i> | 44 |

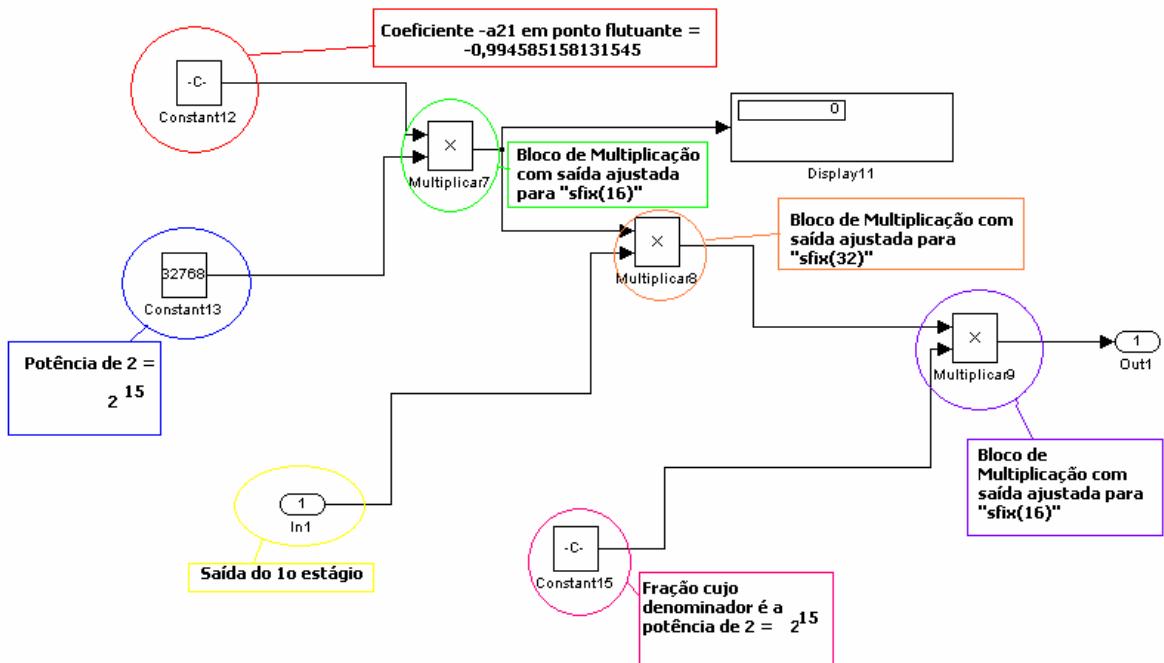

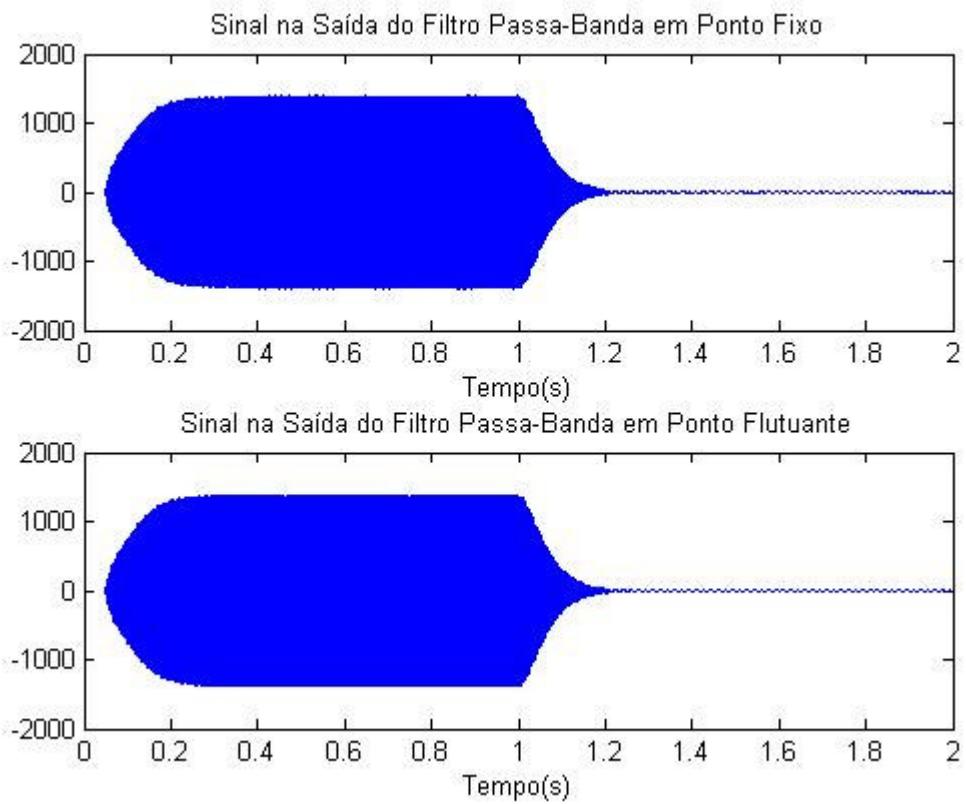

| <i>Figura 33: Os Filtros Passa-Banda Digitais em Ponto Fixo e em Ponto Flutuante.....</i>        | 46 |

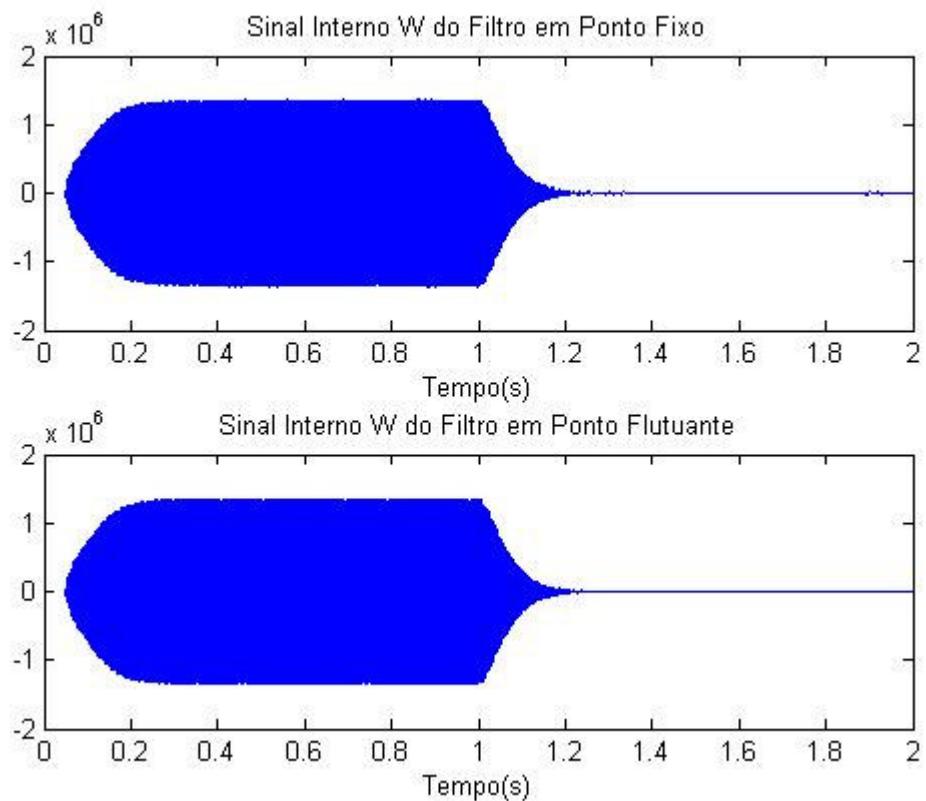

| <i>Figura 34: Sinal Interno <math>W</math>.....</i>                                              | 47 |

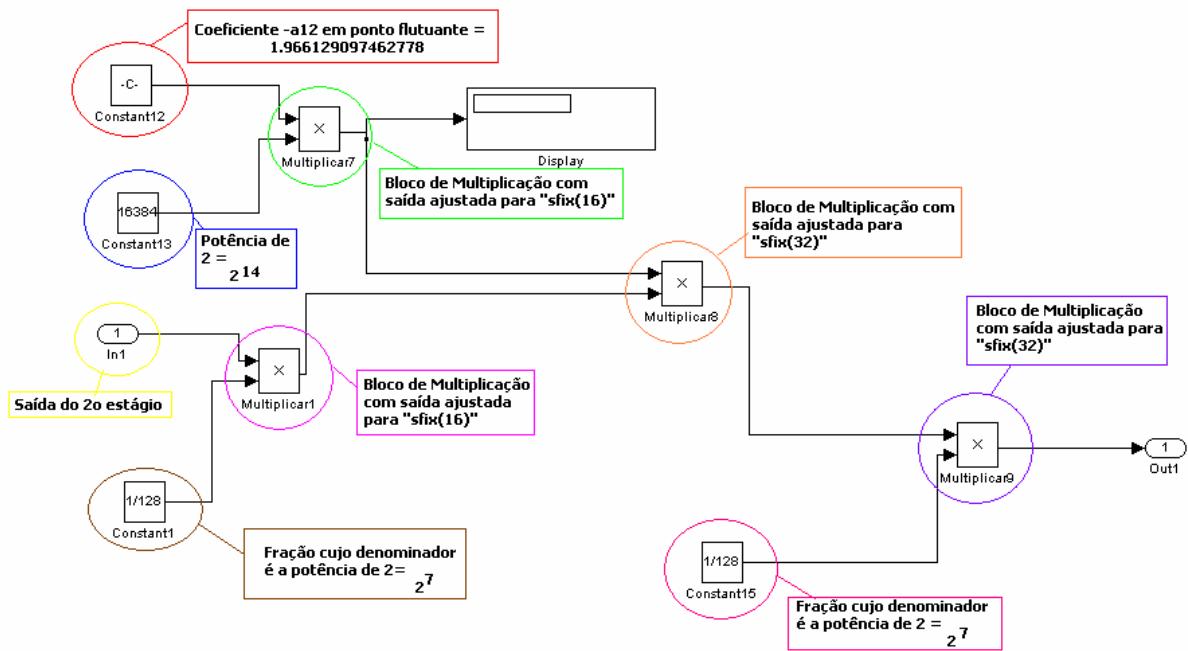

| <i>Figura 35: Interior do Subsistema correspondente ao coeficiente <math>-a_{12}</math>.....</i> | 49 |

| <i>Figura 36: Interior do Subsistema correspondente ao coeficiente <math>-a_{22}</math>.....</i> | 49 |

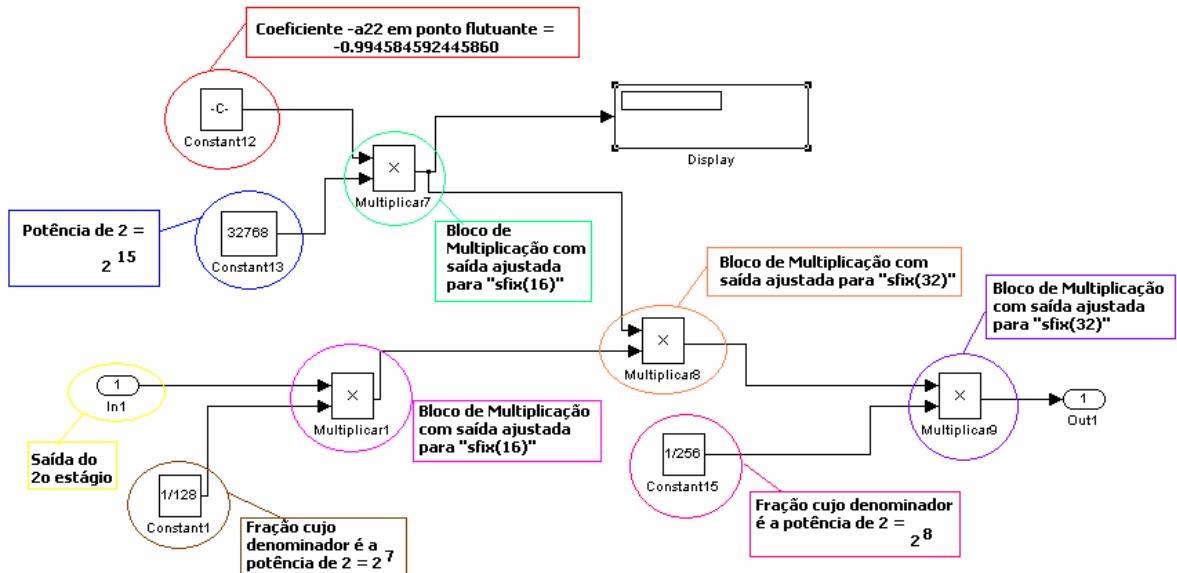

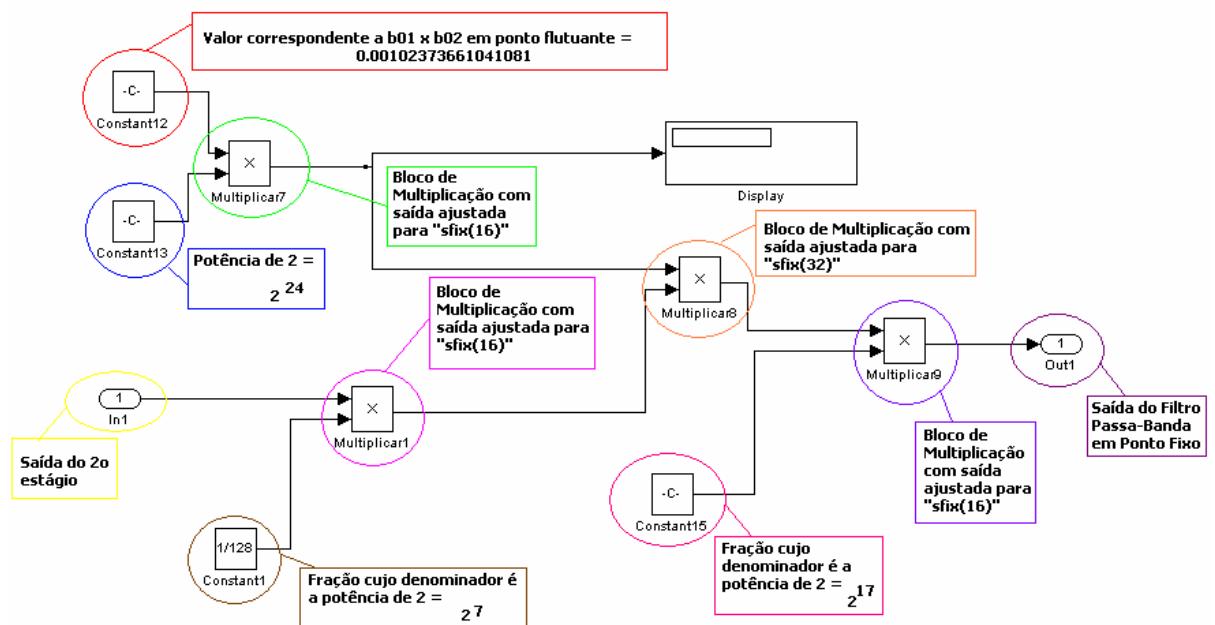

| <i>Figura 37: Interior do Subsistema “<math>b_{01} x b_{02}</math>”.....</i>                     | 50 |

| <i>Figura 38: Saídas dos Filtros Passa-Banda em Ponto Fixo e em Ponto Flutuante.....</i>         | 51 |

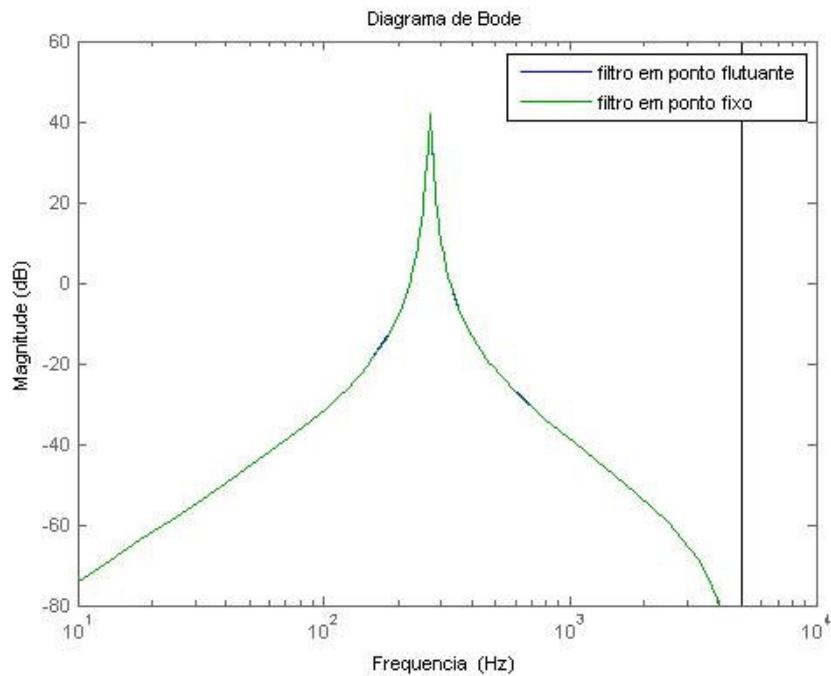

| <i>Figura 39: Respostas em Freqüência dos Filtros em Ponto Flutuante e em Ponto Fixo.....</i>    | 52 |

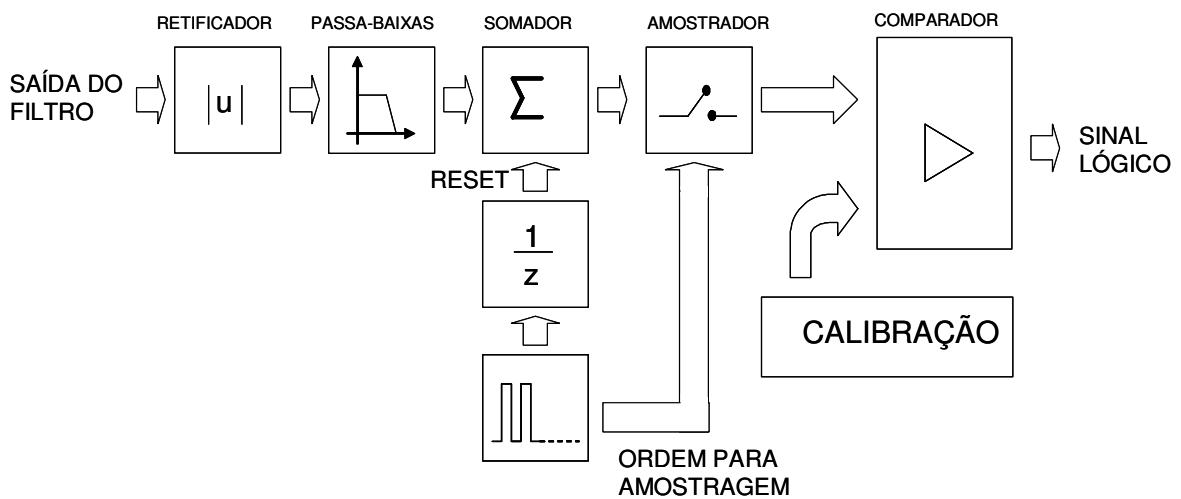

| <i>Figura 40: Diagrama de Blocos do Detector de Amplitude.....</i>                               | 53 |

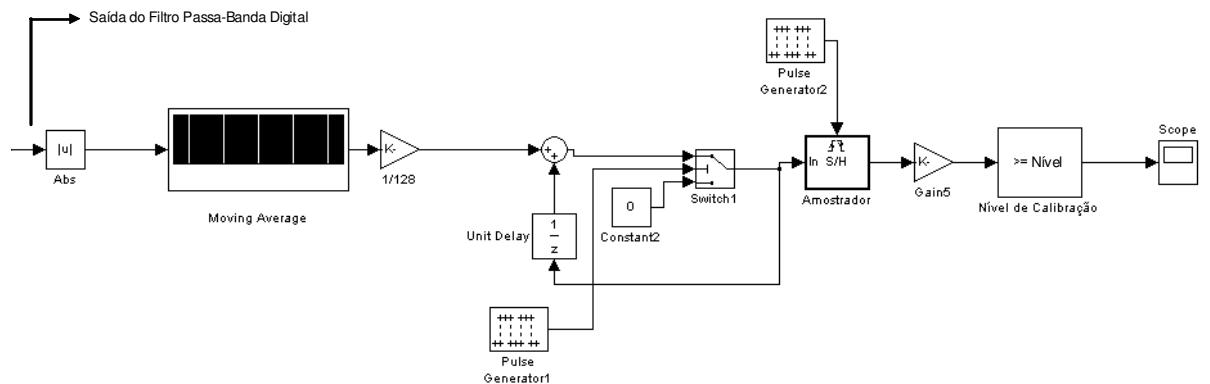

| <i>Figura 41: Esquemático do Detector de Amplitude no Simulink.....</i>                          | 54 |

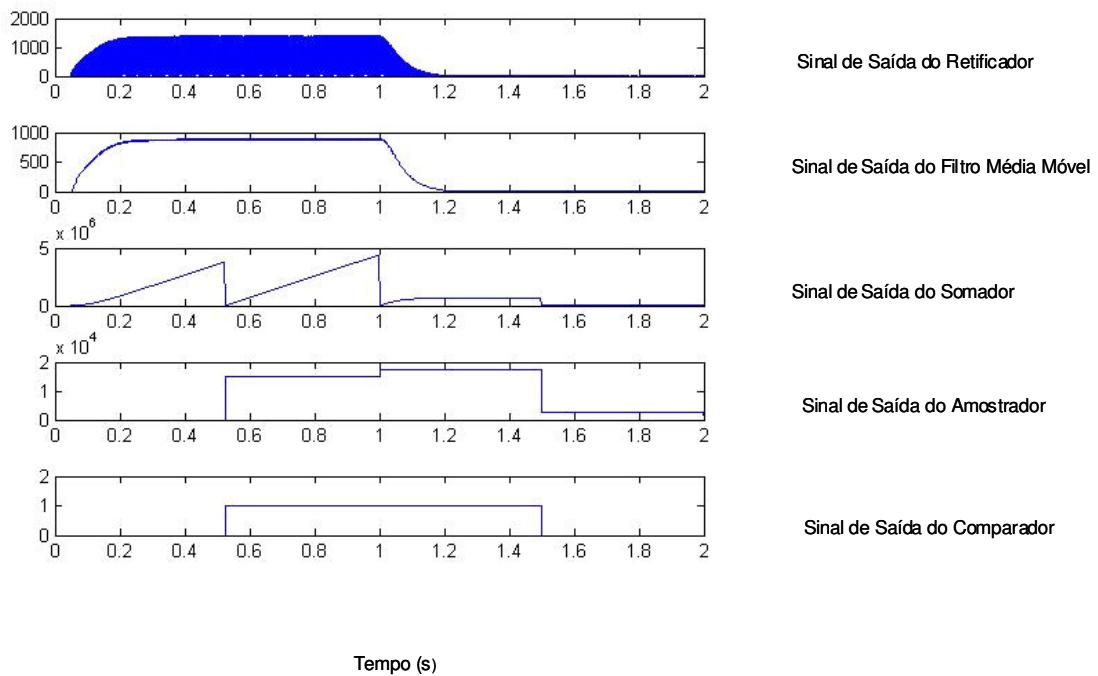

| <i>Figura 42: Sinais de Saída dos Blocos que compõe o Detector de Amplitude.....</i>             | 54 |

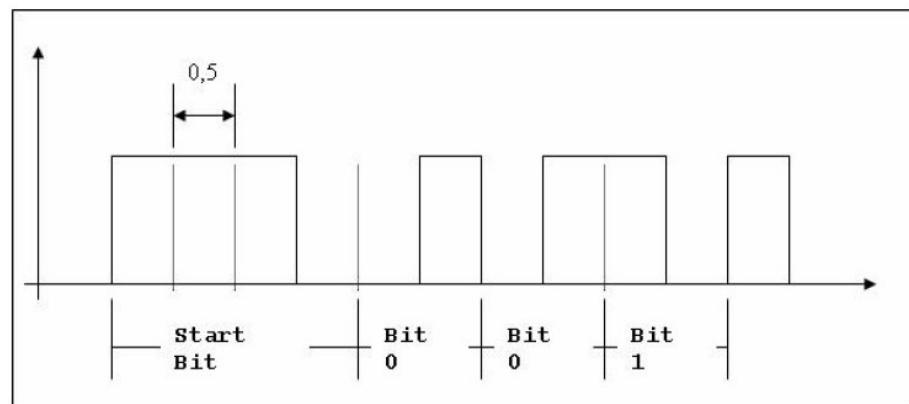

| <i>Figura 43: Protocolo de Comunicação utilizado.....</i>                                        | 55 |

| <i>Figura 44: Bits “Zero” e “Um” de acordo com o Protocolo.....</i>                              | 55 |

| <i>Figura 45: Injeção da Onda Portadora segundo o Protocolo.....</i>                             | 56 |

| <i>Figura 46: Diagrama do Interpretador.....</i>                                                 | 57 |

|                                                                                              |    |

|----------------------------------------------------------------------------------------------|----|

| <i>Figura 47: Algoritmo de Detecção do “Start Bit”.....</i>                                  | 58 |

| <i>Figura 48: Detecção da Informação.....</i>                                                | 59 |

| <i>Figura 49: Sinal Exteriorizado para o Mostrador.....</i>                                  | 59 |

| <i>Figura 50: Rede Elétrica de acordo com a Norma IEC.....</i>                               | 62 |

| <i>Figura 51: Esquemático do Sinal de Entrada para Ensaios com Harmônicos.....</i>           | 63 |

| <i>Figura 52: Sinais do Caso Padrão do Ensaio de Harmônicos e Calibração 10000.....</i>      | 63 |

| <i>Figura 53: Sinais do Caso com Atenuação da Portadora de 50% e Calibração 10000.....</i>   | 64 |

| <i>Figura 54: Sinais do Caso com Atenuação da Portadora de 70% e Calibração 10000.....</i>   | 65 |

| <i>Figura 55: Sinais do Caso com Atenuação da Portadora de 70% e Calibração 5000.....</i>    | 66 |

| <i>Figura 56: Sinais do Caso com Aumento dos Harmônicos e Calibração 5000.....</i>           | 67 |

| <i>Figura 57: Sinais com Aumento dos Harmônicos e Compensação no Conversor AD.....</i>       | 67 |

| <i>Figura 58: Modelo de Rede de Distribuição Implementado em Simulink.....</i>               | 69 |

| <i>Figura 59: Esquemático Simplificado do Ensaio em Transitório.....</i>                     | 71 |

| <i>Figura 60: Sinal na Saída do Filtro Passa-Banda Digital no Ensaio em Transitório.....</i> | 72 |

| <i>Figura 61: Sinais do Caso com Transiente e Calibração 5000.....</i>                       | 72 |

| <i>Figura 62: Sinais do Caso com Transiente e Calibração 4500.....</i>                       | 73 |

# Glossário, Abreviaturas, Siglas e Símbolos

- **ANEEL:** Agência Nacional de Energia Elétrica.

- **ASK:** Amplitude Shift Keying, técnica de modulação de sinais digitais os quais são representados como variações de amplitude da onda portadora.

- **BCD:** Binary Coded Decimal, sistema em que cada dígito decimal é representado por um byte, e no BCD compactado, um dígito decimal é representado por meio byte, utilizando o valor em binário deste dígito.

- **bps:** Bits por segundo, taxa de transferência usada em comunicações do tipo em série (serial) que mede a quantidade de bits que são transferidos por segundo.

- **CEPEL:** Centro de Pesquisa de Engenharia Elétrica, empresa do Grupo Eletrobrás.

- **Checksum:** Uma forma de verificar os dados transmitidos, em um sistema de comunicação, enviando redundância.

- **Conversor AD:** Conversor Analógico-Digital, um dispositivo eletrônico capaz de gerar uma representação digital de uma grandeza analógica.

- **DSP:** Digital Signal Processor ou Processador Digital de Sinais, processador que possui arquiteturas específicas para manipular estruturas típicas de Processamento Digital de Sinais tais como Filtros Digitais, Transformada Rápida de Fourier, multiplicação vetorial, etc.

- **dsPIC:** Um Controlador Digital de Sinais (DSC) da Microchip que consiste em um poderoso dispositivo de 16 bits com arquitetura Harvard modificada, que ao mesmo tempo combina as vantagens de um microcontrolador (MCU) com um Processador Digital de Sinais (DSP).

- **FIR:** Finite Impulse Response, um filtro FIR ou de resposta ao impulso finita é um tipo de filtro digital caracterizado por uma resposta ao impulso que se torna nula após um tempo finito.

- **IEC:** International Electrotechnical Commission ou Comissão Eletrotécnica Internacional é uma organização internacional de padronização de tecnologias elétricas, eletrônicas e relacionadas.

- **IIR:** Infinite Impulse Response, um filtro IIR é um filtro digital com resposta ao impulso de duração infinita.

- **INMETRO:** Instituto Nacional de Metrologia, Normalização e Qualidade Industrial.

- **LCD:** Liquid Crystal Display ou monitor de cristal líquido.

- **MATLAB:** MATrix LABoratory, é um software interativo de alta performance voltado para o cálculo numérico.

- **PLC:** Power Line Communication ou Power Line Carrier é a transmissão de dados utilizando a rede elétrica como meio físico.

- **PLL:** Phase Locked Loop, sistema de controle realimentado que permite a recuperação da onda portadora.

- **Ripple Control:** Técnica de transmissão de dados onde as informações são codificadas através da ausência e presença da onda portadora.

- **ROP:** Receptor de Onda Portadora, dispositivo capaz de recuperar uma onda portadora injetada na rede elétrica.

- **SEMIC:** Sistema Eletrônico de Monitoração Individualizada de Consumos [1], uma patente requerida recentemente pelo CEPEL.

- **Simulink:** Ferramenta de simulação integrada no software MATLAB baseada em diagramas de blocos que permite modelar e analisar sistemas dinâmicos.

- **SMC:** Sistema de Medição Centralizada, uma patente do CEPEL que descreve a topologia de se concentrar medidores de consumo de energia elétrica mantendo a individualização da medição.

- **STC:** Sistema de Telecomando Centralizado, sistema que utiliza uma transmissão de dados unidirecional através da rede elétrica para realizar chaveamento de cargas e controle de tarifas elétricas.

- **TCC:** Terminal de Consulta ao Consumo de energia elétrica de um Sistema de Medição Centralizada.

- **TCCI:** Terminal de Consulta ao Consumo Individual de energia elétrica de um Sistema de Medição Centralizada.

- **TOP:** Transmissor de Onda Portadora, equipamento que injeta, através de um transformador toroidal, sinal no neutro da rede de distribuição elétrica para realizar uma comunicação unidirecional.

# Capítulo 1:

## Introdução

O Centro de Pesquisas de Energia Elétrica (CEPEL) desenvolveu o sistema de medição centralizada (SMC) com o objetivo de aperfeiçoar o processo de medição do consumo de energia elétrica possibilitando a leitura eletrônica automática desses dados por parte das concessionárias. O conceito introduzido pelos pesquisadores do Centro tem como base o agrupamento de medidores ou módulos de medição em caixas coletivas possibilitando o compartilhamento de algumas funções inerentes aos medidores eletrônicos, mas mantendo a individualização do cálculo do consumo de energia.

Estas caixas podem ser instaladas em locais convenientes à concessionária, tanto no interior de edifícios quanto nos postes da rede de distribuição em local inacessível ao consumidor. Assim, com o surgimento do SMC, a aparência dos equipamentos de medição foi bastante alterada conferindo-lhes maior proteção contra fraudes e vandalismo devido, sobretudo, ao distanciamento do medidor de possíveis ações humanas.

Tradicionalmente, os medidores localizam-se ou no interior da unidade consumidora ou em lugar limítrofe entre a casa do consumidor e a rua (normalmente no muro) possuindo cada um a sua caixa própria, individualizada e o consumidor pode acompanhar seu consumo no visor. Com o SMC, para que este paradigma permaneça, é necessário viabilizar meios que permitam ao consumidor visualizar a informação do seu consumo.

Isso pode ser feito através de “hot-line”, “sms”, e-mail, “pagers”, telefone, etc. e já foi posto em prática pela empresa AMPLA Energia e Serviços S.A. no estado do Rio de Janeiro. Entretanto, a experiência tem demonstrado que os consumidores não aderiram à utilização destes métodos preferindo o uso do equipamento conhecido como Terminal de Consulta ao Consumo (TCC) que também pode ser oferecido pelos SMCs. Esse terminal pode ser coletivo (TCCC), normalmente instalado no poste do transformador de distribuição, ou individual (TCCI), instalado na unidade consumidora.

A utilização de TCCs coletivos, apesar de apresentar a vantagem de um custo mais baixo quando comparado ao somatório de TCCs individuais necessários para atender ao mesmo número de consumidores, tem sofrido com ações depredatórias uma vez que os

TCCCs têm que ser instalados em lugar público e de fácil acesso. Além disso, os TCCCs trazem uma dificuldade adicional para o consumidor, na medida em que para que seja realizada a leitura é necessário o deslocamento dos consumidores a locais que ficam afastados da sua própria unidade consumidora.

Com o objetivo de regulamentar o sistema de medição centralizada e conferir ao consumidor o direito de acompanhar o seu consumo de energia em sua própria residência, a ANEEL (Agência Nacional de Energia Elétrica), através da Resolução nº 923 de 2007, e o INMETRO (Instituto Nacional de Metrologia, Normalização e Qualidade Industrial), por meio da Portaria nº 150 de 21 de Junho de 2006, requerem a instalação dos terminais de consulta ao consumo individuais (TCCI) nas unidades consumidoras. Deste modo, para a implantação e utilização do SMC em sua plenitude, torna-se necessária a busca de uma solução técnica economicamente viável e de alta confiabilidade para a implementação dos TCCIs.

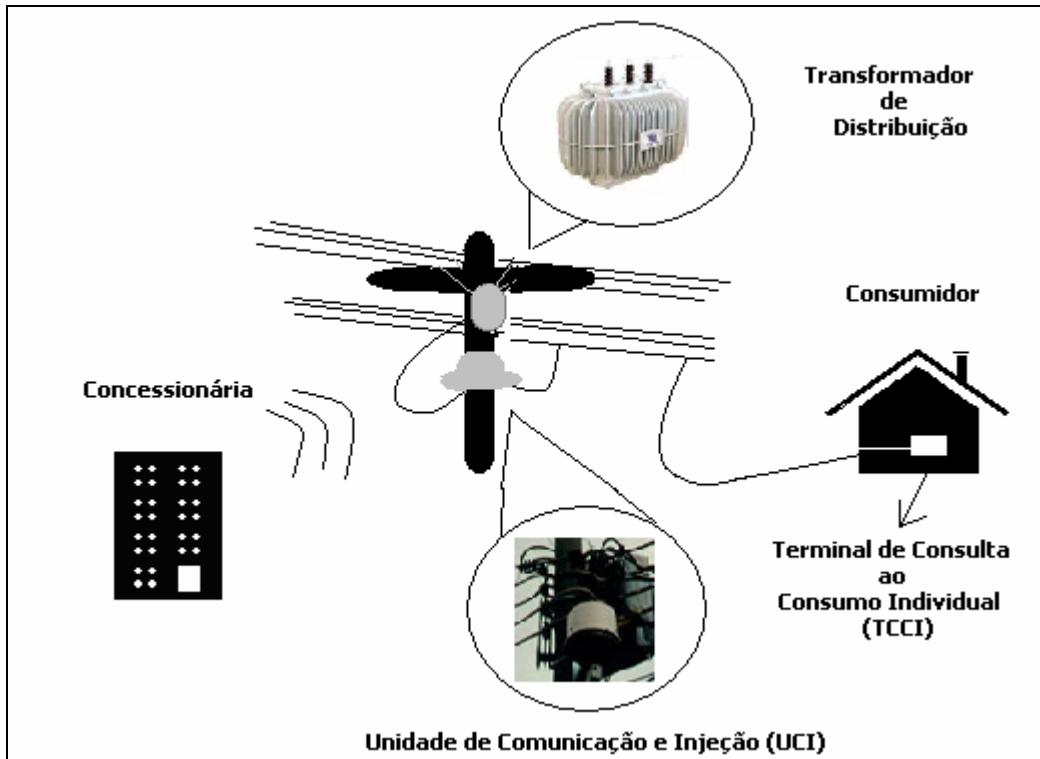

Neste sentido, o CEPEL requereu a patente do Sistema Eletrônico para Monitoração Individualizada de Consumos (SEMIC) [1]. O objetivo básico do projeto é prover um canal de comunicação para a transmissão de informações de uma concessionária de energia elétrica para o consumidor, principalmente, o consumo de energia. O SEMIC é composto por uma unidade de comunicação e injeção (UCI) que é instalada no poste junto ao transformador de distribuição e pelos terminais de consulta ao consumo individual (TCCI) presente nas unidades consumidoras, conforme ilustrado na figura 1.

Figura 1: Canal de Comunicação entre Concessionária e Consumidor.

A UCI possui um circuito de interfaceamento com o sistema de medição centralizada (SMC) da concessionária que pode se dar através de comunicação local, com o circuito correspondente no SMC, ou através de comunicação sem-fio via rádio (UHF, por exemplo) ou outro sistema de comunicação sem fio qualquer (GSM/GPRS, por exemplo). O Transmissor de Onda Portadora (TOP) é o responsável pela injeção do sinal correspondente à informação na rede de distribuição que será propagado atingindo todos os consumidores conectados à mesma. Um módulo de controle gerencia o circuito de interfaceamento e o transmissor de onda portadora.

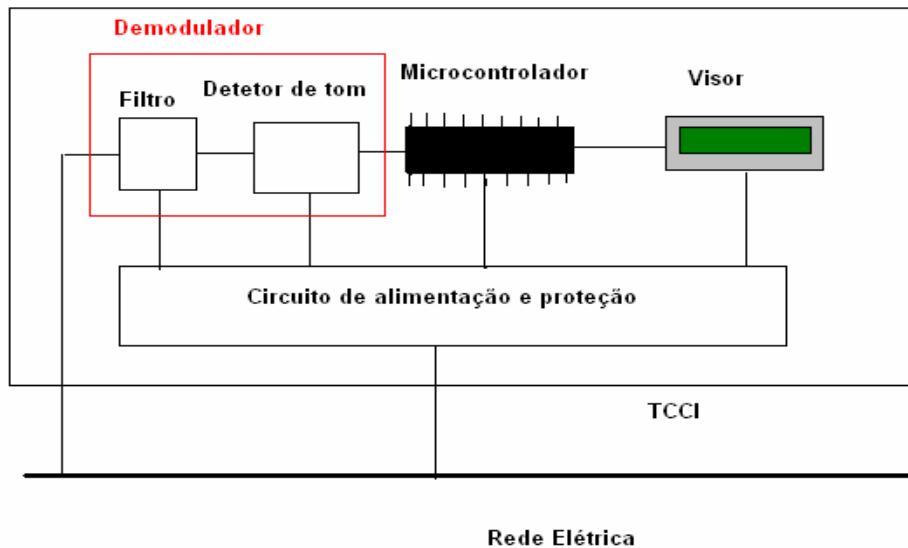

O TCCI é um dispositivo que possui um demodulador, um microcontrolador, que interpreta o sinal de saída deste demodulador, e um visor. Assim, ao ser conectado a uma tomada, este equipamento deve ser capaz de filtrar a onda portadora injetada na rede pelo TOP, processar a mesma identificando as informações ali presentes, e apresentá-las em um LCD. A figura 2 apresenta o diagrama do TCCI.

Figura 2: Terminal de Consulta ao Consumo Individual (TCCI).

Esse sistema híbrido de comunicação entre concessionária e consumidor é composto por dois enlaces: o primeiro utilizando a comunicação sem-fio e o segundo utilizando as linhas de distribuição de baixa tensão, foi baseado em outro projeto do CEPEL denominado Sistema de Telecomando Centralizado (STC) [2].

No projeto previamente mencionado, foi desenvolvido o Transmissor de Onda Portadora (TOP) que injetava a onda portadora no neutro da rede de distribuição atingindo assim todos os consumidores ligados a ela e o Receptor de Onda Portadora (ROP) capaz de filtrar, interpretar a informação e, a partir desta, realizar chaveamento e desligamento de cargas (receptores instalados junto às cargas a serem chaveadas) e controle de tarifa (receptores instalados dentro dos medidores) objetivando aplinar as curvas de carga e tornar o sistema mais equilibrado.

Os princípios desta comunicação PLC (“Power Line Communication” ou “Power Line Carrier”) são aproveitados no SEMIC. A injeção de sinal é feita no neutro, a freqüência da onda portadora é baixa (cerca de centenas de Hz) e está situada entre as freqüências dos harmônicos de 60Hz e sua modulação é do tipo “Ripple Control”, isto é, os bits são definidos pela presença e ausência da portadora. Pelo fato de usar baixas freqüências onde a atenuação da rede é menor, essa modulação é robusta garantindo a confiabilidade necessária a um sistema de medição de consumo utilizado para tarifação de clientes, possuindo, em contra partida, uma taxa de transmissão considerada baixa (cerca de 0,5 bit/s). Esse aspecto negativo

não é muito sentido nesse caso já que o consumidor provavelmente não precisará da informação de seu consumo atualizada em tempo real (vide Apêndice A [3]).

Com isso, a estrutura do demodulador do ROP pôde ser aproveitada no TCCI consistindo basicamente de um filtro passa-banda sintonizado na freqüência da portadora e de um detector de tom (PLL), ambos analógicos sendo que este último é implementado usando o CI 567.

## 1.1 Objetivo

O objetivo do presente trabalho é propor e estudar um modelo de demodulador digital para o Terminal de Consulta ao Consumo Individual (TCCI) do Sistema Eletrônico de Monitoração Individualizada de Consumo (SEMIC) visando sua futura implementação em DSP (*Digital Signal Processor*).

O projeto é todo baseado em simulações feitas com o auxílio da ferramenta “Simulink” do software matemático “MATLAB” [4]. Através dela, foi proposto um algoritmo de detecção da onda portadora e para isso, foram utilizadas operações facilmente implementáveis em dispositivos do tipo DSP.

Tendo definido a arquitetura do demodulador, foram realizados testes para a avaliação de seu desempenho em relação a dois principais problemas que na prática poderiam afetar o bom funcionamento do sistema. São eles: harmônicos e transitórios ambos existentes na rede elétrica. Visa-se, com isso, verificar a validade e robustez do modelo proposto.

Além disso, o fato de o TCCI ter sua aplicação direcionada aos consumidores de baixa tensão faz com que se tenha um volume muito grande de unidades a serem instaladas. Assim, o objetivo é que a solução apresente não só alta confiabilidade, mas também um baixo custo. Nesse sentido, este trabalho foi desenvolvido em ponto fixo visando o seu uso em processadores menos complexos e normalmente menos dispendiosos.

Com isso, pretende-se também, de posse da solução a ser adotada, da arquitetura, dos parâmetros e das condições de contorno, verificar o tipo de DSP mais adequado com relação à capacidade de processamento necessária para a implementação do modelo proposto no “MATLAB”.

## 1.2 Organização do Trabalho

O texto deste trabalho está dividido em quatro capítulos e dois apêndices. O primeiro é uma introdução ao contexto do trabalho e expõe também seus objetivos.

O Capítulo 2 detalha as especificações de projeto e explica o algoritmo desenvolvido no “Simulink” para detecção da onda portadora dando ênfase à questão da aritmética em ponto fixo.

O terceiro capítulo é destinado às simulações considerando o sistema em estado de regime permanente e em transitório. Os resultados são analisados e as condições de contorno são estabelecidas.

Por fim, o Capítulo 4 conclui o projeto apresentando a arquitetura definitiva do demodulador, ou seja, aquela capaz de atender às especificações de maneira satisfatória considerando os problemas causados tanto pelos harmônicos quanto pelos transitórios da rede elétrica, além de apontar um dispositivo do tipo DSP ou dsPIC que se adequaria à implementação prática e as perspectivas futuras para o projeto.

O apêndice A apresenta o cálculo do valor da taxa de transmissão e o apêndice B corresponde ao “script” do MATLAB utilizado nas simulações.

## Capítulo 2:

# O Demodulador Digital do TCCI

O demodulador do TCCI corresponde ao circuito que, uma vez conectado a uma tomada da casa do consumidor, é capaz de extrair o sinal injetado na rede elétrica pelo TOP sendo este último instalado no poste próximo ao transformador de distribuição.

A versão digital do demodulador proposta aqui se trata de um aperfeiçoamento daquele desenvolvido analogicamente para o Receptor de Onda Portadora (ROP) em trabalhos anteriores [2][5]. Isso pode ser feito porque, como já foi mencionado, a comunicação PLC utilizada para enviar a leitura do consumo para o TCCI se baseia naquela usada no Sistema de Telecomando Centralizado (STC) para mandar informações de chaveamento de carga e controle de tarifa. Assim, as características e especificações de projeto são as mesmas e estão detalhadas na seção seguinte.

## 2.1. Características e Especificações do Projeto

### 2.1.1 Modulação do Sinal Injetado

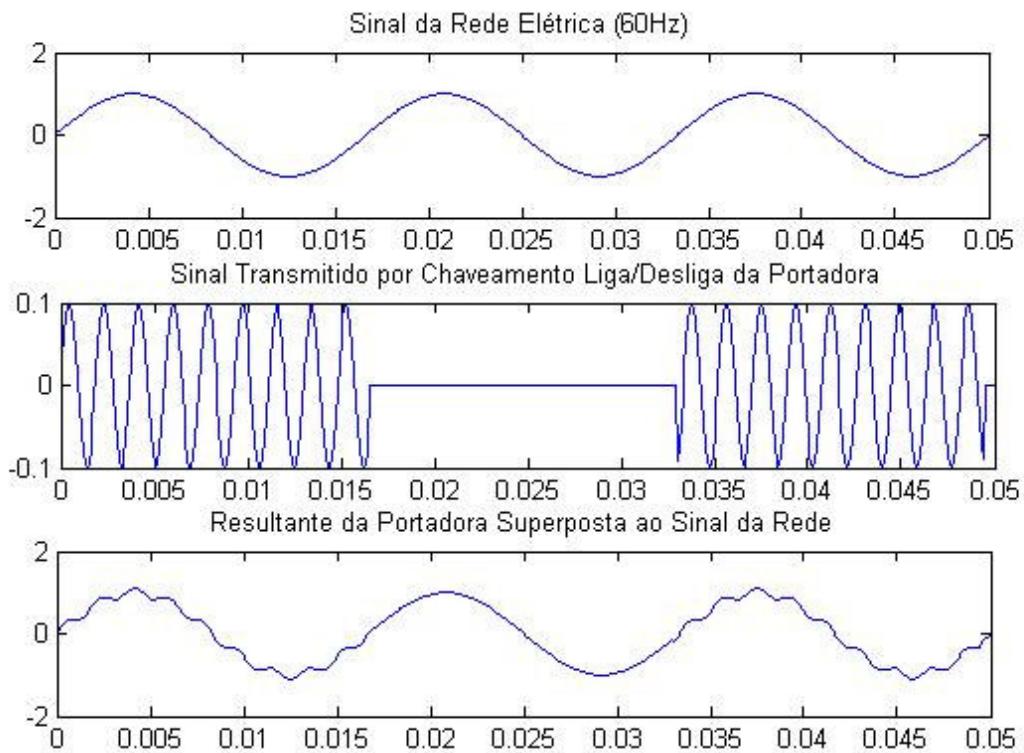

O tipo de modulação utilizada na comunicação PLC abordada é o “Ripple Control” que tem como características principais o uso de freqüências inferiores a 1 KHz e a codificação em ASK (Amplitude-Shift Keying) [6], ou seja, ligando e desligando a injeção da onda portadora como mostra a figura 3.

Figura 3: Modulação ‘Ripple Control’.

Como as freqüências estão próximas ao 60Hz, se propagam através da linha e dos transformadores com bastante eficiência. Entretanto, nesta faixa de freqüências ocorre forte presença de harmônicos da rede, sendo necessário posicionar a freqüência da portadora entre estes harmônicos. Por esta razão, sistemas ‘RC’ (Ripple Control) estão fortemente sujeitos a ruídos.

Outras características relevantes para o projeto são: a baixa taxa de transmissão devido às baixas freqüências da portadora e a limitação a aplicações unidirecionais, uma vez que o retorno é dificultado pela necessidade de potência. Portanto, a comunicação utilizada é unidirecional e a princípio considera-se apropriada uma taxa de transmissão de 1 bps (bit por segundo).

### 2.1.2 Sinal Injetado

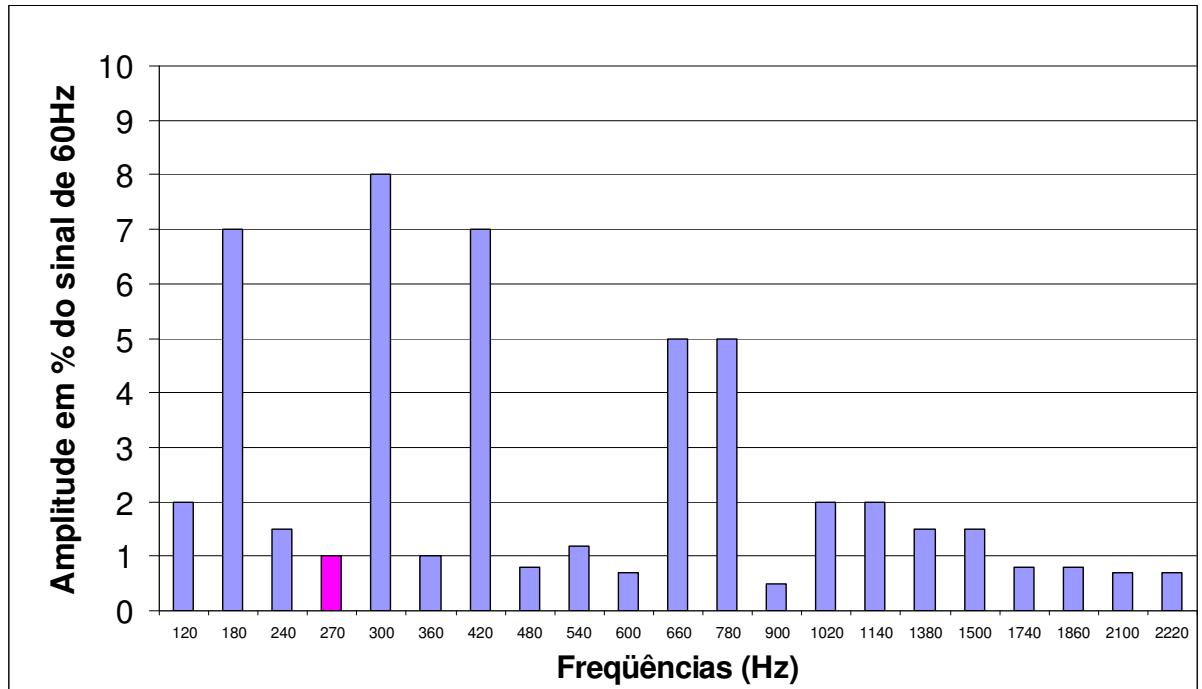

O sinal injetado no neutro, devido às características do TOP usado na referência [2], tem amplitude igual a 1% da amplitude da tensão da rede. Da norma nº62054-11 para receptores de telecomando aplicados a sistemas de ‘Ripple Control’ de Maio de 2004 elaborada pela IEC (International Eletrotechnical Commision) [7] se extraiu os níveis dos

harmônicos em relação à fundamental de 60Hz considerados no desenvolvimento deste projeto.

Assim, o sinal injetado pelo transmissor de onda portadora na freqüência determinada é uma onda quadrada cuja amplitude é de 1,79V para uma tensão de 127V eficazes. Como a componente fundamental de uma onda quadrada apresenta o fator  $4/\pi$  como multiplicador de sua amplitude, também se pode considerar o sinal injetado como uma senóide de amplitude 1,27% da tensão da rede.

A escolha da freqüência da portadora foi baseada em simulações do modelo da rede de distribuição de baixa tensão e testes de campo realizados em trabalhos anteriores [2][8]. Na ocasião, verificou-se a boa propagação de freqüências de até 300Hz (atenuação menor que 3dB). Nesta região de interesse, optou-se pela freqüência de 270Hz que está centrada entre os harmônicos 240Hz (4º) e 300Hz (5º). Outras freqüências podem ser usadas como, por exemplo, a freqüência de 510Hz. Estes estudos deverão ser realizados em trabalhos futuros.

O gráfico do espectro de freqüência da rede elétrica segundo a norma da IEC [7], junto com a onda portadora injetada pelo TOP, é mostrado na figura 4.

Figura 4: Espectro de Freqüência de acordo com a Norma da IEC.

## 2.2 Modelo Proposto

O modelo proposto em “MATLAB” para o demodulador do TCCI deve ser capaz de recuperar a onda portadora descrita anteriormente distinguindo sua presença e sua ausência de maneira confiável.

O demodulador apresentado neste trabalho está parcialmente baseado no projeto do Receptor de Onda Portadora (ROP) do STC [2][5] e aproveita o seu conceito. Ilustra-se a seguir o esquema desenvolvido no trabalho base (figura 5). É um projeto completamente analógico, a menos do interpretador. O atenuador de entrada do ROP é responsável pela redução da amplitude do sinal de 60Hz de forma a atender os requisitos de entrada do filtro passa-banda. Este poderia ser melhor definido como filtro com amplificador, pois além de atenuar o sinal da fundamental (60Hz) e seus harmônicos, dá um ganho na freqüência da onda portadora de 270Hz. Os parâmetros do filtro foram calculados visando atender às especificações de relação sinal-ruído na entrada do detector de tom baseado em PLL (CI 567) utilizado para a recuperação da portadora após a filtragem. Finalmente o interpretador recebe sinal serializado digital e verifica sua coerência e o processa.

Figura 5: Diagrama de Blocos do Receptor de Onda Portadora do STC.

No caso do presente trabalho, manter-se-á o conceito do atenuador. Contudo, são incluídos os blocos do filtro “antialiasing”, o conversor AD (Analógico/Digital), o detector de amplitude e o bloco de adequação do sinal. A PLL não é utilizada, sendo substituída pelos dois últimos elementos mencionados. O diagrama de blocos do demodulador proposto pode ser observado na Figura 6 e os blocos que o compõe serão detalhados nas próximas subseções.

Figura 6: Diagrama de Blocos do Demodulador do TCCI.

### 2.2.1 Atenuador de Entrada

O atenuador de entrada do TCCI é responsável pela redução da amplitude do sinal de 60Hz de forma a possibilitar o processamento dos sinais em baixa amplitude. Este circuito, como já mencionado anteriormente, foi desenvolvido para o receptor de onda portadora (ROP) do STC [2][5] e o seu conceito foi aproveitado no presente trabalho.

Para o projeto base, estipulou-se como amplitude para a tensão de saída do atenuador cerca de  $500 \text{ mV}_{\text{rms}}$ . Com isso, o circuito atenuador obtido correspondia a uma atenuação de 50dB. Decidiu-se para o presente projeto adotar os mesmos valores de atenuação, o que implica que a tensão de entrada do conversor AD teria cerca de 0,7V de pico. Isto corresponde a uma tensão eficaz de 156V, o que representa uma margem de segurança de 23% acima da tensão nominal da rede, de 127V.

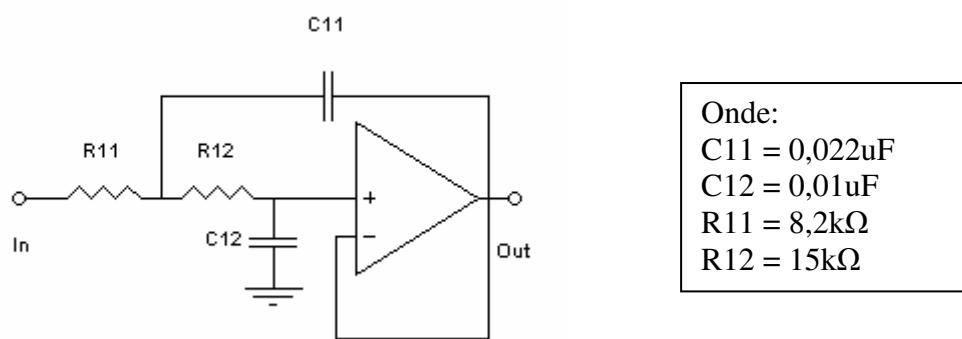

O circuito e sua resposta em freqüência são mostrados nas figuras a seguir. No “Simulink”, o atenuador é representado pelo bloco contendo sua função de transferência apresentado na figura 8.

Figura 7: Circuito Atenuador.

Figura 8: Resposta em Freqüência do Circuito Atenuador.

Figura 9: Representação do Circuito Atenuador no Simulink.

### 2.2.2 Filtro Anti-Aliasing

No processo de digitalização do sinal de entrada do demodulador, é necessário levar em consideração o Teorema de Nyquist. De acordo com Nyquist, a quantidade de amostras por unidade de tempo de um sinal, chamada taxa ou freqüência de amostragem, deve ser maior que o dobro da maior freqüência contida no sinal a ser amostrado, para que possa ser reproduzido integralmente sem erro de “aliasing”. Assim, a metade da freqüência de amostragem é chamada freqüência de Nyquist e corresponde ao limite máximo de freqüência do sinal que pode ser reproduzido. Como na prática não é possível garantir que o sinal não contenha componentes acima do limite estabelecido por Nyquist (distorções, interferências,

ruídos, outras comunicações PLC, etc...), é necessário filtrar o sinal com um filtro passa baixas com freqüência de corte igual (ou menor) à freqüência de Nyquist, ou filtro anti-aliasing.

Para este projeto, adotou-se uma freqüência de amostragem de 10kHz porque julgou-se a mesma suficiente para a implementação em DSP. A princípio, segundo Nyquist, poder-se-ia ajustar a freqüência de corte do filtro anti-aliasing para 5kHz. Entretanto, optou-se por uma freqüência de corte de 1kHz para não só evitar o aliasing devido a freqüências superiores a 5kHz, como também para atenuar possíveis harmônicos acima de 1kHz. Os harmônicos abaixo de 1kHz têm sua amplitude reduzida através do filtro passa-banda digital.

O filtro anti-aliasing utilizado no projeto foi desenvolvido no software FilterLab disponibilizado pela empresa Microchip em seu site [9]. Trata-se de um filtro passa-baixas ativo de 2<sup>a</sup> ordem com ganho na banda de passagem de aproximadamente 1 V/V. O circuito, sua resposta em freqüência e sua representação no “Simulink” (feita através do bloco “Analog Filter Design”) são apresentados nas figuras que se seguem. Outras opções para o filtro anti-aliasing deverão ser avaliadas em trabalhos futuros.

Figura 10: Circuito do Filtro Anti-Aliasing.

Figura 11: Resposta em Freqüência do Filtro Anti-Aliasing.

Figura 12: Representação do Filtro Anti-Aliasing no Simulink.

### 2.2.3 Amostrador e Conversor AD (Analógico/Digital)

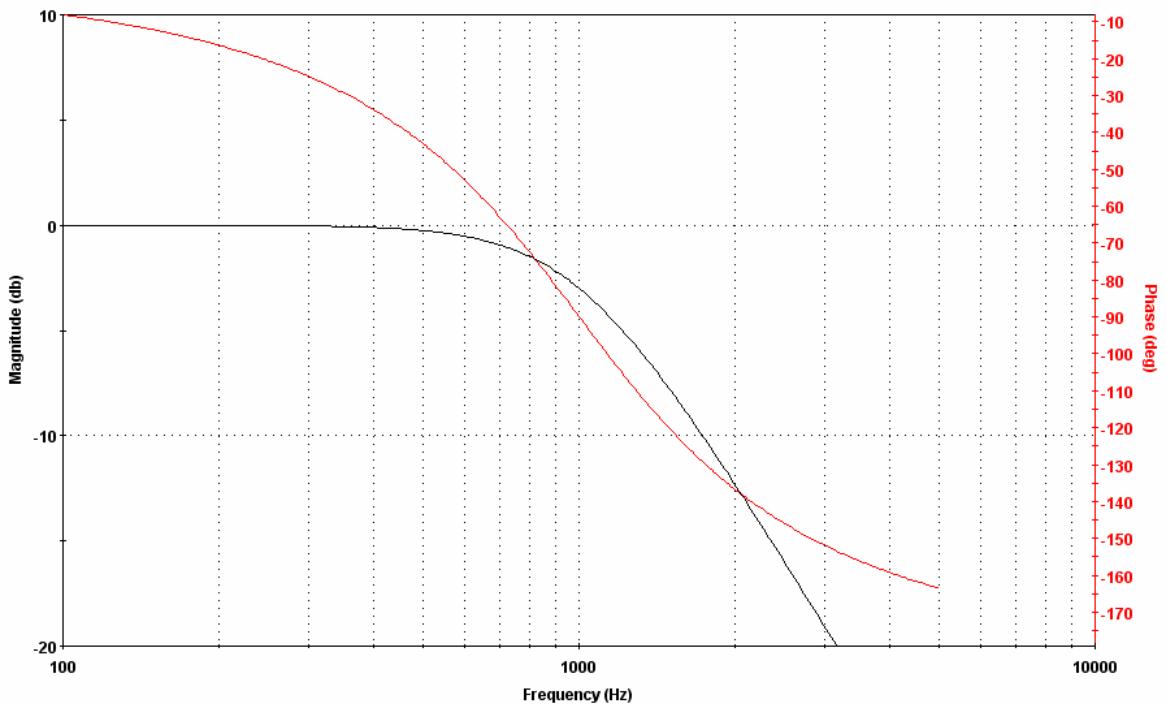

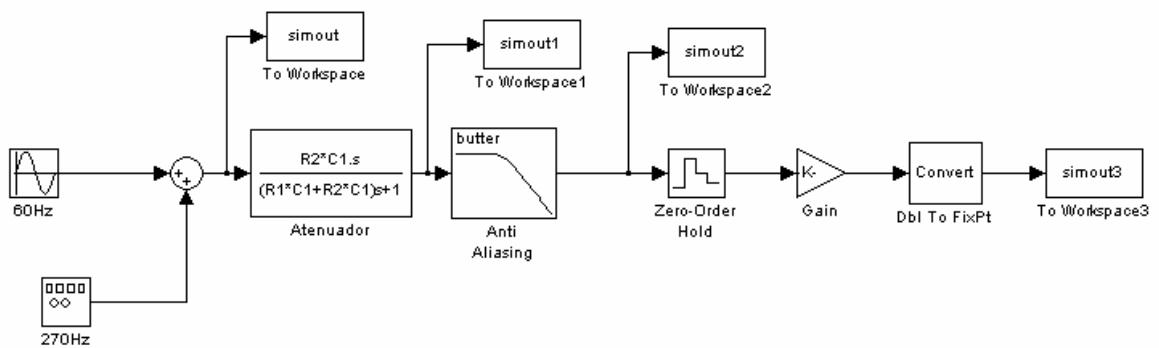

O conjunto de blocos utilizado para modelar o amostrador e o conversor AD do DSP está ilustrado na figura a seguir. Pretende-se, em uma futura implementação prática, usar um conversor AD com fundo de escala definido através de referências de tensão e com uma palavra binária na sua saída de 12 bits. Assume-se que o conversor AD apresentará a palavra binária na sua saída em complemento de dois.

Conversor AD

Figura 13: Representação do Conversor AD no Simulink.

O “Zero-Order Hold” é o responsável pela amostragem do sinal de entrada a uma taxa de 10kHz. Para demonstrar o funcionamento deste bloco, apresenta-se na figura 14 seus sinais de entrada e saída, considerando uma situação hipotética onde um sinal de 60 Hz é amostrado a uma taxa de 600Hz. É importante destacar que, no MATLAB, o bloco “Zero-Order Hold” ainda não quantiza o sinal de entrada, ele apenas amostra e mantém o valor aquisitado até realizar nova aquisição sendo sua saída composta de números em formato de ponto flutuante.

Figura 14: Exemplo de funcionamento do “Zero-Order Hold”.

O bloco de ganho ajusta o fundo de escala do conversor AD. O valor do ganho está relacionado ao fundo de escala utilizado e também à máxima palavra binária do conversor,

como será explicado mais adiante. Este bloco de ganho é parte do processo de conversão dos sinais analógicos em sinais digitais não representando, portanto, uma amplificação propriamente dita.

E, por fim, o “Convert” converte os valores das amostras do sinal de ponto flutuante para seus valores correspondentes em ponto fixo no formato inteiro sinalizado (“signed integer”) com 12 bits, simulando assim o conversor AD de 12 bits.

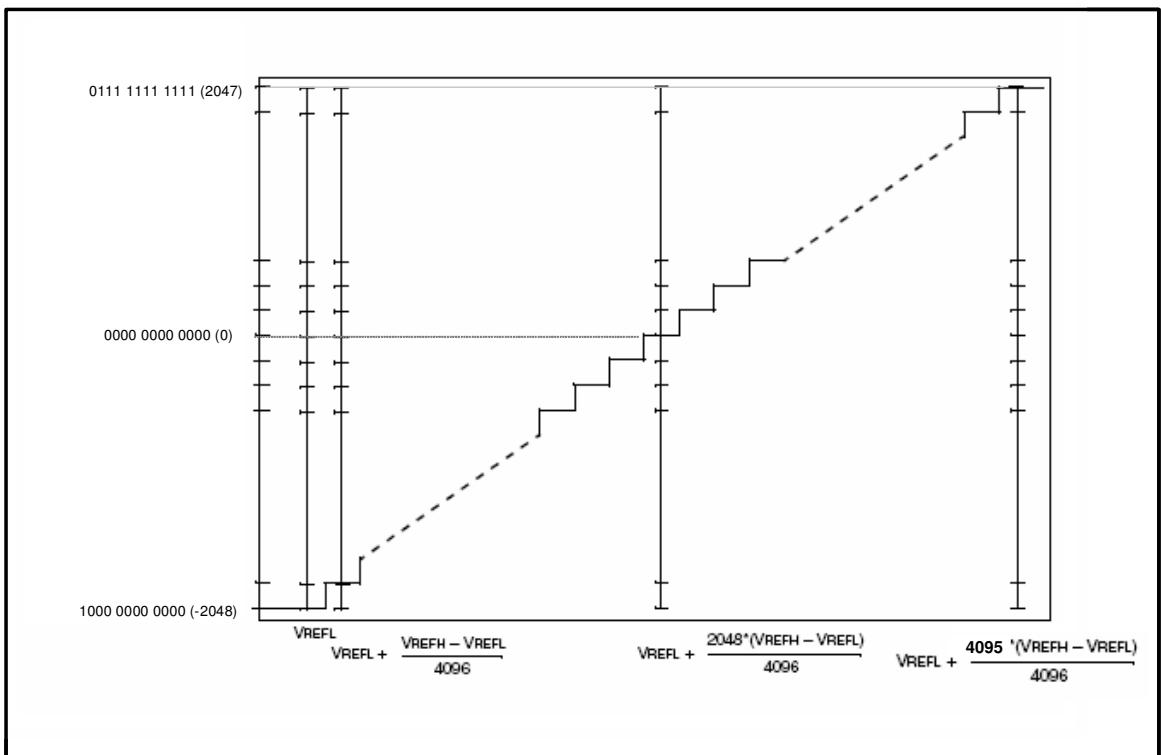

Para este trabalho, assumir-se-á um conversor AD onde valores de sinal entre dois níveis consecutivos de quantização são aproximados para o nível mais próximo. A figura 15 apresenta a função de transferência do conversor que será simulado usando-se esse conceito de arredondamento. Ela também destaca a presença dos limites do fundo de escala do AD representados por  $V_{REFL}$  (limite inferior) e  $V_{REFH}$  (limite superior) que podem ser definidos através dos pinos do CI (círculo integrado) do DSP que será usado na implementação futura do algoritmo. A tensão na entrada do conversor poderá excursionar entre  $V_{REFL}$  e  $V_{REFH}$  que, para este trabalho, serão considerados iguais em módulo.

Como as amostras são números inteiros sinalizados e o AD considerado é de 12 bits, na representação de complemento de dois, o bit mais à esquerda é utilizado para representar o sinal e onze bits são utilizados para a magnitude do sinal. Assim, são  $2^{12}$  (4096) níveis de quantização, sendo que os números positivos são representados de 0 a 2047 e os números negativos de -1 a -2048 como indicado na figura a seguir.

Figura 15: Função de Transferência do Conversor AD.

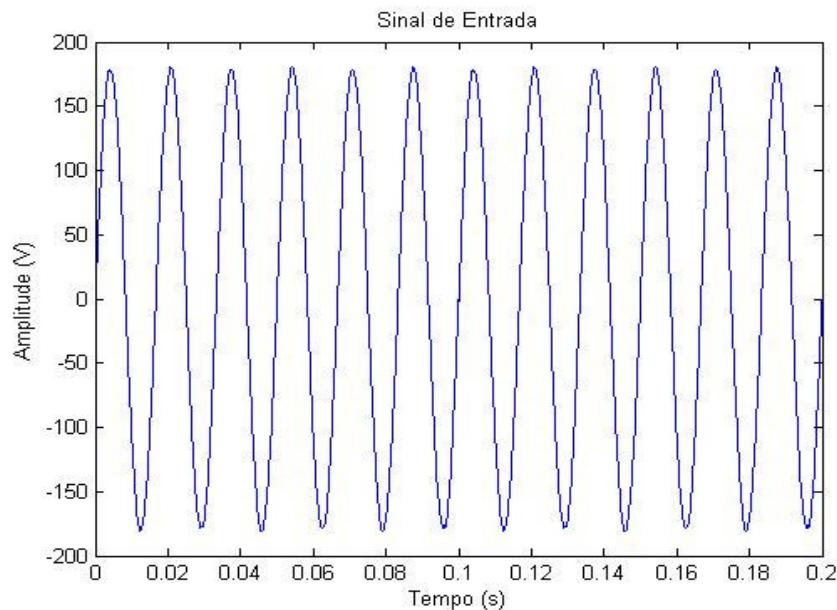

Para exemplificar o funcionamento do bloco amostrador e conversor AD, é apresentada uma simulação preliminar (figura 16) cujo sinal de entrada (figura 17) é composto por uma superposição da fundamental (60Hz) e de uma onda quadrada de 270Hz. O nível de sinal da portadora corresponde a 1% do nível do sinal da rede como já mencionado na subseção 2.2.2. Em trabalhos anteriores [2][8], foram feitos testes em campo e simulações que comprovaram que a onda portadora sofre uma atenuação máxima de 3 dB devido a perdas na linha de distribuição entre o transmissor de onda portadora (TOP) e o receptor. Assim, o nível da onda quadrada que no “Simulink” corresponde à onda portadora de 270Hz é igual a 1% do nível da fundamental acrescido desta atenuação de 3dB.

Figura 16: Esquemático da Simulação em “Simulink”.

Observa-se que não se nota visualmente o sinal de 270Hz uma vez que ele é muito menor que o sinal de 60Hz.

Figura 17: Sinal de Entrada Composto pela Superposição

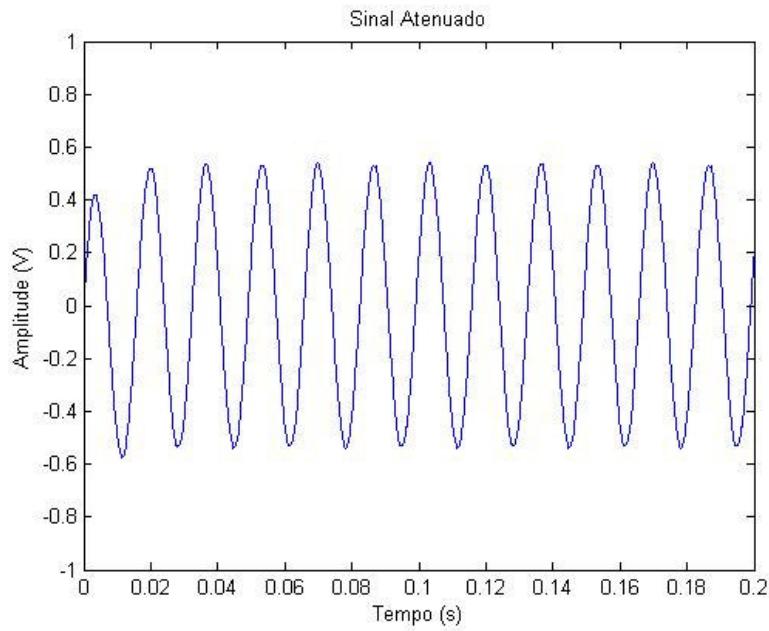

Esse sinal de entrada é atenuado, passa pelo filtro anti-aliasing e é amostrado no “Zero-Order-Hold” e quantizado no conversor AD. A figura 18 apresenta o sinal de saída do atenuador.

Figura 18: Sinal na Saída do Atenuador.

Como já esperado, o sinal na saída do atenuador possui, no máximo, 0,7V de pico o que corresponde a  $500V_{rms}$ . Ao ser filtrado, este sinal permanece inalterado uma vez que é composto por freqüências (60Hz e 270Hz) localizadas dentro da banda passante do filtro anti-aliasing e têm um ganho de 0 dB. Assim, este também é o sinal na entrada do conversor AD. Considerando a faixa de excursão do mesmo, optou-se por um fundo de escala de 1V. Logo, para conseguir-se que o limite inferior de -1V seja representado por -2048 e o limite superior de 1V por 2048, deve-se multiplicar o sinal de entrada por  $(2048/1=2048)$ . Este é o valor escolhido para o ganho K do bloco de ganho. O bloco “Convert” limita o nível superior a 2047 completando o ajuste da escala do conversor AD. Além disso, o bloco “Convert” quantiza o valor de forma a reproduzir o que o conversor AD faria na prática.

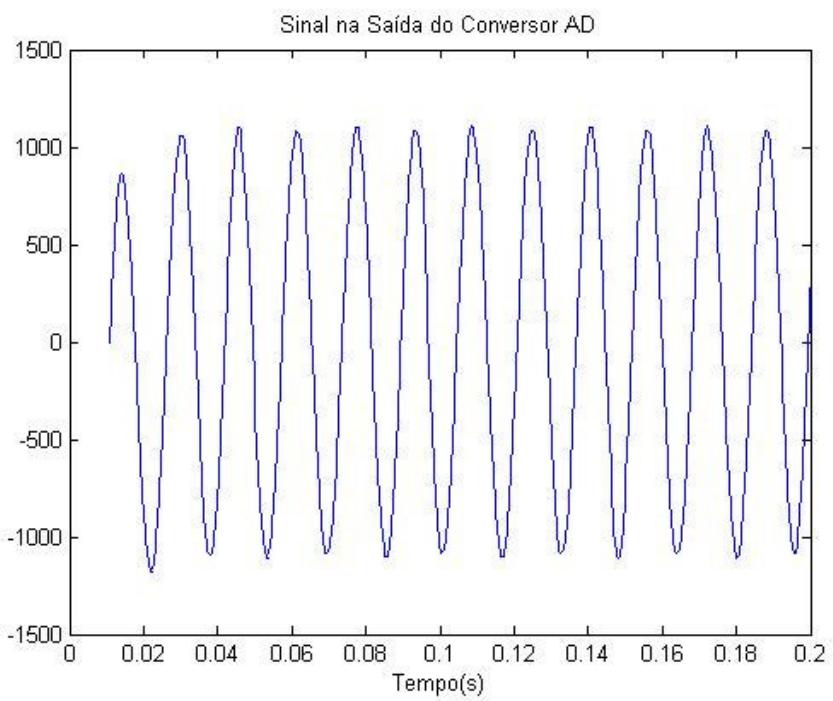

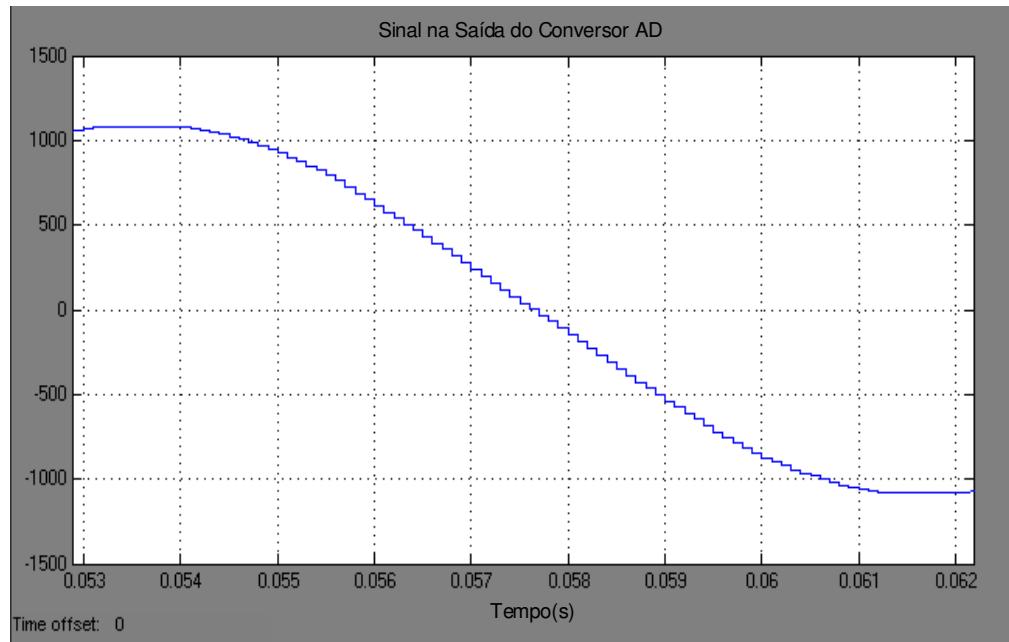

O sinal amostrado e quantizado presente na saída do conversor AD é ilustrado na figura 19. Observa-se que não é visualmente clara a quantização. Para vê-la recorreu-se a um “zoom” resultando na figura 20. Esse é o sinal de entrada do filtro passa-banda digital que será assunto da próxima subseção.

Figura 19: Sinal Amostrado e Quantizado.

Figura 20: “Zoom” do Sinal Amostrado e Quantizado.

## 2.2.4 Filtro Passa-Banda Digital

O projeto do filtro passa-banda digital é inteiramente baseado no projeto do filtro passa-banda analógico desenvolvido para o demodulador do ROP (Receptor de Onda Portadora) em trabalhos anteriores [2][5].

Naquele caso, o filtro projetado é melhor definido como filtro com amplificador, pois além de atenuar o sinal da fundamental (60Hz) e seus harmônicos, dá um ganho na freqüência da onda portadora de 270Hz. Esses parâmetros foram calculados visando atender às especificações de relação sinal-ruído na entrada do detector de tom (CI 567) que era utilizado para a detecção da portadora após a filtragem.

Sendo assim, para a correta detecção do sinal de 270Hz, constatou-se que seria necessário atender às seguintes especificações [5]:

- Ganho Mínimo na Banda de Passagem ( $G_P$ ) = 31dB

- Ganho Máximo na Banda de Rejeição ( $G_R$ ) = 8,7dB

- Atenuação Mínima entre a banda de passagem e a banda de rejeição:

$$A_a = G_P - G_R = 22,3 \text{ dB}$$

- Atenuação Máxima na banda de Passagem ( $A_p$ ) = 3dB

- Freqüências de corte inferior e superior:

$$f_2 = 264,6\text{Hz} \text{ e } f_4 = 275,4\text{Hz}$$

- Freqüências limite da banda de rejeição:

$$f_1 = 240\text{Hz} \text{ e } f_4 = 300\text{Hz}$$

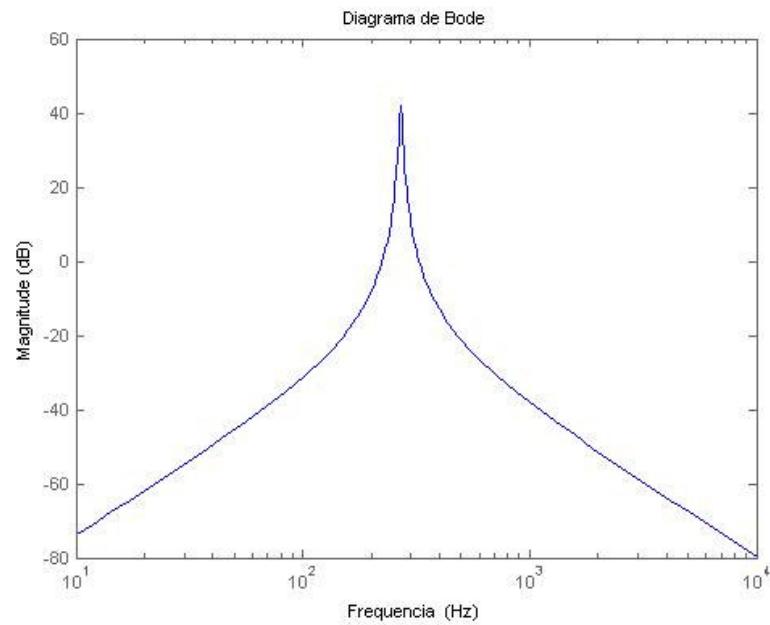

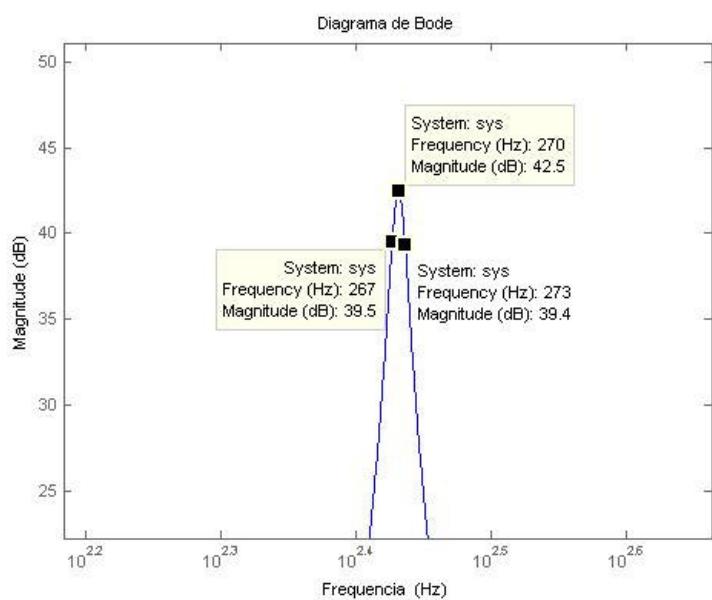

Buscando respeitar os critérios descritos anteriormente, foi desenvolvido, através da aproximação de Butterworth e implementado usando a configuração Delyiannis [5], um filtro passa-banda de quarta (4<sup>a</sup>) ordem. Sua função de transferência em blocos de segunda ordem é mostrada a seguir e sua resposta em freqüência é ilustrada na figura 21. A figura 22, apresenta um “zoom” do gráfico da figura 21 detalhando a freqüência central e as freqüências de corte inferior e superior.

$$H(s) = (4,157 \times 10^5) \times \frac{s}{s^2 + 54,56s + 2,902 \times 10^6} \times \frac{s}{s^2 + 54,56s + 2,860 \times 10^6}$$

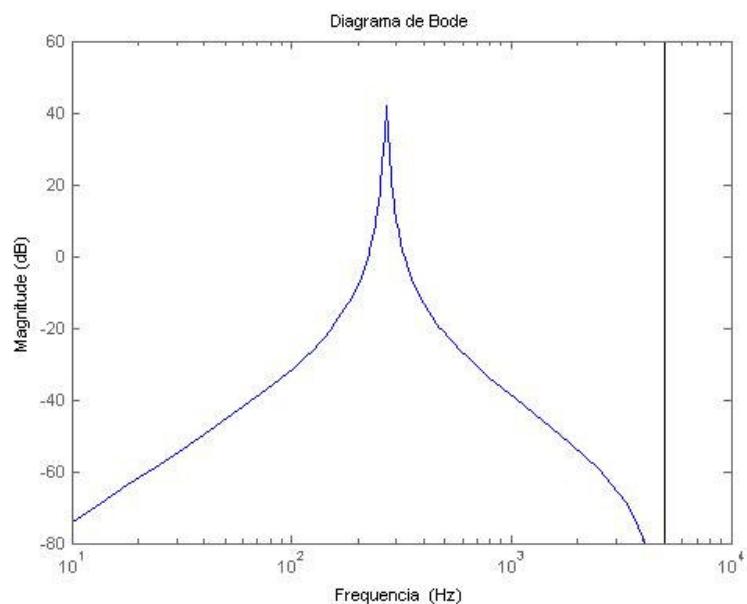

Figura 21: Resposta em Freqüência do Filtro Passa-Banda Analógico.

Figura 22: “Zoom” da Resposta em Freqüência do Filtro Passa-Banda Analógico.

No presente trabalho, optou-se pelo procedimento clássico para projeto de filtros digitais IIR (Infinite Impulse Response) que é, de posse do projeto do protótipo analógico descrito anteriormente, transformá-lo num filtro digital [10]. Para isso, foi escolhido o método da transformação bilinear. Considerado o método mais importante de obtenção dos coeficientes de um filtro IIR, o método bilinear garante o mapeamento de todo o semi-plano lateral esquerdo do plano  $s$  dentro do círculo unitário do plano  $z$ . Assim, um filtro analógico estável (com pólos localizados no semi-plano lateral esquerdo de  $s$ ) resulta em um filtro digital também estável (pólos localizados dentro do círculo unitário) [11]. Além disso, possui a vantagem de evitar o “aliasing” mantendo, com isso, as características da resposta de módulo da função de transferência no tempo contínuo ao gerar a função de transferência no tempo discreto [10].

A operação básica usada para converter um filtro analógico  $H(s)$  em seu equivalente digital é substituir  $s$  pela expressão:

$$s = k \frac{z-1}{z+1}, \text{ sendo } k=1 \text{ ou } \frac{2}{T} \text{ onde } T \text{ é o período de amostragem}$$

Neste trabalho, os coeficientes do filtro digital foram calculados usando a função “bilinear” do MATLAB (vide apêndice B). O resultado desta transformação foi o filtro digital com a seguinte função de transferência em blocos de segunda ordem:

$$H(z) = \frac{b_{01} + b_{21}z^{-2}}{1 + a_{11}z^{-1} + a_{21}z^{-2}} \times \frac{b_{02} + b_{22}z^{-2}}{1 + a_{12}z^{-1} + a_{22}z^{-2}} \text{ onde:}$$

$b_{01} = 20,628205321817553$

$b_{21} = -20,628205321817561$

$a_{11} = -1,965714801321117$

$a_{21} = 0,994585158131545$

$b_{02} = 4,962800177910070e-5$

$b_{22} = -4,962800177921170e-5$

$a_{12} = -1,966129097462778$

$a_{22} = 0,994584592445860$

A desvantagem deste método está na forma como são mapeadas as freqüências analógicas em freqüências digitais. Para altas freqüências a relação é altamente não-linear correspondendo a uma grande distorção da resposta na freqüência do filtro digital comparada com a do filtro analógico. Essa distorção na resposta de módulo é conhecida como efeito de warping (empenamento, em inglês) e pode ser compensado deslocando-se adequadamente (pré-distorcendo-se) as freqüências de interesse antes de se realizar a transformação.

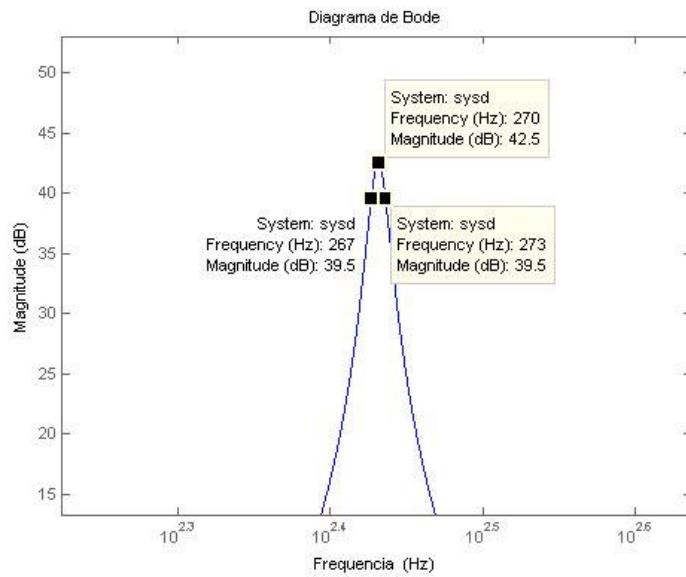

Neste sentido, o último argumento da função “bilinear” do MATLAB corresponde à freqüência de “pre-warping”. Isso significa que o sistema sofre uma pré-distorção de modo a garantir que as respostas em freqüência antes e depois da transformação sejam iguais naquela freqüência. No caso, a freqüência de “pre-warping” escolhida foi a freqüência central (270Hz). A resposta em freqüência do filtro digital pode ser vista na figura 23. A figura 24, por sua vez, é um “zoom” do gráfico da figura 23 detalhando a freqüência central e as freqüências de corte inferior e superior.

Figura 23: Resposta em Freqüência do Filtro Passa-Banda Digital.

Figura 24: "Zoom" da Resposta em Freqüência do Filtro Passa-Banda Digital.

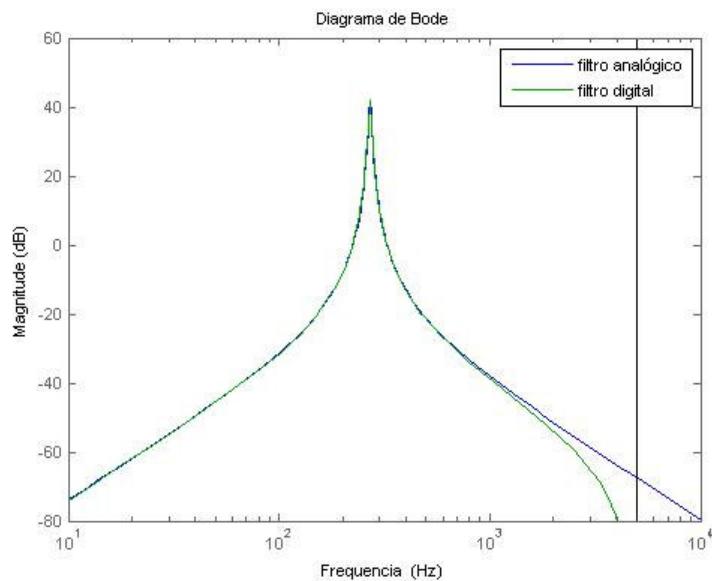

A fim de verificar o efeito de warping, apresentam-se as respostas em freqüência dos dois filtros em um mesmo gráfico. Observa-se que as duas funções se encontram superpostas nas freqüências de interesse (freqüências central, de corte inferior e superior) e com isso, pode-se concluir que a distorção causada pela transformação bilinear não prejudica o projeto.

Figura 25: Respostas em Freqüência dos Filtros Passa-Banda Analógico e Digital.

Uma alternativa seria o reprojeto do filtro, levando-se em consideração inclusive a possibilidade de se utilizar outra aproximação que não a de Butterworth ou até mesmo a possibilidade de ser um filtro com topologia FIR (resposta ao impulso finita). Os estudos sobre as alternativas de projeto serão destinadas a trabalhos futuros.

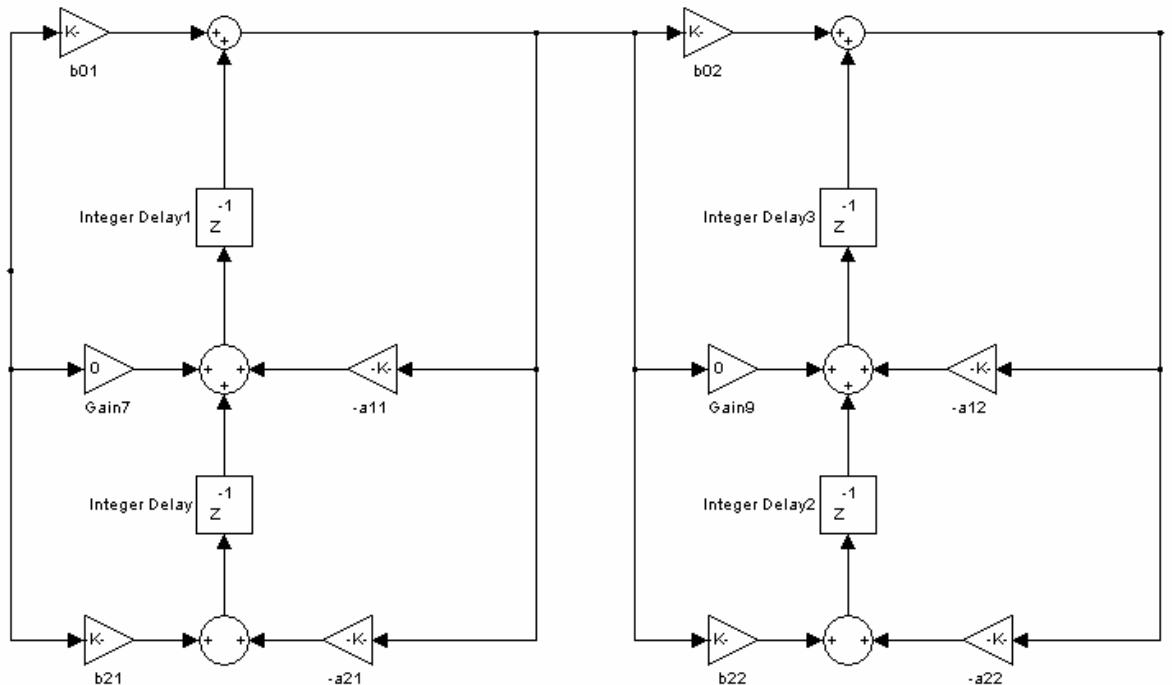

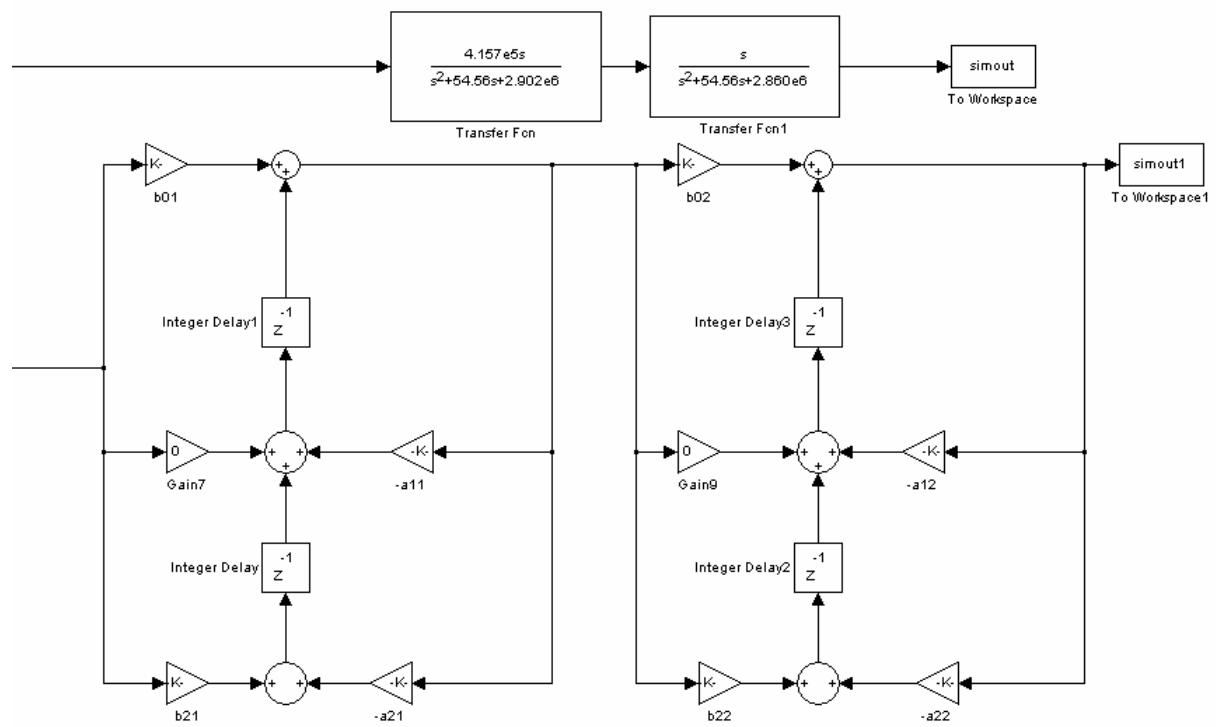

No Simulink, o filtro passa-banda digital que, como visto, é de 4<sup>a</sup> ordem, foi subdividido em duas seções de 2<sup>a</sup> ordem conectadas em cascata. Essa implementação foi escolhida porque além de estar de acordo com aquela utilizada no projeto base [5], também é considerada usual para o caso de filtros de ordem superior a 3 a fim de diminuir a sensibilidade a efeitos de precisão finita [11]. A estrutura simulada é mostrada na figura 26.

Figura 26: Implementação do Filtro Passa-Banda Digital no Simulink.

Como pode ser observado na figura 26, optou-se pela estrutura na forma canônica transposta uma vez que a forma direta é muito sensível a efeitos de precisão finita [11]. Outro aspecto é que, por ser canônica, sua implementação possui número mínimo de elementos de atraso [11]. Outras estruturas menos suscetíveis à saturação e mais otimizadas são possíveis,

mas não serão abordadas neste projeto podendo, assim, ter seu desempenho explorado em trabalhos futuros.

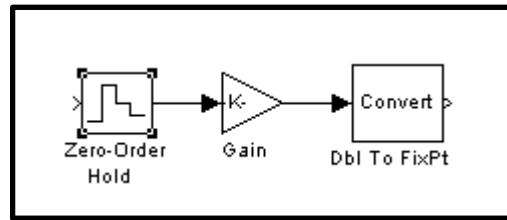

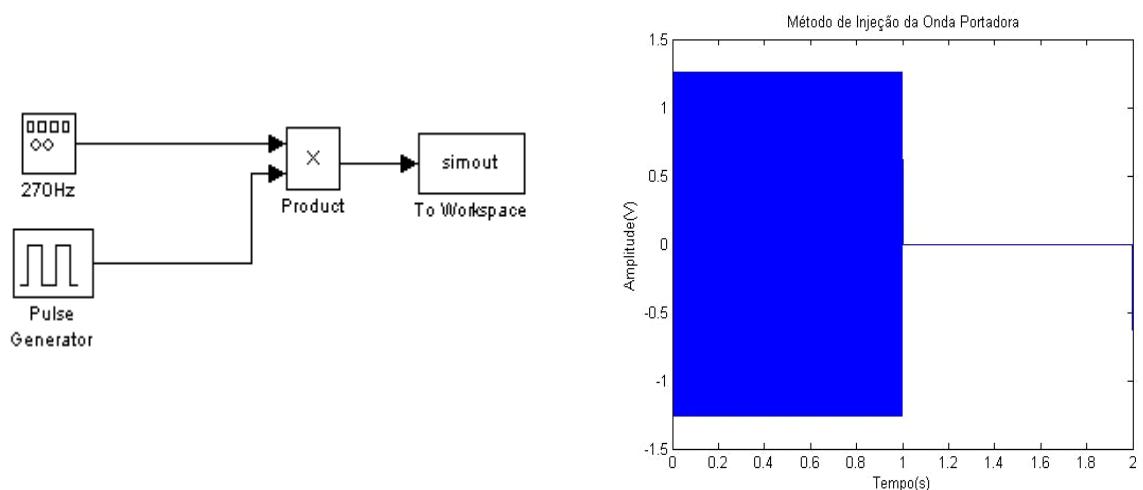

Para verificar o desempenho do filtro digital, foram feitas simulações aplicando o sinal descrito na seção 2.2.3 na entrada do demodulador. Os níveis da fundamental e da onda portadora foram mantidos, a única diferença é que esta última foi pré-multiplicada por uma onda quadrada de 1V de pico e dois segundos de período. Isso faz com que, definindo-se dois segundos como tempo de simulação, por exemplo, a onda portadora esteja presente no primeiro segundo e ausente no segundo. A figura 27 ilustra o método de injeção da portadora descrito.

Figura 27: Método de Injeção da Onda Portadora.

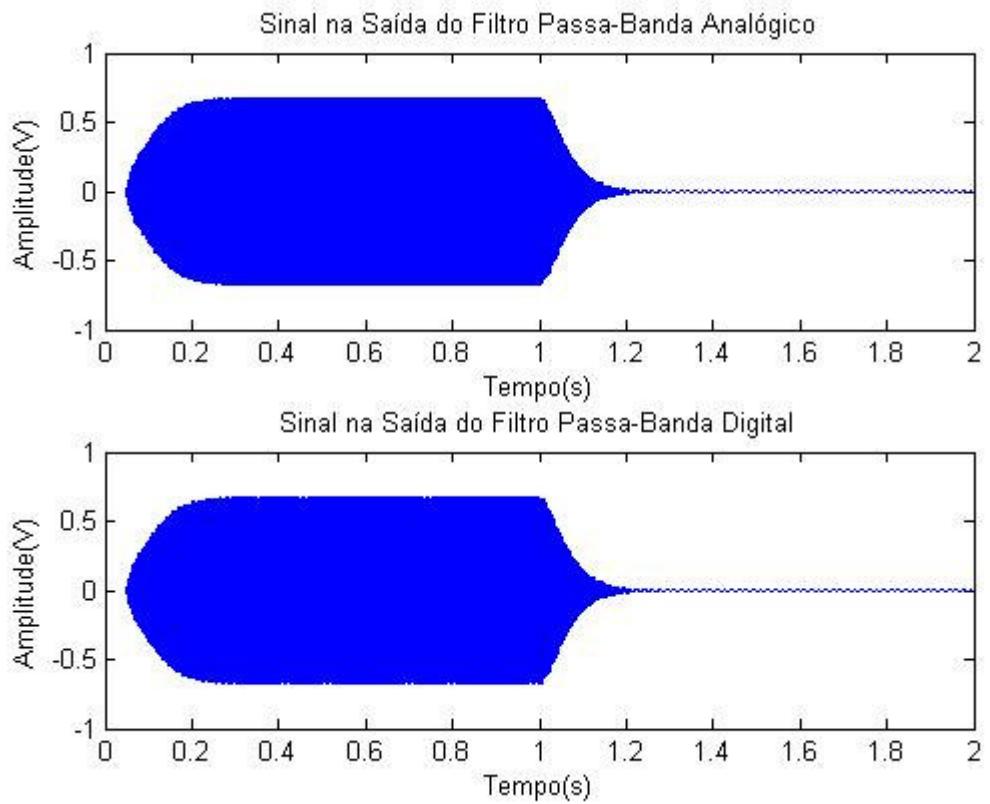

A validação do filtro digital foi feita comparando sua saída com aquela que se deseja obter, ou seja, com a do filtro analógico. Para isso, utilizou-se um conversor AD ideal, representado somente pelo bloco “Zero Order Hold” com taxa de amostragem de 10kHz. O esquemático da simulação e os gráficos com as saídas dos filtros analógico e digital são mostrados nas figuras 28 e 29, respectivamente.

Figura 28: Comparação entre os Filtros Passa-Banda Analógico e Digital no Simulink.

Figura 29: Sinais nas Saídas dos Filtros Passa-Banda Analógico e Digital.

Observa-se, na figura 29, que as saídas dos filtros são semelhantes comprovando o que já foi mostrado na figura 25. Entretanto, o filtro digital calculado através da função “bilinear” do MATLAB utiliza aritmética em ponto flutuante. Seu projeto em ponto fixo é o tema da próxima subseção.

## 2.2.5 Aritmética em Ponto-Fixo

Em geral, os processadores de ponto fixo são menos dispendiosos que os já preparados para realizar operações em ponto flutuante. Esta é a principal motivação para a decisão de projetar o demodulador no MATLAB usando a aritmética de ponto fixo.

O primeiro passo neste sentido foi dado no projeto do conversor AD quando se utilizou o bloco “Convert” que converte o valor das amostras de ponto flutuante para números inteiros sinalizados de 12 bits. Isto significa que as amostras só podem assumir valores inteiros presentes no intervalo [-2048 2047], simulando, assim, um conversor AD de 12 bits.

O sinal agora amostrado e quantizado entra no filtro passa-banda. Estipulou-se que o DSP teria uma arquitetura de 16 bits, isto é, as operações de multiplicação e adição utilizadas na implementação do filtro possuem como operandos e resultados números inteiros sinalizados, cujos valores se encontram no intervalo [-32768 32767]. Esses limites correspondem a  $-2^{15}$  e  $2^{15} - 1$  respectivamente sendo o 16º bit destinado à representação do sinal. O desrespeito desses limites caracteriza o erro de overflow (saturação) que deve ser evitado.

Assim, o projeto do filtro digital em ponto fixo no MATLAB é baseado em dois procedimentos. O primeiro é garantir que os operandos das multiplicações (coeficientes) sejam números inteiros, sinalizados cujo valor está dentro do intervalo descrito. O segundo é garantir que o resultado das operações de multiplicação e adição tenham essas mesmas características.

Os blocos de ganho (“Gain”), adição e multiplicação utilizados para implementar o filtro passa-banda digital no Simulink possuem suporte para aritmética de ponto fixo. Com isso, para limitar o resultado das operações de adição e multiplicação a números sinalizados

em ponto fixo de 16 bits, é necessário ajustar na própria janela de diálogo de cada um desses blocos o campo referente ao formato da sua saída (“Output data type”) para “sfix(16)” onde o “s” é de sinalizado, o “fix” é de ponto fixo e o “16” corresponde ao tamanho de 16 bits. A definição de que se tratam de valores inteiros é feita com o campo referente ao escalamento da saída (“Output Scaling Value”) igual a  $2^0$ . Isso significa que o ponto binário está localizado mais à direita do número caracterizando, assim, o formato inteiro.

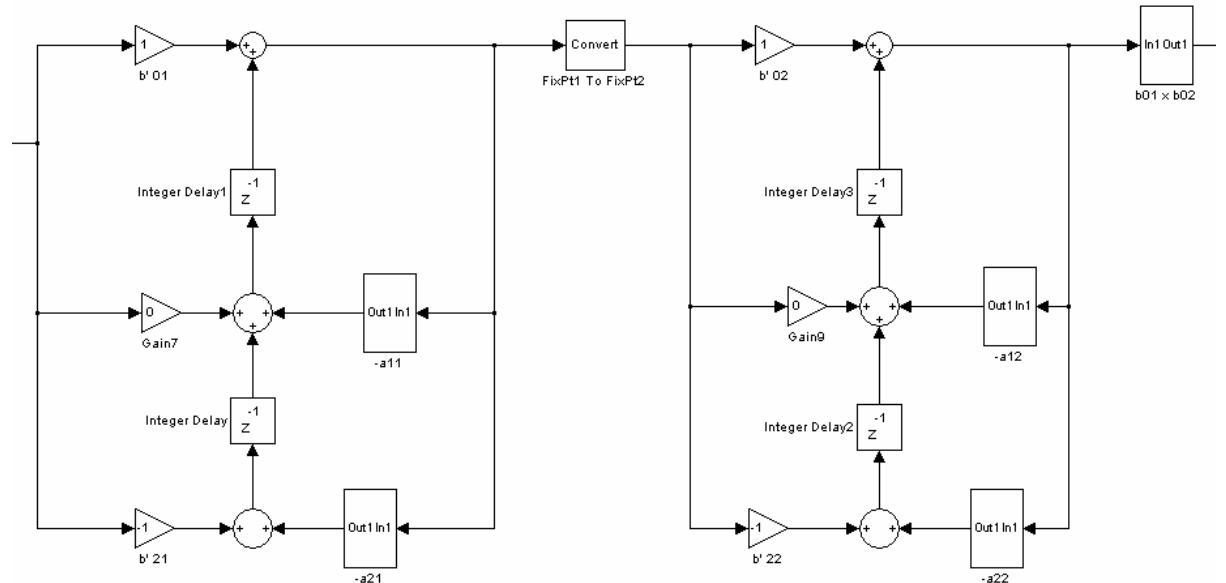

No processo de escalamento dos coeficientes, optou-se por normalizar os valores dos coeficientes dos numeradores dos dois estágios [11]. Como  $b_{01} \cong -b_{21}$ , para o 1º estágio, dividiu-se os coeficientes por  $b_{01}$  obtendo-se  $b'_{01} = 1$  e  $b'_{21} = -1$ . Já para o 2º estágio, como  $b_{02} \cong -b_{22}$ , dividiu-se os coeficientes por  $b_{02}$  obtendo-se  $b'_{02} = 1$  e  $b'_{22} = -1$ . A saída do filtro é, então, multiplicada por  $b_{01} \times b_{02}$  após o filtro compensando a normalização feita. Esse procedimento foi realizado já com vistas a uma possível implementação futura em DSPs porque reduz o número de multiplicações a serem realizadas. A estrutura do filtro em ponto fixo é ilustrada na figura 30.

Figura 30: Implementação do Filtro Passa-Banda Digital em Ponto Fixo no Simulink.

Para escalar os coeficientes do denominador do 1º estágio (subsistemas correspondentes a  $-a_{11}$  e  $-a_{21}$ ) multiplica-se o valor do coeficiente em ponto flutuante por uma potência de dois de modo que o resultado da operação seja inferior ao máximo valor

possível em 16 bits. A saída do bloco dessa multiplicação deve estar ajustada para ser do formato inteiro sinalizado de 16 bits (“sfixed(16)”). O cálculo da potência de dois a ser multiplicada pode ser feito empiricamente, mas existe, no MATLAB, a função “*fi*” que tendo como argumento o valor do coeficiente em ponto flutuante retorna o valor da potência de dois necessária para acomodar o coeficiente em 16 bits. Esse coeficiente, então, passa a ser um número inteiro sinalizado de 16 bits que multiplicado pela saída do 1º estágio (filtro recursivo) que também é um número inteiro sinalizado de 16 bits resulta em um número com as mesmas características diferindo apenas no tamanho que passa a caber somente em 32 bits. Esta operação pode ser realizada em DSP através do recurso chamado de “*type cast*” e equivale a ter, durante o processamento, variáveis de 32 bits. No ambiente “Simulink”, basta permitir que a saída do segundo bloco de multiplicação seja “sfixed(32)”. Entretanto, como o processador é 16 de bits, os bits menos significativos devem ser descartados para que o número volte a caber em 16 bits. Tal procedimento que em software é realizado através de um comando de “*shift*” para direita é feito no Simulink com uma multiplicação por um número fracionário cujo denominador é igual à potência de dois pela qual o coeficiente em ponto flutuante fora multiplicado. Neste caso, a saída do bloco de multiplicação é novamente ajustada para “sfixed(16)”.

As figuras 31 e 32 mostram o interior dos dois subsistemas que representam os coeficientes do denominador do 1º estágio.

Figura 31: Interior do Subsistema correspondente ao coeficiente  $-a_{11}$ .

Figura 32: Interior do Subsistema correspondente ao coeficiente  $-a_{21}$ .

O projeto do filtro em ponto fixo foi feito com o auxílio de comparações de seus sinais internos com os sinais internos do filtro em ponto flutuante que é tido como modelo (figura 33). Com isso, verificou-se que os sinais internos resultantes das operações de adição e multiplicação do 2º estágio do filtro eram muito altos alcançando valores que ultrapassam 16 bits. Este é o caso, por exemplo, do sinal identificado como W na figura 33 e mostrado em detalhe na figura 34.

Figura 33: Os Filtros Passa-Banda Digitais em Ponto Fixo e em Ponto Flutuante.

Figura 34: Sinal Interno W.

Sendo assim, todas as operações referentes ao 2º estágio do filtro têm como operandos e resultados números inteiros sinalizados de 32 bits. O bloco “Convert” localizado na entrada deste estágio é o responsável pela conversão da saída do 1º estágio em um número de 32 bits mantendo as demais características (os números continuam sendo inteiros e sinalizados). Nesse sentido, os blocos de ganho, soma e multiplicação que, como já mencionado, possuem suporte para aritmética em ponto fixo, têm o campo da janela de diálogo referente ao formato da saída (“Output data type”) ajustado para “sfix(32)”. Em DSP, isso pode ser feito via software através de um “type cast”. Assim, para o caso do segundo estágio do filtro, as variáveis de entrada e saída dos somadores passarão a ter 32 bits. Isto implica que em um processador de 16 bits, tenha-se que fazer a previsão para isto, criando-se duas variáveis de 16 bits correspondentes a uma variável de 32 bits.

Para escalar os coeficientes do denominador do 2º estágio também se multiplica o valor do coeficiente em ponto flutuante por uma potência de dois de modo que o resultado dessa operação ainda caiba em 16 bits. A saída do bloco dessa multiplicação deve estar ajustada para ser do formato inteiro sinalizado de 16 bits (“sfixed(16)”). Esse coeficiente inteiro sinalizado de 16 bits é, então, multiplicado pela saída do 2º estágio (filtro recursivo). Entretanto, como já foi observado, este sinal na saída do filtro possui um valor alto (32 bits). Logo, antes de ser multiplicado pelo coeficiente, o sinal deve ser multiplicado por uma fração cujo denominador é uma potência de dois de modo que os bits menos significativos são descartados e este número passe a ocupar 16 bits. O valor deste denominador pode ser calculado tanto usando a função “fi” do MATLAB como empiricamente. Números que correspondem a potências de dois são escolhidos para realizar o escalamento pois operações de divisão e multiplicação por esses números são facilmente implementadas em software através de comandos de “shift” para direita ou para esquerda respectivamente.

Assim, dois números de 16 bits (o coeficiente e o sinal na saída do filtro devidamente escalados) são multiplicados resultando em um número de 32 bits. Pode-se observar que mesmo com os números em 32 bits, as multiplicações do 2º estágio do filtro são realizadas em 16 bits, o que implica que para este tipo de operação (a mais demorada) não haverá uma perda de velocidade. Este número de 32 bits resultante é, então, multiplicado por uma fração cujo denominador é uma potência de dois fazendo com que seus bits menos significativos fossem descartados. O valor do denominador desta nova fração é o que falta para compensar o escalamento do coeficiente. Apesar da saída do último bloco de multiplicação ser um número de 16 bits, o campo da janela de diálogo referente ao formato da saída deste bloco (“Output Data Type”) é ajustado para “sfixed(32)”. Isso acontece pois este sinal será somado a outro de 32 bits (o sinal de saída do bloco de ganho “-1” no caso do coeficiente  $a_{22}$  e a saída do bloco “Integer Delay2” no caso do coeficiente  $a_{12}$ ) e em uma operação de adição a base dos operandos deve ser a mesma.

As figuras 35 e 36 mostram o interior dos dois subsistemas que representam os coeficientes do denominador do 2º estágio.

Figura 35: Interior do Subsistema correspondente ao coeficiente  $-a_{12}$ .

Figura 36: Interior do Subsistema correspondente ao coeficiente  $-a_{22}$ .

A saída do 2º estágio do filtro é a entrada do bloco “ $b_01x b_02$ ” que compensa a normalização feita nos coeficientes dos numeradores dos dois estágios do filtro digital. Esse subsistema é semelhante àquele utilizado para representar os coeficientes do denominador do

2º estágio. A constante correspondente a  $b_{01}x b_{02}$  é multiplicada por uma potência de dois de modo que o resultado seja um número inteiro sinalizado de 16 bits. Esse número é então multiplicado pelo sinal de entrada do subsistema que por possuir 32 bits deve ser previamente multiplicado por uma fração cujo denominador é uma potência de dois tendo seus bits menos significativos descartados para que passe a ocupar 16 bits. A multiplicação desses dois números inteiros sinalizados de 16 bits resulta em um número de 32 bits. Este último, por sua vez, tem seus bits menos significativos descartados passando a ter 16 bits através da multiplicação por uma fração cujo denominador é a potência de dois que falta para compensar o escalamento da constante  $b_{01}x b_{02}$ . Neste caso, a saída deste último bloco de multiplicação possui formato “sfix(16)”.

O interior do subsistema em questão (bloco “b01 x b02”) é mostrado na figura 37.

Figura 37: Interior do Subsistema “b01 x b02”.

A ação de descartar os bits menos significativos para adequar o sinal ao tamanho correspondente a 16 bits implica uma perda de precisão. Dependendo do nível, essa perda pode ocasionar um erro de arredondamento (“Roundoff error”) que faz com que o sistema não mais atenda suas especificações originais prejudicando o projeto do filtro digital. Deste

modo, são plotados os sinais de saída do filtro digital em ponto fixo e em ponto flutuante (figura 38) assim como as respectivas funções de transferência (figura 39).

Figura 38: Saídas dos Filtros Passa-Banda em Ponto Fixo e em Ponto Flutuante.

Figura 39: Respostas em Freqüência dos Filtros em Ponto Flutuante e em Ponto Fixo.

Observa-se que a perda de precisão não inviabiliza o projeto uma vez que as duas saídas são semelhantes e as respostas em freqüências se encontram superpostas.

A princípio, a partir do projeto original, que continha um circuito de PLL analógico, neste projeto utilizar-se-ia uma PLL digital. No entanto, optou-se pela implementação de um detector de amplitude em substituição à PLL. Esta decisão está baseada na expectativa de que o nível do sinal de 270Hz possa ser alto se comparado ao nível do ruído que o filtro apresenta em sua saída quando a onda portadora está ausente. Outro critério seria que o uso do detector de amplitude seria mais simples em um DSP que um PLL digital. Este é o assunto da próxima subseção.

## 2.2.6 Detector de Amplitude

Neste projeto, utiliza-se um detector de pico na saída do filtro para auxiliar na identificação da onda portadora. O seu objetivo é verificar a presença ou ausência do sinal de 270Hz. Apresenta-se o esquema proposto para o detector de pico na figura a seguir.

Figura 40: Diagrama de Blocos do Detector de Amplitude.

A saída do filtro é retificada e em seguida aplica-se um filtro passa-baixas. Trata-se de um filtro FIR (Finite Impulse Response) média móvel ou “moving average” que calcula a média de um determinado número de amostras do sinal, número este que pode ser definido pelo projetista. Se o número de amostras for inferior ao período de 270Hz, não se obtém a filtragem correta. Desta forma o número de amostras tem que ser superior a 10000/270 ou 37,03. Como esta divisão não é exata, não se consegue obter uma amostragem sincronizada e haverá erros. Para minimizá-los optou-se por amostrar um número bem maior de amostras, 128 amostras.

O resultado da saída do filtro é aplicado a um somador que faz a integração do nível DC filtrado. Há um gerador de pulsos que “reseta” o somador para zero periodicamente. Um passo de amostragem antes do “reset” do integrador, o sinal de saída do mesmo é amostrado por um amostrador. Em seguida o sinal amostrado é comparado com um nível pré-estabelecido (“NÍVEL DE CALIBRAÇÃO”). A idéia de colocar um somador “resetável” e amostrado tem por finalidade tornar o algoritmo mais robusto do que um simples detector de

nível. Com este procedimento, um “spike” na entrada do integrador poderia ser filtrado, o que não ocorreria com um detector simples. Produz-se então um sinal onde o nível lógico “1” corresponde à presença da onda portadora enquanto o nível lógico “0” corresponde à ausência da onda portadora. Concluindo-se, assim, o projeto do demodulador.

Apresenta-se na figura 41, o esquema do detector de amplitude no ambiente “Simulink” e a figura 42 mostra os sinais nas saídas dos blocos descritos.

Figura 41: Esquemático do Detector de Amplitude no Simulink.

Figura 42: Sinais de Saída dos Blocos que compõe o Detector de Amplitude.

Observa-se, pelo sinal de saída do comparador, que o sistema apresenta um atraso de aproximadamente 0,5 segundo. Otimizações do algoritmo no sentido de diminuir esse atraso são destinadas a trabalhos futuros.

### 2.2.7 Interpretador

O sinal injetado pelo TOP atinge todos os consumidores ligados ao transformador de distribuição e consequentemente todos os receptores. Com isso, para garantir que a informação da leitura do consumo atingirá o receptor específico a que se destina e evitar que ruídos na rede elétrica sejam interpretados como onda portadora erroneamente, um protocolo de comunicação foi estabelecido em trabalhos anteriores [5][12]. Este protocolo é ilustrado na figura a seguir [12]:

Figura 43: Protocolo de Comunicação utilizado.

Observa-se que há um “start bit”, composto por três períodos de 0,5 segundo com o sinal “on” e um período de 0,5 segundo com o sinal “off”. O restante dos dados segue a convenção mostrada na figura 44:

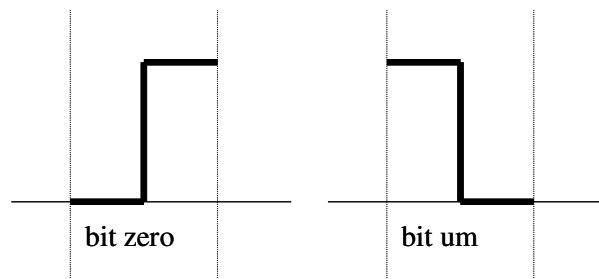

Figura 44: Bits “Zero” e “Um” de acordo com o Protocolo.

O bit “zero” é identificado por um período de 0,5 segundo com o sinal “off” e um período de 0,5 segundo com o sinal “on”, ou seja, é caracterizado por uma transição positiva. O bit “um” é identificado por um período de 0,5 segundo com o sinal “on” e um período de 0,5 segundo com o sinal “off”, ou seja, é caracterizado por uma transição negativa. Isso garante mais robustez à comunicação PLC utilizada.

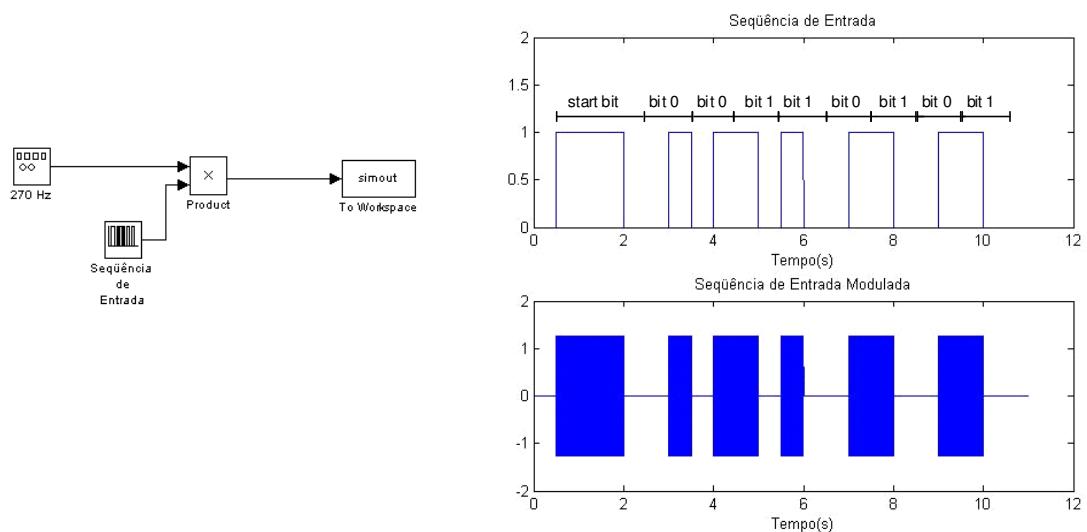

O protocolo em questão também foi utilizado neste projeto, tendo sua implementação no ambiente “Simulink” ilustrada na figura 45.

Figura 45: Injeção da Onda Portadora segundo o Protocolo.

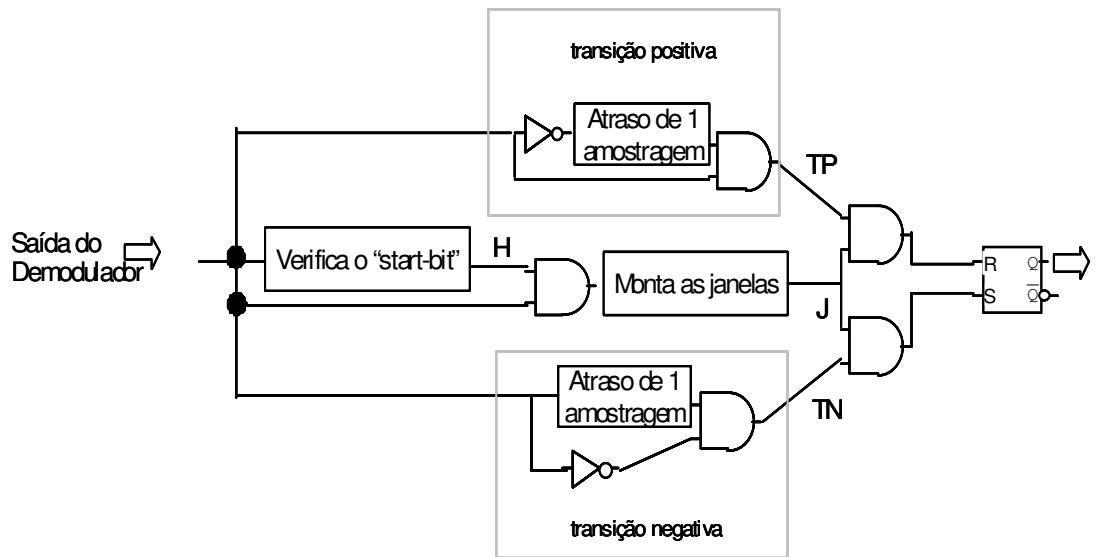

Assim, após o demodulador, há a necessidade de um circuito interpretador. Este circuito avalia os níveis lógicos de saída do demodulador de acordo com o protocolo pré-estabelecido.

Apresenta-se a seguir o diagrama de blocos simplificado do interpretador feito no “Simulink”.

Figura 46: Diagrama do Interpretador.

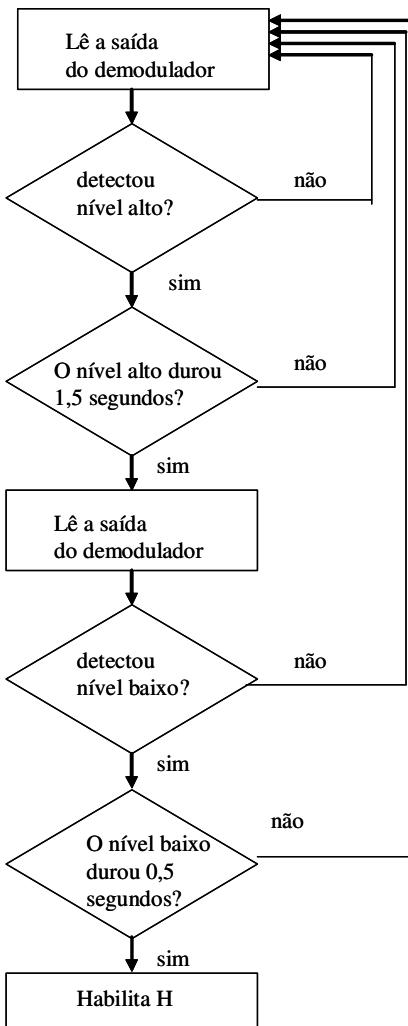

A primeira função do interpretador é verificar se há um “start bit” presente. Isto é feito através de um algoritmo implementado no MATLAB usando-se blocos lógicos, tais como portas lógicas, contadores, “flip-flops” e comparadores. A lógica desta função está exposta na figura 47:

Figura 47: Algoritmo de Detecção do “Start Bit”.

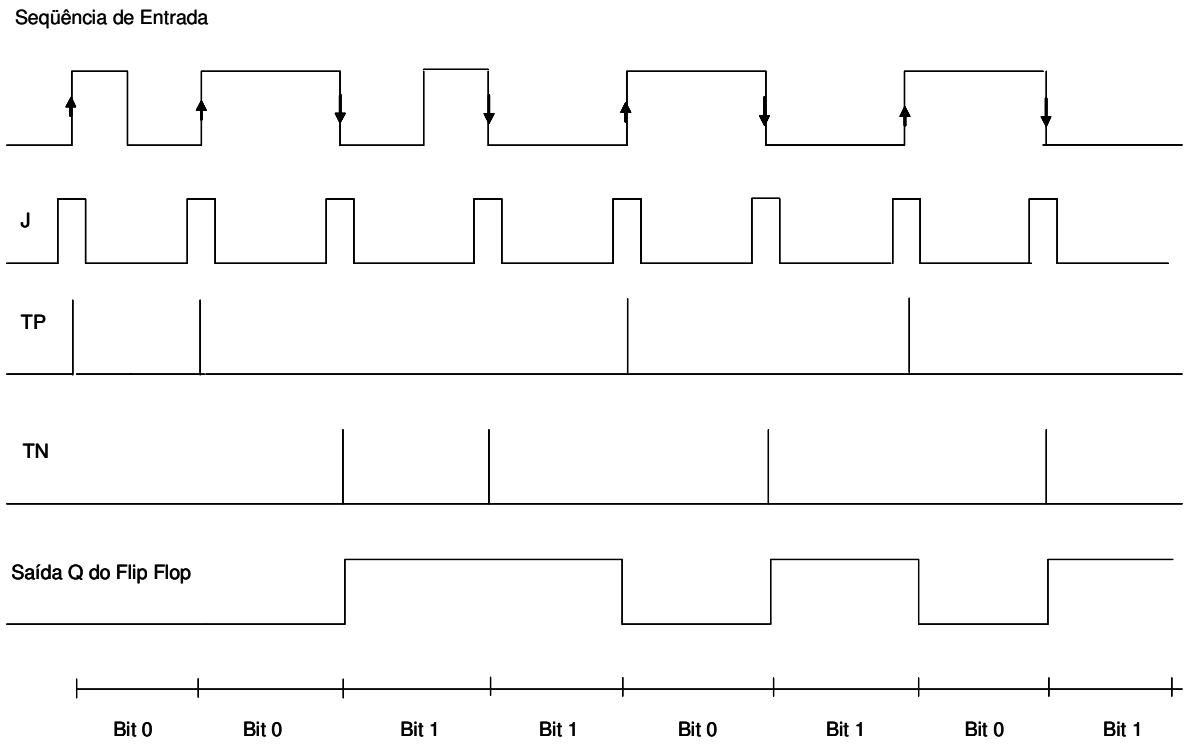

A detecção dos demais bits se realiza através da montagem de três sinais, os sinais “TP”, “TN” e “J”, como mostrado na figura do interpretador (figura 46). O sinal TP indica transição positiva do sinal de entrada correspondente ao bit “0”. O sinal TN indica transição negativa do sinal de entrada correspondente ao bit “1”. O sinal J habilita a detecção dos bits, como mostrado na figura a seguir:

Figura 48: Detecção da Informação.

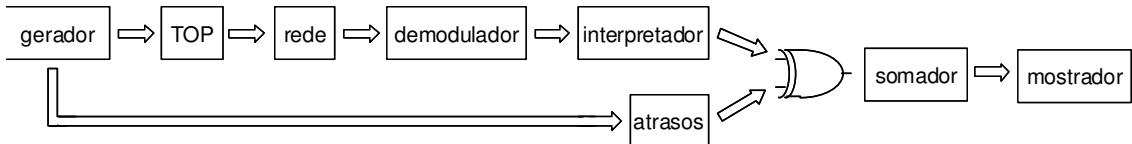

Finalmente, para verificar se o interpretador funciona corretamente, adotou-se uma lógica de comparar com o sinal original esperado em termos de palavra binária através de uma porta “XOR”, como mostrado na figura a seguir. Esta comparação é somada e colocada em um mostrador para se verificar facilmente qualquer diferença entre os sinais. Há atrasos relacionados à propagação do sinal na rede e principalmente dentro do demodulador (filtro passa-baixas, integrador) e eles devem ser considerados na comparação.

Figura 49: Sinal Exteriorizado para o Mostrador.

Na realidade, o interpretador seria implementado através de linguagem de programação, dentro de um DSP. Em trabalhos anteriores [5][12], a interpretação é feita por “software” utilizando um microcontrolador.

O algoritmo apresentado aqui pode ser realizado de outras formas, como, por exemplo, através da contagem do tempo “on” e “off” de um bit aliada a uma avaliação mais robusta do sinal de forma a contornar eventuais erros menores que poderiam afetar o desempenho. Investigações sobre as diferentes possibilidades de implementação do algoritmo de interpretação do protocolo assim como avaliações de desempenho são deixadas como sugestão para estudos futuros.

# Capítulo 3:

## Ensaio e Resultados

Neste capítulo, apresentam-se os ensaios realizados com o algoritmo proposto e os resultados. O objetivo é verificar seu desempenho considerando os dois principais problemas inerentes à rede elétrica: harmônicos e transitórios, já que estes poderão afetar o bom funcionamento do sistema projetado na prática.

De posse dos resultados preliminares, é possível definir um nível de calibração para o detector de amplitude e estabelecer as condições de contorno para as quais o modelo ainda funciona de maneira satisfatória.

### 3.1 Ensaio com Harmônicos

Esta seção tratará dos ensaios feitos considerando os harmônicos da fundamental de 60Hz. Usou-se como caso base de harmônicos aquele definido no trabalho [2] que se baseia na norma IEC nº 62054-11 [7]. Verifica-se ainda o desempenho do algoritmo proposto sob condições harmônicas mais elevadas ainda que o caso base a fim de identificar o limite para correta detecção da onda portadora.

#### 3.1.1 Caso Padrão

O caso padrão, como já foi mencionado, corresponde ao estabelecido pela norma IEC. Esta define os harmônicos a serem considerados e seus respectivos níveis em porcentagens do nível da componente fundamental da rede elétrica como mostrado na figura 4.

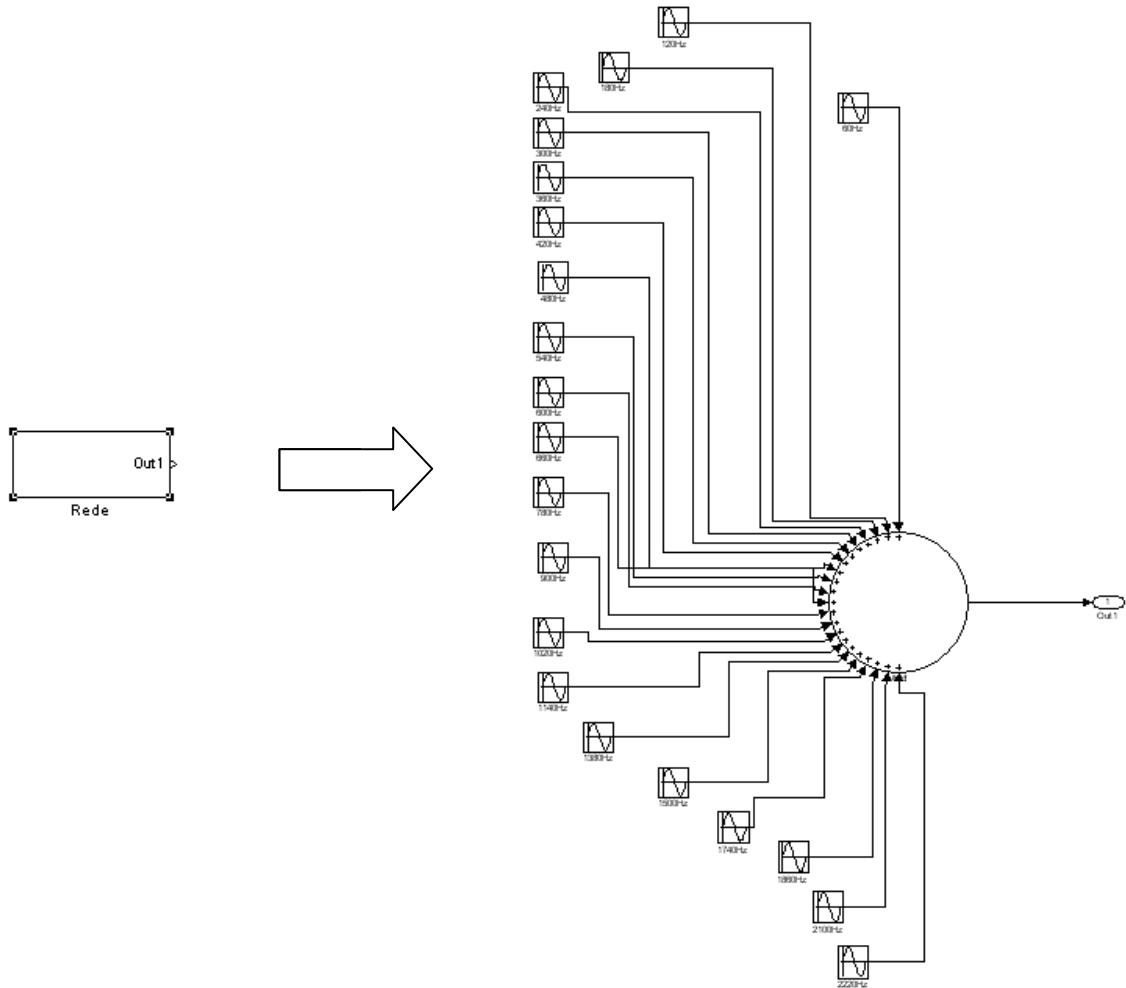

No ambiente “Simulink”, a rede elétrica prevista pela norma IEC [7] é representada por um subsistema contendo uma soma de sinais senoidais correspondendo à freqüência fundamental (60Hz) e seus harmônicos. Apresenta-se na figura 50 a implementação deste arranjo.

Figura 50: Rede Elétrica de acordo com a Norma IEC.

Também pela norma IEC, a onda portadora injetada possui amplitude igual a cerca de 1% da amplitude da fundamental. Em trabalhos anteriores [2][5], verificou-se uma atenuação máxima de 3dB entre o transmissor de onda portadora e o receptor de onda portadora na frequência de 270Hz devido a perdas na linha de distribuição. Para simular este efeito no “Simulink” multiplica-se o valor da onda quadrada do TOP (1,79V) por 0,7 resultando numa onda quadrada de aproximadamente 1,25V.

O esquemático do sinal de entrada do demodulador para os ensaios de harmônicos é mostrado a seguir:

Figura 51: Esquemático do Sinal de Entrada para Ensaios com Harmônicos.

Com esses níveis de harmônicos e onda portadora obtém-se uma relação sinal ruído de 0,09803 ou -40,17 dB. Este valor considera o sinal de 60Hz da fundamental como ruído para o receptor.

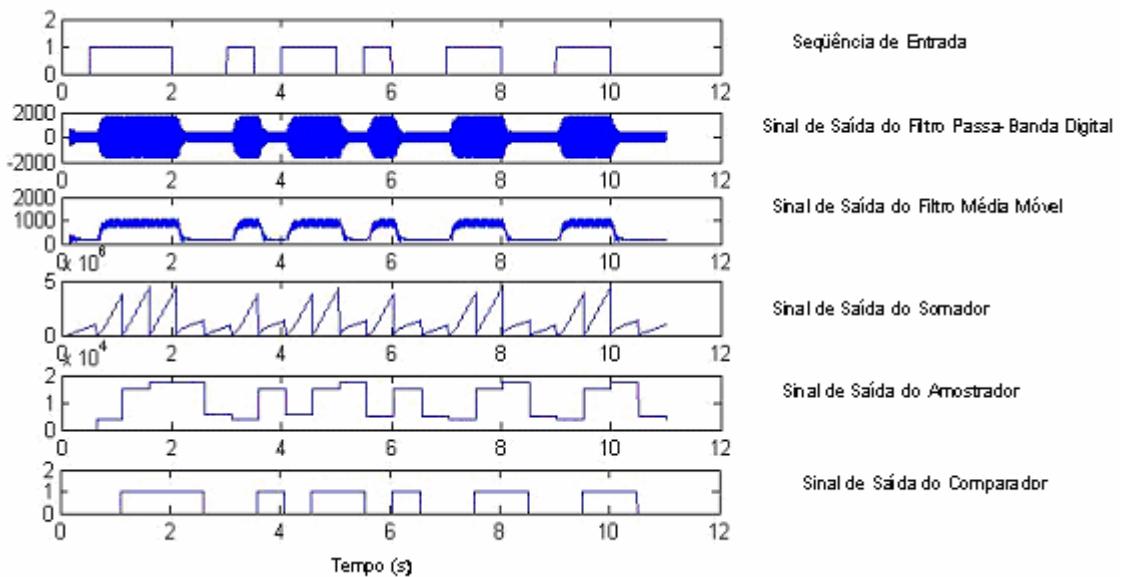

Para esta situação, ajusta-se o nível de calibração, explicado na seção 2.2.6 do capítulo anterior, para 10000 conseguindo, assim, detectar a onda portadora.

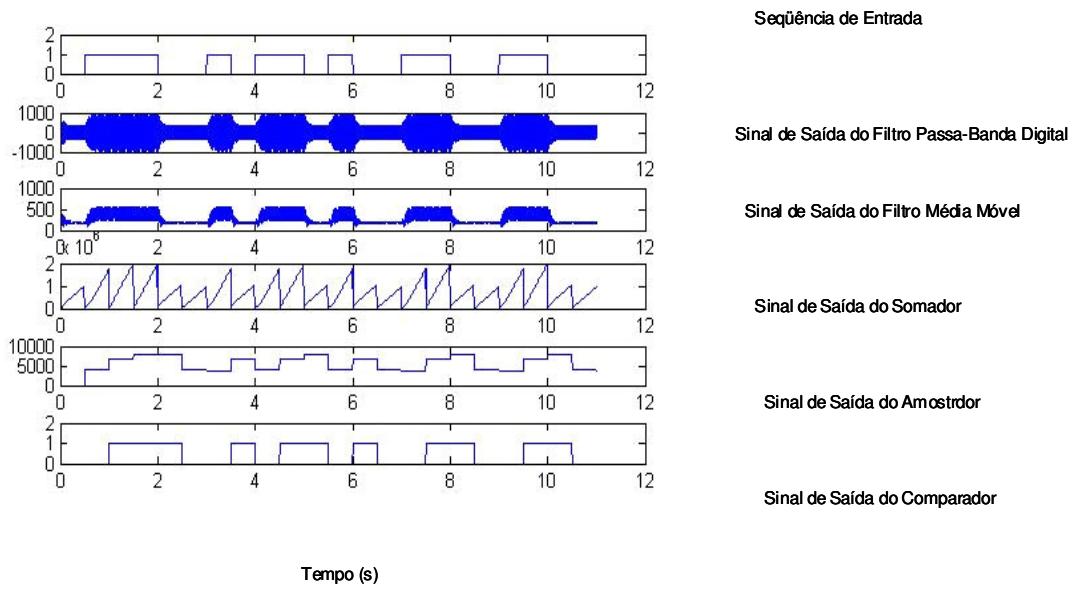

Os sinais correspondentes à seqüência de entrada, às saídas dos filtros passa-banda digital e FIR média móvel, do somador, do amostrador e do comparador são mostrados a seguir.

Figura 52: Sinais do Caso Padrão do Ensaio de Harmônicos e Calibração 10000.

Como se pode observar, a seqüência de entrada, salvo um atraso de 0,5 segundo, é igual àquela na saída do comparador. Como resultado, o display do interpretador acusou “zero” comprovando a validade do algoritmo para este caso.

### 3.1.2 Casos com Atenuação da Portadora

Com o objetivo de verificar o desempenho do algoritmo proposto sob condições harmônicas mais elevadas do que a própria norma, diminuiu-se o nível da onda portadora. Atenuou-se o valor da amplitude da onda portadora de 28% com relação ao valor do ensaio anterior. Isto corresponde a reduzir o valor original do sinal injetado pelo TOP à metade. A relação sinal ruído incluindo-se a fundamental de 60Hz é de 0,007002 ou -43dB. Com isso, mantendo-se a calibração em 10000 tem-se:

Figura 53: Sinais do Caso com Atenuação da Portadora de 50% e Calibração 10000.

Observa-se que ainda é possível discriminar o sinal da portadora de maneira satisfatória.

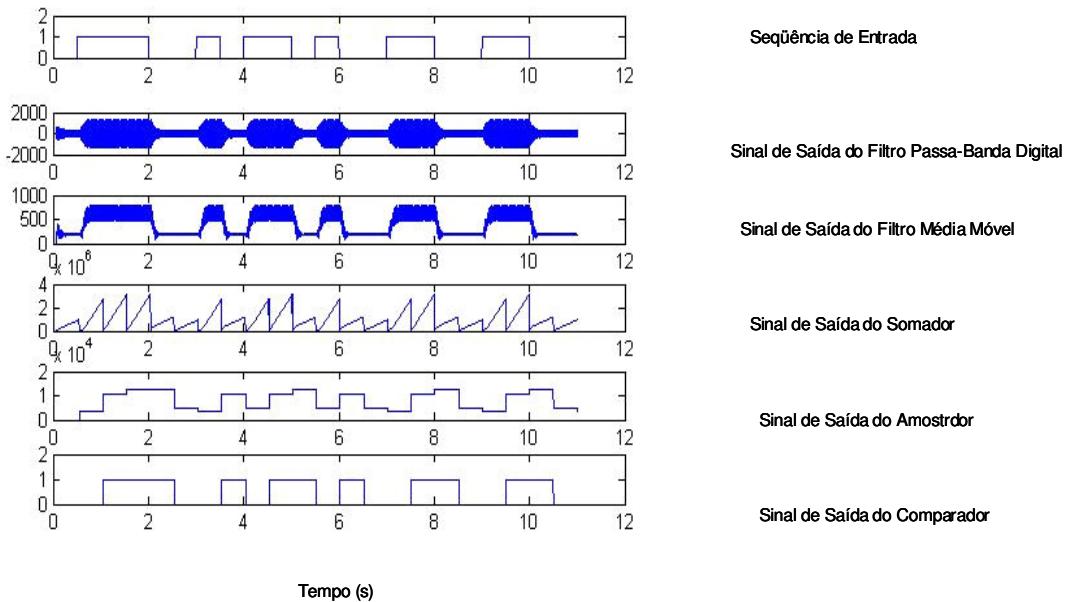

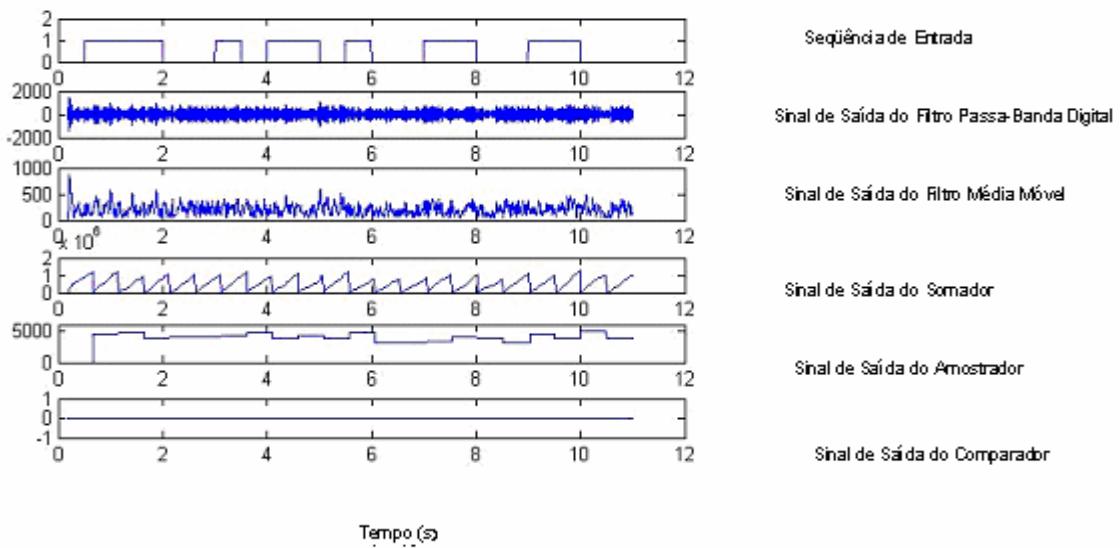

Prosseguiram-se os ensaios reduzindo-se o nível da onda portadora para 30% do valor original do TOP. Este caso corresponde a uma relação sinal ruído de 0,0042 ou -47,5 dB.

Mantendo-se o nível de calibração em 10000, o algoritmo não foi capaz de discriminar a onda portadora. Esta situação é ilustrada pela figura 54.

Figura 54: Sinais do Caso com Atenuação da Portadora de 70% e Calibração 10000.

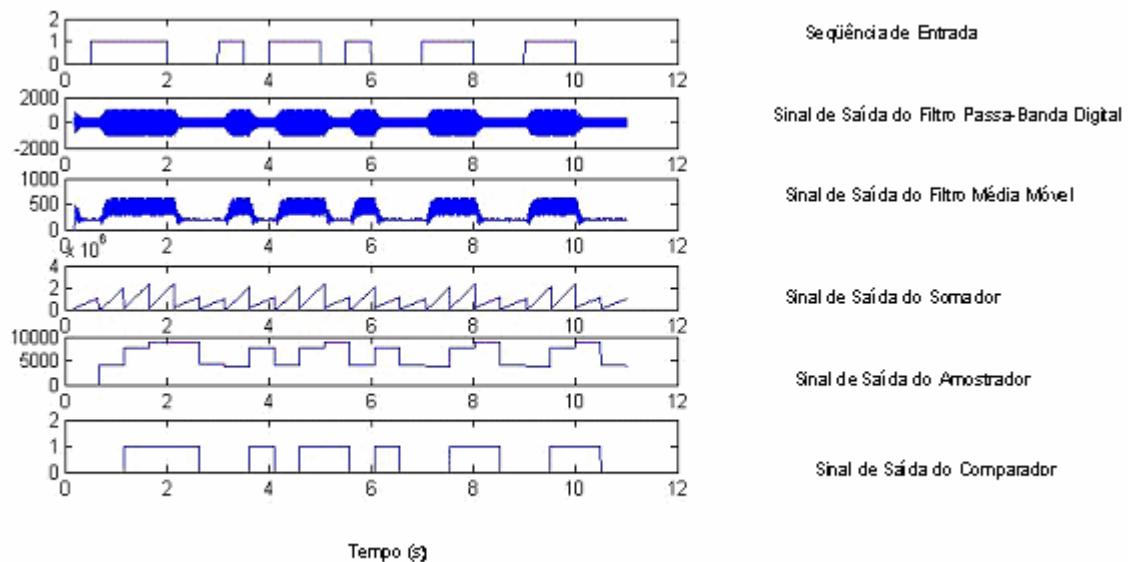

Observa-se que já não se consegue recuperar a seqüência de entrada. Entretanto, a saída do filtro passa-banda digital ainda discrimina a onda portadora. Portanto, uma mudança de nível de calibração poderá ser suficiente. Assim, mantendo a razão sinal ruído, alterou-se a calibração para 5000 obtendo-se o resultado apresentado na figura 55:

Figura 55: Sinais do Caso com Atenuação da Portadora de 70% e Calibração 5000.

Para este caso, a mudança do nível de calibração solucionou o problema da falta de detecção da onda portadora. No entanto, verificou-se em seguida, que com o nível usado nesta situação, de 5000, o algoritmo não funcionou para os casos base e o de redução de 50% da onda portadora em relação ao sinal injetado pelo TOP. Isto porque ele representou um nível muito baixo para estes dois casos já vistos, havendo um erro de detecção nestas condições. Isto evidencia o fato de que, para trabalhos futuros, poder-se-ia trabalhar com um algoritmo de níveis adaptativos às condições do sinal de entrada.

### 3.1.3 Caso com Aumento dos Harmônicos

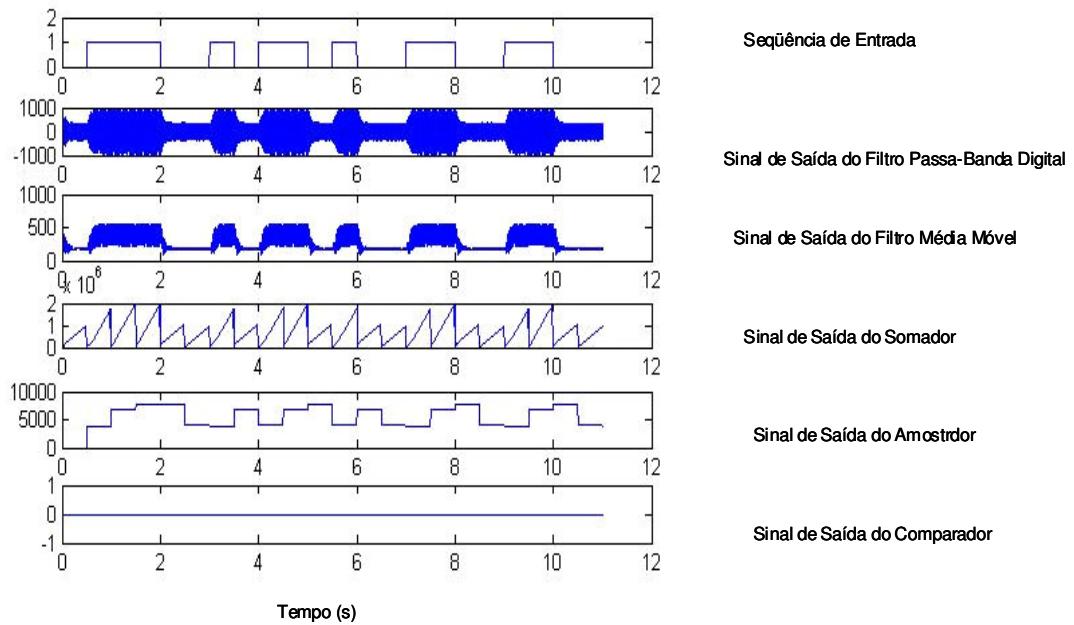

Retornando ao caso padrão, com a onda portadora de nível igual a 1% da amplitude da fundamental e considerando uma atenuação de 3 dB, aumentou-se o nível dos harmônicos vizinhos(240Hz e 300Hz) em duas vezes, pois estes são tidos como os harmônicos mais prejudiciais ao bom funcionamento do demodulador uma vez que estão mais próximos da freqüência da onda portadora. Com a relação sinal ruído de 0,009706 ou -40,26 dB, os resultados são apresentados na figura 56.

Figura 56: Sinais do Caso com Aumento dos Harmônicos e Calibração 5000.

Neste caso, percebeu-se que houve saturação ou “overflow” do algoritmo, no 1º estágio do filtro. Na tentativa de corrigir este erro devido à precisão finita, optou-se por modificar o conversor estipulando 2V como fundo de escala. Com o bloco de ganho utilizado na modelagem do AD passando a ser “2048/2”, obter-se-ia uma redução no nível do sinal de entrada do filtro e espera-se que este ajuste seja suficiente para recuperar a onda portadora. Assim, como o sinal de entrada foi reduzido pela metade, o nível de calibração adotado também teve seu valor reduzido à metade passando a ser igual a 5000. A figura a seguir mostra os sinais para a condição descrita.

Figura 57: Sinais com Aumento dos Harmônicos e Compensação no Conversor AD.

Pela imagem, conclui-se que a compensação feita no conversor AD fez com que o demodulador recuperasse a onda portadora com sucesso.

Aplicando-se a compensação para os ensaios considerando atenuação da portadora, verifica-se que o caso padrão e o caso com redução de 50% apresentam resultados satisfatórios com esta calibração de 5000. O único ensaio em que o demodulador nesta configuração ainda falha é naquele com atenuação da onda da portadora de 70% em relação ao sinal original do TOP. Assim, este representa, a princípio, o caso limite verificado através das simulações em regime.

Entretanto, para validar o modelo de forma definitiva é necessário verificar seu desempenho considerando transitório. Este é o tema da próxima subseção.

## 3.2 Ensaio em Transitório

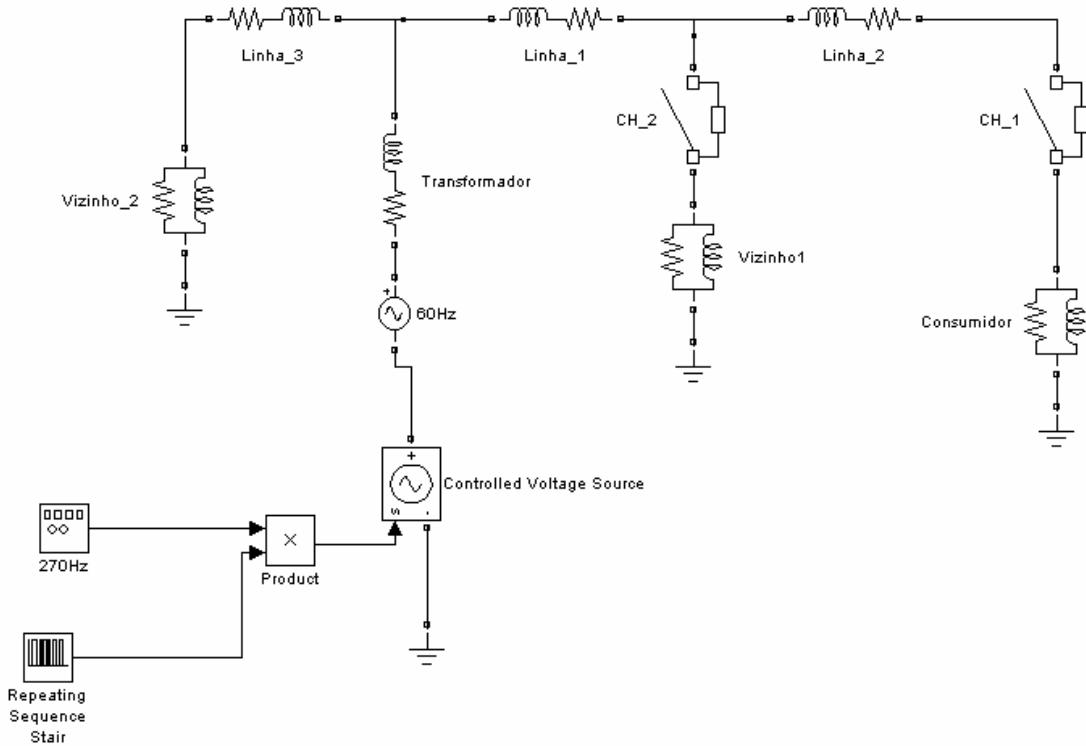

### 3.2.1 Modelo da Rede de Distribuição

Para os ensaios de transitório, foi montado no ambiente “Simulink” um modelo de rede de distribuição de energia em baixa tensão. Esta rede está baseada em uma linha típica de distribuição de uma concessionária de energia elétrica[8][2]. Levando-se em consideração que as freqüências de interesse são inferiores a 1kHz com foco em 270Hz, optou-se por simplificar a rede típica, eliminando-se as capacitâncias distribuídas do modelo original. Assim, modelou-se a linha com uma resistência em série com uma indutância, levando-se em consideração padrões típicos de linhas de distribuição, conforme mencionado em [2][8]. Sua configuração é apresentada a seguir:

- Comprimento total da linha – 580 metros;

- Número de consumidores – 30 (trinta);

- Distância aproximada entre consumidores – 20 metros;

- Transformador de alimentação trifásico, de potência nominal de 150KVA.

O modelo será monofásico considerando que o transformador está montado no meio da linha e eqüidistante de dois consumidores vizinhos como ilustrado na figura 58. O uso de

modelos mais detalhados levando-se em consideração a influência entre fases será destinado a trabalhos futuros.

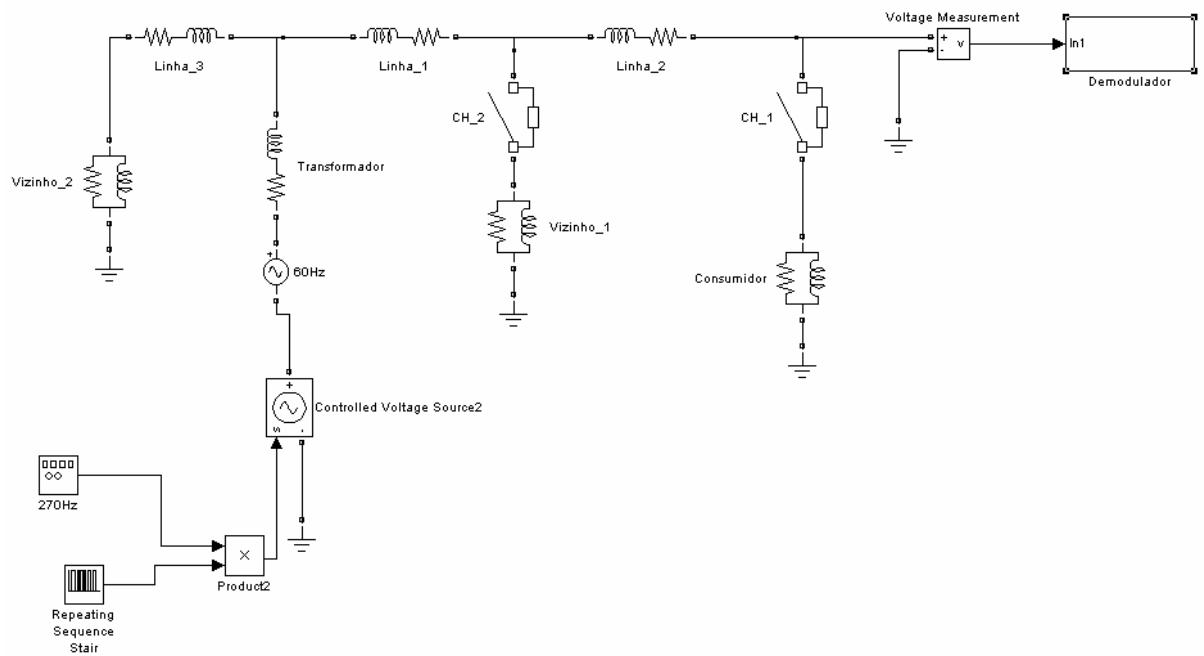

Figura 58: Modelo de Rede de Distribuição Implementado em Simulink.

O bloco “Controlled Voltage Source” faz a interface entre os blocos do “Simulink” padrão e os blocos destinados à simulação de circuitos (“SimPowerSystems”).

Como a simulação em questão modela as perdas da linha, o sinal de 270Hz injetado é uma onda quadrada de nível correspondente a 1% do nível da fundamental da rede, ou seja, não se considera a atenuação máxima de 3dB já na definição dos parâmetros do bloco como foi feito para os ensaios de harmônicos. Essa injeção está, mais uma vez, de acordo com o protocolo de comunicação pré-estabelecido [2][5]. A portadora é, então, superposta à fundamental de 60Hz.

A impedância do transformador de distribuição está baseada em [2][8] e corresponde a um circuito série resistor e indutor de valores: 4,1mΩ e 27,89uH respectivamente.

A impedância da linha é modelada de modo que cada 20 metros de linha são modelados por um resistor de 7,53mΩ e um indutor de 32,8uH. Com relação aos trabalhos [2] e [8], retirou-se a capacidade paralela porque considerou-se que para baixas freqüências o efeito causado pela impedância do capacitor usualmente presente em paralelo com a série

resistor indutor em modelos de linha de transmissão é pouco significante. Uma modelagem mais exata da linha de distribuição será considerada em trabalhos futuros.

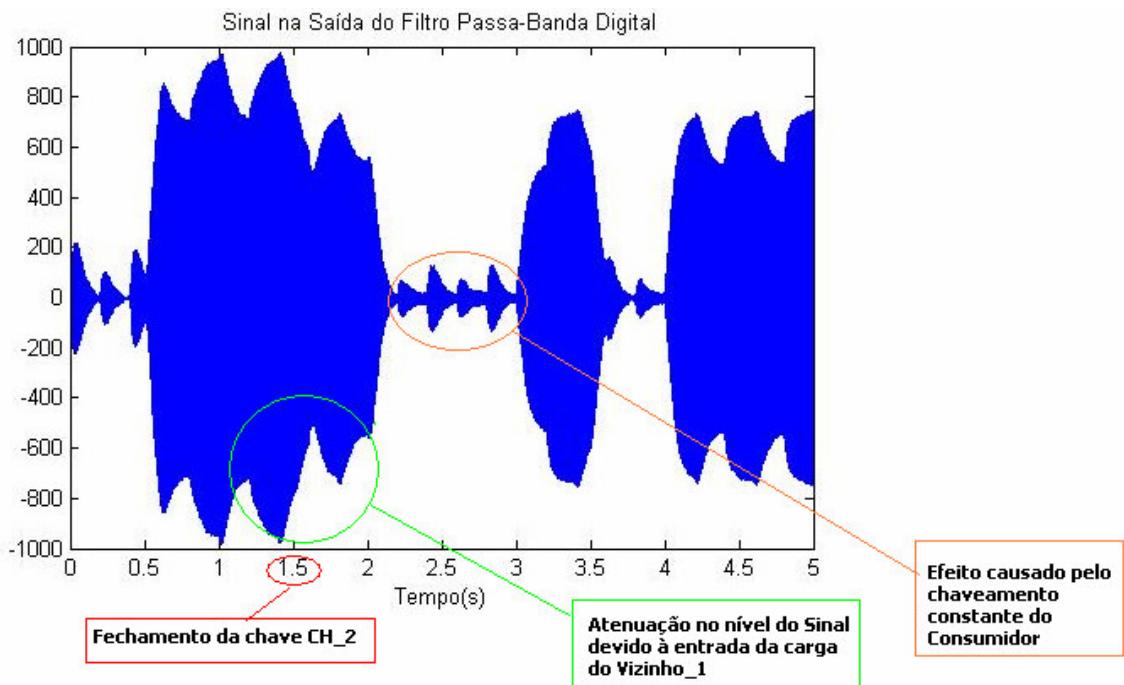

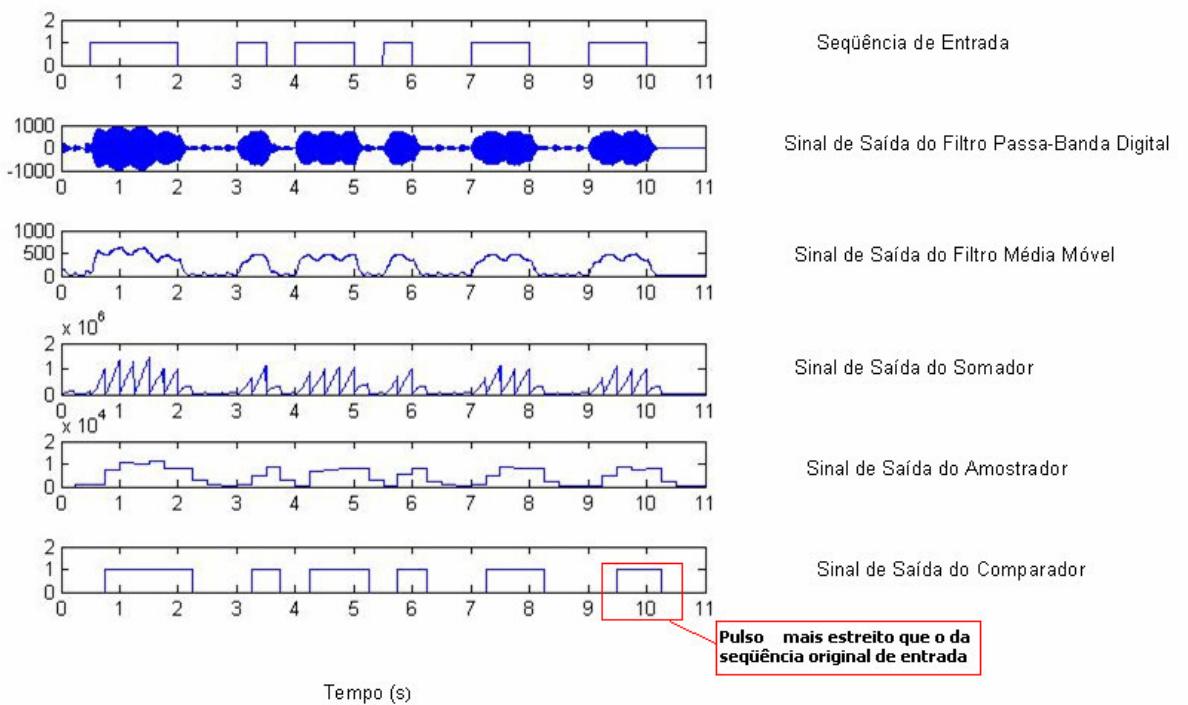

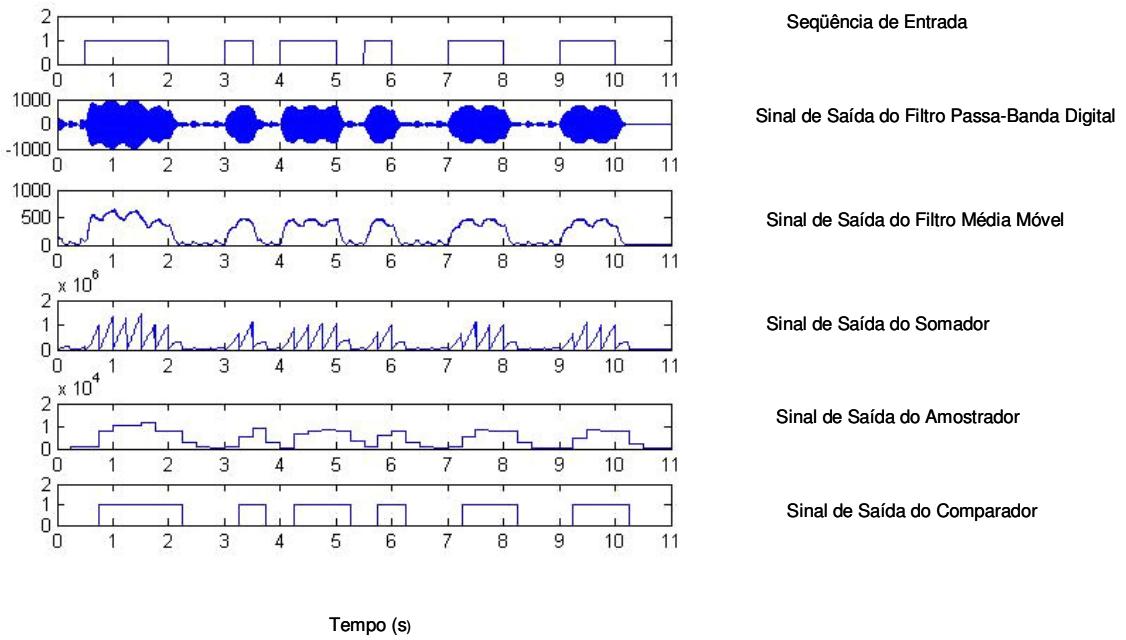

O consumidor localizado na extremidade direita da linha é identificado como “Consumidor” e o seu vizinho mais próximo está representado como “Vizinho”. Portanto, “Linha\_2” possui comprimento igual a 20 metros, é modelada por uma série resistor indutor de, respectivamente,  $7,53\text{m}\Omega$  e um indutor de  $32,8\text{uH}$  como já foi visto. A “Linha\_1” representa uma distância de linha igual à metade do comprimento total da rede (290m) menos os vinte metros finais. Assim, são 270 metros de linha o que corresponde à “13,5” séries de resistores e indutores como aquela já mencionada. Concentrando-as em uma única de  $R = 101,655\text{ m}\Omega$  ( $13,5 \times 7,53\text{ m}\Omega$ ) e  $L = 422,8\text{uH}$  ( $13,5 \times 32,8\text{ uH}$ ) obtém-se o modelo da “Linha\_1”. O consumidor identificado como “Vizinho\_2”, por sua vez, é aquele localizado na extremidade esquerda da linha de distribuição. Com isso, o comprimento modelado por “Linha\_3” corresponde à metade dos 580 metros o que equivale à “14,5” séries de resistores e indutores modeladas por uma única série de  $R = 109,185\text{ m}\Omega$  ( $14,5 \times 7,53\text{ m}\Omega$ ) e  $L = 475,6\text{ uH}$  ( $14,5 \times 32,8\text{uH}$ ).